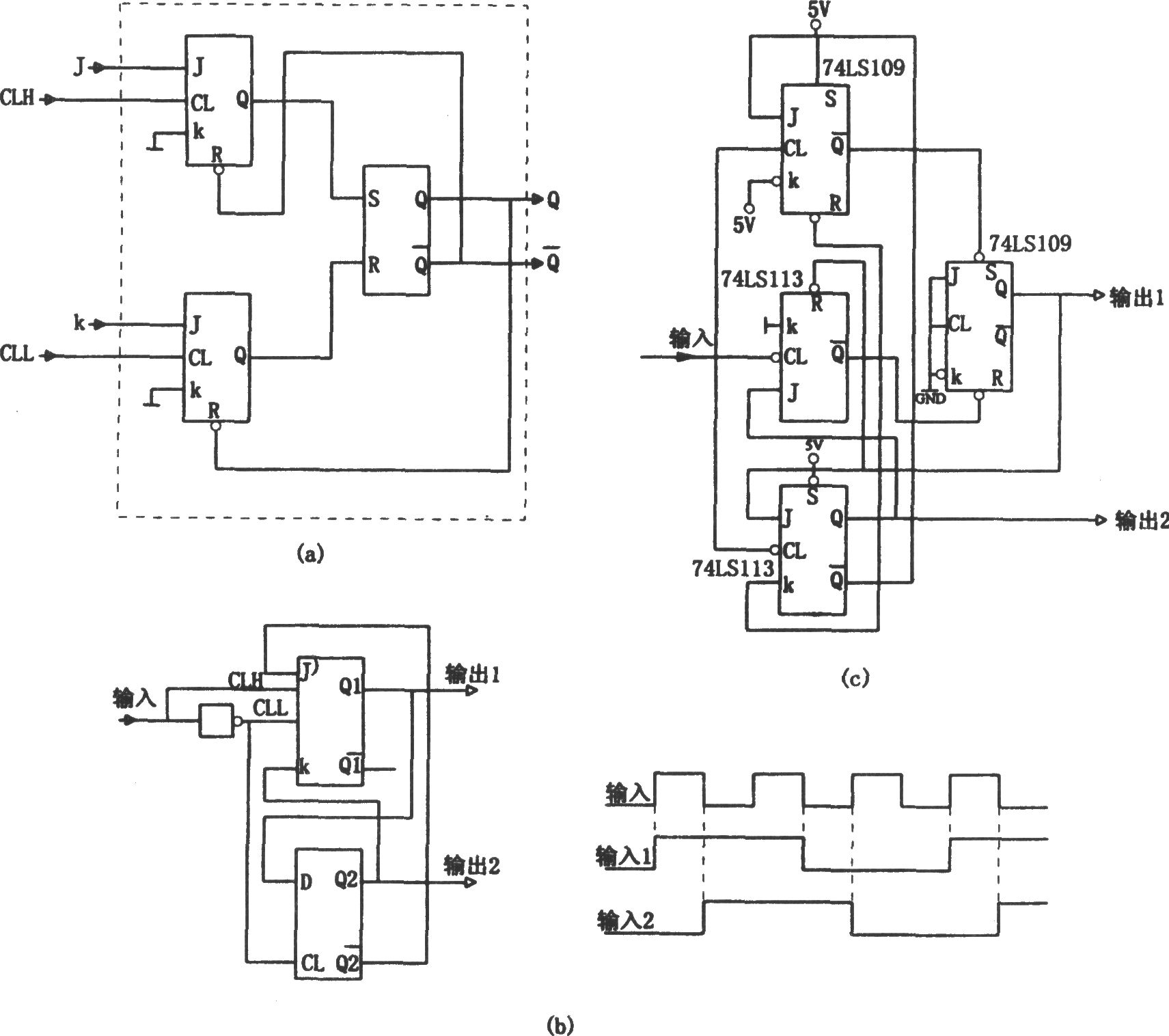

对称输出的三分频电路(74LS109、74LS113)

发布时间:2011-4-28 10:14

发布者:电路图分享

如图所示为对称输出的三分频电路。在一般的利用常规计数器对数字脉冲进行奇数分频时.即使输入是对称信号,输出也得不到占空比为50%的分频输出,其原因是内部触发器采用的是统一的上升沿(或下降沿)进行触发。为了解决此问题,可以利用一个J和K分别由不同时钟沿触发的JK触发器,如图(a)所示。该电路内部由两个JK触发器和一个RS触发器构成,其等效J端由CLH触发,而等效K端由CLL端触发,其余功能与一般的JK触发器相同。将图(a)作为一个单元与一个常规的D触发器组合,并在时钟端加上反相器,可以构成对称输出的三分频电路,如图(b)所示。图(c)是一个实际应用电路。图中因为采用了下降沿触发的74LS113,所以省去了它与74LS109时钟端之间的反相器。电路74LS109和74LS113的一半构成图(a)同样功能的电路。而74LS113的另一半相当于图(b)的D触发器。 |

网友评论