ЕчТЗГЃЪЖадИХФюЃЈ5ЃЉ-ЩЯРЕчзшЁЂЯТРЕчзш / РЕчСїЁЂЙрЕчСї / ЩШГіЯЕЪ§

ЗЂВМЪБМфЃК2011-4-20 17:13

ЗЂВМепЃК1770309616

|

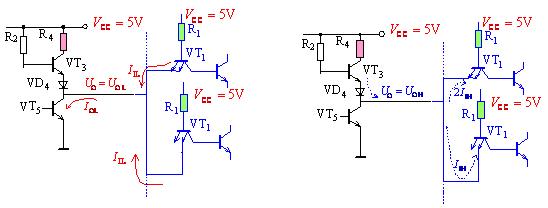

(вЛ)ЩЯРЕчзшЃК 1ЁЂЕБTTLЕчТЗЧ§ЖЏCOMSЕчТЗЪБЃЌШчЙћTTLЕчТЗЪфГіЕФИпЕчЦНЕЭгкCOMSЕчТЗЕФзюЕЭИпЕчЦН ЃЈвЛАуЮЊ3.5VЃЉЃЌетЪБОЭашвЊдкTTLЕФЪфГіЖЫНгЩЯРЕчзшЃЌвдЬсИпЪфГіИпЕчЦНЕФжЕЁЃ 2ЁЂOCУХЕчТЗБиаыМгЩЯРЕчзшЃЌВХФмЪЙгУЁЃ 3ЁЂЮЊМгДѓЪфГів§НХЕФЧ§ЖЏФмСІЃЌгаЕФЕЅЦЌЛњЙмНХЩЯвВГЃЪЙгУЩЯРЕчзшЁЃ 4ЁЂдкCOMSаОЦЌЩЯЃЌЮЊСЫЗРжЙОВЕчдьГЩЫ№ЛЕЃЌВЛгУЕФЙмНХВЛФмаќПеЃЌвЛАуНгЩЯРЕчзшВњЩњНЕЕЭЪфШызшПЙЃЌЬсЙЉаЙКЩЭЈТЗЁЃЭЌrЙмНХаќПеОЭБШНЯШнвзНгЪмЭтНчЕФЕчДХИЩШХЃЈMOSЦїМўЮЊИпЪфШызшПЙЃЌМЋШнвзв§ШыЭтНчИЩШХЃЉЁЃ 5ЁЂаОЦЌЕФЙмНХМгЩЯРЕчзшРДЬсИпЪфГіЕчЦНЃЌДгЖјЬсИпаОЦЌЪфШыаХКХЕФдыЩљШнЯодіЧППЙИЩШХФмСІЁЃ 6ЁЂЬсИпзмЯпЕФПЙЕчДХИЩШХФмСІЁЃЙмНХаќПеОЭБШНЯШнвзНгЪмЭтНчЕФЕчДХИЩШХЁЃ 7ЁЂГЄЯпДЋЪфжаЕчзшВЛЦЅХфШнвзв§Ц№ЗДЩфВЈИЩШХЃЌМгЩЯЯТРЕчзшЪЧЕчзшЦЅХфЃЌгааЇЕФвжжЦЗДЩфВЈИЩШХЁЃ (Жў)ЩЯРЕчзшзшжЕЕФбЁдёддђАќРЈ: 1ЁЂДгНкдМЙІКФМАаОЦЌЕФЙрЕчСїФмСІПМТЧгІЕБзуЙЛДѓЃКЕчзшДѓЃЌЕчСїаЁЁЃ 2ЁЂДгШЗБЃзуЙЛЕФЧ§ЖЏЕчСїПМТЧгІЕБзуЙЛаЁЃКЕчзшаЁЃЌЕчСїДѓЁЃ 3ЁЂЖдгкИпЫйЕчТЗЃЌЙ§ДѓЕФЩЯРЕчзшПЩФмБпбиБфЦНЛКЁЃ злКЯПМТЧвдЩЯШ§Еу,ЭЈГЃдк1kЕН10kжЎМфбЁШЁЁЃЖдЯТРЕчзшвВгаРрЫЦЕРРэЁЃ (Ш§)ЖдЩЯРЕчзшКЭЯТРЕчзшЕФбЁдёгІНсКЯПЊЙиЙмЬиадКЭЯТМЖЕчТЗЕФЪфШыЬиадНјааЩшЖЈЃЌжївЊашвЊПМТЧвдЯТМИИівђЫиЃК 1ЃЎ Ч§ЖЏФмСІгыЙІКФЕФЦНКтЁЃвдЩЯРЕчзшЮЊР§ЃЌвЛАуЕиЫЕЃЌЩЯРЕчзшдНаЁЃЌЧ§ЖЏФмСІдНЧПЃЌЕЋЙІКФдНДѓЃЌЩшМЦЪЧгІзЂвтСНепжЎМфЕФОљКтЁЃ 2ЃЎ ЯТМЖЕчТЗЕФЧ§ЖЏашЧѓЁЃЭЌбљвдЩЯРЕчзшЮЊР§ЃЌЕБЪфГіИпЕчЦНЪБЃЌПЊЙиЙмЖЯПЊЃЌЩЯРЕчзшгІЪЪЕБбЁдёвдФмЙЛЯђЯТМЖЕчТЗЬсЙЉзуЙЛЕФЕчСїЁЃ 3ЃЎ ИпЕЭЕчЦНЕФЩшЖЈЁЃВЛЭЌЕчТЗЕФИпЕЭЕчЦНЕФУХМїЕчЦНЛсгаВЛЭЌЃЌЕчзшгІЪЪЕБЩшЖЈвдШЗБЃФмЪфГіе§ШЗЕФЕчЦНЁЃвдЩЯРЕчзшЮЊР§ЃЌЕБЪфГіЕЭЕчЦНЪБЃЌПЊЙиЙмЕМЭЈЃЌЩЯРЕчзшКЭПЊЙиЙмЕМЭЈЕчзшЗжбЙжЕгІШЗБЃдкСуЕчЦНУХМїжЎЯТЁЃ 4ЃЎ ЦЕТЪЬиадЁЃвдЩЯРЕчзшЮЊР§ЃЌЩЯРЕчзшКЭПЊЙиЙмТЉдДМЖжЎМфЕФЕчШнКЭЯТМЖЕчТЗжЎМфЕФЪфШыЕчШнЛсаЮГЩRCбгГйЃЌЕчзшдНДѓЃЌбгГйдНДѓЁЃЩЯРЕчзшЕФЩшЖЈгІПМТЧЕчТЗдкетЗНУцЕФашЧѓЁЃ (ЫФ)ЯТРЕчзшЕФЩшЖЈЕФддђКЭЩЯРЕчзшЪЧвЛбљЕФЁЃ OCУХЪфГіИпЕчЦНЪБЪЧвЛИіИпзшЬЌЃЌЦфЩЯРЕчСївЊгЩЩЯРЕчзшРДЬсЙЉЃЌЩшЪфШыЖЫУПЖЫПкВЛДѓгк100uA,ЩшЪфГіПкЧ§ЖЏЕчСїдМ500uAЃЌБъзМЙЄзїЕчбЙЪЧ5VЃЌЪфШыПкЕФИпЕЭЕчЦНУХЯоЮЊ0.8V(ЕЭгкДЫжЕЮЊЕЭЕчЦН)ЃЛ2V(ИпЕчЦНУХЯожЕ)ЁЃ бЁЩЯРЕчзшЪБЃК 500uA x 8.4K= 4.2МДбЁДѓгк8.4KЪБЪфГіЖЫФмЯТРжС0.8VвдЯТЃЌДЫЮЊзюаЁзшжЕЃЌдйаЁОЭРВЛЯТРДСЫЁЃШчЙћЪфГіПкЧ§ЖЏЕчСїНЯДѓЃЌдђзшжЕПЩМѕаЁЃЌБЃжЄЯТРЪБФмЕЭгк0.8VМДПЩЁЃ ЕБЪфГіИпЕчЦНЪБЃЌКіТдЙмзгЕФТЉЕчСїЃЌСНЪфШыПкаш200uA 200uA x15K=3VМДЩЯРЕчзшбЙНЕЮЊ3VЃЌЪфГіПкПЩДяЕН2VЃЌДЫзшжЕЮЊзюДѓзшжЕЃЌдйДѓОЭРВЛЕН2VСЫЁЃбЁ10KПЩгУЁЃCOMSУХЕФПЩВЮПМ74HCЯЕСаЁЃ ЩшМЦЪБЙмзгЕФТЉЕчСїВЛПЩКіТдЃЌIOПкЪЕМЪЕчСїдкВЛЭЌЕчЦНЯТвВЪЧВЛЭЌЕФЃЌЩЯЪіНіНіЪЧдРэЃЌвЛОфЛАИХРЈЮЊЃКЪфГіИпЕчЦНЪБвЊЮЙБЅКѓУцЕФЪфШыПкЃЌЪфГіЕЭЕчЦНВЛвЊАбЪфГіПкЮЙГХСЫЃЈЗёдђЖргрЕФЕчСїЮЙИјСЫМЖСЊЕФЪфШыПкЃЌИпгкЕЭЕчЦНУХЯожЕОЭВЛПЩППСЫЃЉ ++++++++++++++++++++++++++++++++++++++++++++++ ЩЯРЕчзшЃКНЋФГЪфГіЕчЮЛЕуВЩгУЕчзшгыЕчдДVDDЯрСЌЕФЕчзшЁЃвђЮЊЪфГіЖЫПЩвдПДзїЪЧОпгаФкзшЕФЕчбЙдДЃЌгЩгкЩЯРЕчзшгыVDDСЌНгЃЌРћгУИУЕчзшЕФЗжбЙдРэЃЈвЛАуЩЯРЕчзшБШЪфГіЖЫФкзшДѓЕУЖрЃЌжСгкИУзшжЕЕФДѓаЁМћЩЯРЕчзшЕФбЁШЁддђЃЉЃЌДгЖјНЋЪфГіЖЫЕчЮЛРИпЁЃ 1ЃЌШчЙћЕчЦНгУOC(МЏЕчМЋПЊТЗЃЌTTL)ЛђOD(ТЉМЋПЊТЗЃЌCOMS)ЪфГіЃЌФЧУДВЛгУЩЯРЕчзшЪЧВЛФмЙЄзїЕФЃЌ етИіКмШнвзРэНтЃЌЙмзгУЛгаЕчдДОЭВЛФмЪфГіИпЕчЦНСЫЁЃ 2ЃЌШчЙћЪфГіЕчСїБШНЯДѓЃЌЪфГіЕФЕчЦНОЭЛсНЕЕЭЃЈЕчТЗжавбОгаСЫвЛИіЩЯРЕчзшЃЌЕЋЪЧЕчзшЬЋДѓЃЌбЙНЕЬЋИпЃЉЃЌОЭПЩвдгУЩЯРЕчзшЬсЙЉЕчСїЗжСПЃЌ АбЕчЦНЁАРИпЁБЁЃЃЈОЭЪЧВЂвЛИіЕчзшдкICФкВПЕФЩЯРЕчзшЩЯЃЌ ШУЫќЕФбЙНЕаЁвЛЕуЃЉЁЃЕБШЛЙмзгАДашвЊИУЙЄзїдкЯпадЗЖЮЇЕФЩЯРЕчзшВЛФмЬЋаЁЁЃЕБШЛвВЛсгУетИіЗНЪНРДЪЕЯжУХЕчТЗЕчЦНЕФЦЅХфЁЃ ашвЊзЂвтЕФЪЧЃЌЩЯРЕчзшЬЋДѓЛсв§Ц№ЪфГіЕчЦНЕФбгГйЁЃЃЈRCбгЪБЃЉ вЛАуCMOSУХЕчТЗЪфГіВЛФмИјЫќаќПеЃЌЖМЪЧНгЩЯРЕчзшЩшЖЈГЩИпЕчЦНЁЃ ЯТРЕчзшЃККЭЩЯРЕчзшЕФдРэВюВЛЖрЃЌжЛЪЧРЕНGNDШЅЖјвбЃЌФЧбљЕчЦНОЭЛсБЛРЕЭЁЃ ЯТРЕчзшвЛАугУгкЩшЖЈЕЭЕчЦНЛђепЪЧзшПЙЦЅХф(ПЙЛиВЈИЩШХ[size=+0])ЁЃ [size=+0]ЩЯРЕчзшЕФЙЄзїдРэЕчТЗЭМ [size=+0]

ШчЩЯЭМЫљЪОЃЌЩЯВПЕФвЛИіBias Resaitor ЕчзшвђЮЊЪЧНгЕиЃЌвђЖјНазіЯТРЕчзшЃЌвтЫМЪЧНЋЕчТЗНкЕуAЕФЕчЦНЯђЕЭЗНЯђЃЈЕиЃЉРЃЛЭЌбљЃЌЭМжаЯТВПЕФвЛИіBias Resaitor ЕчзшвђЮЊНгЕчдДЃЈе§ЃЉЃЌвђЖјНазіЩЯРЕчзшЃЌвтЫМЪЧНЋЕчТЗНкЕуAЕФЕчЦНЯђИпЗНЯђЃЈЕчдДе§ЃЉРЁЃЕБШЛЃЌаэЖрЕчТЗжаЩЯРЕчзшКЭЯТРЕчзшжаМфЕФФЧИі12kЕчзшЪЧУЛгаЕФЛђепЪЧПДВЛЕНЕФЁЃ ЩЯЭМЪЧRSЃ485/RSЃ422змЯпЩЯЕФЃЌПЩвдвЛЯТзгШЯЪЖЩЯРЕчзшКЭЯТРЕчзшЕФвтЫМЁЃЕЋаэЖрЕчТЗжЛгавЛИіЩЯРЕчзшЛђЯТРЕчзшЃЌЖјЧвЪЕМЪжаЃЌЛЙЪЧЩЯРЕчзшЕФЮЊЖрЁЃ ++++++++++++++++++++++++++++++++++++++++++++++дкЪ§зжЕчТЗжаВЛгУЕФЪфШыНХЖМвЊНгЙЬЖЈЕчЦНЃЌЭЈЙ§1kЕчзшНгИпЕчЦНЛђНгЕиЁЃ 1ЁЂЖЈвхЃК ЩЯРОЭЪЧНЋВЛШЗЖЈЕФаХКХЭЈЙ§вЛИіЕчзшЧЖЮЛдкИпЕчЦНЃЁЕчзшЭЌЪБЦ№ЯоСїзїгУЃЁЯТРЭЌРэЃЁ ЩЯРЪЧЖдЦїМўзЂШыЕчСїЃЌЯТРЪЧЪфГіЕчСї ШѕЧПжЛЪЧЩЯРЕчзшЕФзшжЕВЛЭЌЃЌУЛгаЪВУДбЯИёЧјЗж ЖдгкЗЧМЏЕчМЋЃЈЛђТЉМЋЃЉПЊТЗЪфГіаЭЕчТЗЃЈШчЦеЭЈУХЕчТЗЃЉЬсЩ§ЕчСїКЭЕчбЙЕФФмСІЪЧгаЯоЕФЃЌЩЯРЕчзшЕФЙІФмжївЊЪЧЮЊМЏЕчМЋПЊТЗЪфГіаЭЕчТЗЪфГіЕчСїЭЈЕРЁЃ 2ЁЂЮЊЪВУДвЊЪЙгУРЕчзшЃК вЛАузїЕЅМќДЅЗЂЪЙгУЪБЃЌШчЙћICБОЩэУЛгаФкНгЕчзшЃЌЮЊСЫЪЙЕЅМќЮЌГждкВЛБЛДЅЗЂЕФзДЬЌЛђЪЧДЅЗЂКѓЛиЕНдзДЬЌЃЌБиаыдкICЭтВПСэНгвЛЕчзшЁЃ Ъ§зжЕчТЗгаШ§жжзДЬЌЃКИпЕчЦНЁЂЕЭЕчЦНЁЂКЭИпзшзДЬЌЃЌгааЉгІгУГЁКЯВЛЯЃЭћГіЯжИпзшзДЬЌЃЌПЩвдЭЈЙ§ЩЯРЕчзшЛђЯТРЕчзшЕФЗНЪНЪЙДІгкЮШЖЈзДЬЌЃЌОпЬхЪгЩшМЦвЊЧѓЖјЖЈЃЁ вЛАуЫЕЕФЪЧI/OЖЫПкЃЌгаЕФПЩвдЩшжУЃЌгаЕФВЛПЩвдЩшжУЃЌгаЕФЪЧФкжУЃЌгаЕФЪЧашвЊЭтНгЃЌI/OЖЫПкЕФЪфГіРрЫЦгквЛИіШ§МЋЙмЕФCЃЌЕБCНгЭЈЙ§вЛИіЕчзшКЭЕчдДСЌНгдквЛЦ№ЕФЪБКђЃЌИУЕчзшГЩЮЊЩЯCРЕчзшЃЌвВОЭЪЧЫЕЃЌШчЙћИУЖЫПке§ГЃЪБЮЊИпЕчЦНЃЌCЭЈЙ§вЛИіЕчзшКЭЕиСЌНгдквЛЦ№ЕФЪБКђЃЌИУЕчзшГЦЮЊЯТРЕчзшЃЌЪЙИУЖЫПкЦНЪБЮЊЕЭЕчЦНЃЌзїгУТ№ЃК БШШчЃКЕБвЛИіНггаЩЯРЕчзшЕФЖЫПкЩшЮЊЪфШчзДЬЌЪБЃЌЫћЕФГЃЬЌОЭЮЊИпЕчЦНЃЌгУгкМьВтЕЭЕчЦНЕФЪфШыЁЃ ЩЯРЕчзшЪЧгУРДНтОізмЯпЧ§ЖЏФмСІВЛзуЪБЬсЙЉЕчСїЕФЁЃвЛАуЫЕЗЈЪЧРЕчСїЃЌЯТРЕчзшЪЧгУРДЮќЪеЕчСїЕФЃЌвВОЭЪЧЙрЕчСїЁЃ +++++++++++++++++++++++++++++++++ РЕчСїгыЙрЕчСї 1ЁЂИХФю РЕчСїКЭЙрЕчСїЪЧКтСПЕчТЗЪфГіЧ§ЖЏФмСІЃЈзЂвтЃКРЁЂЙрЖМЪЧЖдЪфГіЖЫЖјбдЕФЃЌЫљвдЪЧЧ§ЖЏФмСІЃЉЕФВЮЪ§ЃЌетжжЫЕЗЈвЛАугУдкЪ§зжЕчТЗжаЁЃ етРяЪзЯШвЊЫЕУїЃЌаОЦЌЪжВсжаЕФРЁЂЙрЕчСїЪЧвЛИіВЮЪ§жЕЃЌЪЧаОЦЌдкЪЕМЪЕчТЗжадЪаэЪфГіЖЫРЁЂЙрЕчСїЕФЩЯЯожЕЃЈдЪаэзюДѓжЕЃЉЁЃЖјЯТУцвЊНВЕФетИіИХФюЪЧЕчТЗжаЕФЪЕМЪжЕЁЃ гЩгкЪ§зжЕчТЗЕФЪфГіжЛгаИпЁЂЕЭЃЈ0ЃЌ1ЃЉСНжжЕчЦНжЕЃЌИпЕчЦНЪфГіЪБЃЌвЛАуЪЧЪфГіЖЫЖдИКдиЬсЙЉЕчСїЃЌЦфЬсЙЉЕчСїЕФЪ§жЕНаЁАРЕчСїЁБЃЛЕЭЕчЦНЪфГіЪБЃЌвЛАуЪЧЪфГіЖЫвЊЮќЪеИКдиЕФЕчСїЃЌЦфЮќЪеЕчСїЕФЪ§жЕНаЁАЙрЃЈШыЃЉЕчСїЁБЁЃ ЖдгкЪфШыЕчСїЕФЦїМўЖјбдЃК ЙрШыЕчСїКЭЮќЪеЕчСїЖМЪЧЪфШыЕФЃЌ ЙрШыЕчСїЪЧБЛЖЏЕФЃЌ ЮќЪеЕчСїЪЧжїЖЏЕФЁЃ ШчЙћЭтВПЕчСїЭЈЙ§аОЦЌв§НХЯђаОЦЌФкЁЎСїШыЁЏГЦЮЊЙрЕчСїЃЈБЛЙрШыЃЉЃЛ ЗДжЎШчЙћФкВПЕчСїЭЈЙ§аОЦЌв§НХДгаОЦЌФкЁЎСїГіЁЏГЦЮЊРЕчСїЃЈБЛРГіЃЉ 2ЁЂЮЊЪВУДФмЙЛКтСПЪфГіЧ§ЖЏФмСІ ЕБТпМУХЪфГіЖЫЪЧЕЭЕчЦНЪБЃЌЙрШыТпМУХЕФЕчСїГЦЮЊЙрЕчСїЃЌЙрЕчСїдНДѓЃЌЪфГіЖЫЕФЕЭЕчЦНОЭдНИпЁЃгЩШ§МЋЙмЪфГіЬиадЧњЯпвВПЩвдПДГіЃЌЙрЕчСїдНДѓЃЌБЅКЭбЙНЕдНДѓЃЌЕЭЕчЦНдНДѓЁЃ ШЛЖјЃЌТпМУХЕФЕЭЕчЦНЪЧгавЛЖЈЯожЦЕФЃЌЫќгавЛИізюДѓжЕUOLMAXЁЃдкТпМУХЙЄзїЪБЃЌВЛдЪаэГЌЙ§етИіЪ§жЕЃЌTTLТпМУХЕФЙцЗЖЙцЖЈUOLMAX Ём0.4ЁЋ0.5VЁЃЫљвдЃЌЙрЕчСїгавЛИіЩЯЯоЁЃ ЕБТпМУХЪфГіЖЫЪЧИпЕчЦНЪБЃЌТпМУХЪфГіЖЫЕФЕчСїЪЧДгТпМУХжаСїГіЃЌетИіЕчСїГЦЮЊРЕчСїЁЃРЕчСїдНДѓЃЌЪфГіЖЫЕФИпЕчЦНОЭдНЕЭЁЃетЪЧвђЮЊЪфГіМЖШ§МЋЙмЪЧгаФкзшЕФЃЌФкзшЩЯЕФЕчбЙНЕЛсЪЙЪфГіЕчбЙЯТНЕЁЃРЕчСїдНДѓЃЌЪфГіЖЫЕФИпЕчЦНдНЕЭЁЃ ШЛЖјЃЌТпМУХЕФИпЕчЦНЪЧгавЛЖЈЯожЦЕФЃЌЫќгавЛИізюаЁжЕUOHMINЁЃдкТпМУХЙЄзїЪБЃЌВЛдЪаэГЌЙ§етИіЪ§жЕЃЌTTLТпМУХЕФЙцЗЖЙцЖЈUOHMIN Ён2.4VЁЃЫљвдЃЌРЕчСївВгавЛИіЩЯЯоЁЃ ПЩМћЃЌЪфГіЖЫЕФРЕчСїКЭЙрЕчСїЖМгавЛИіЩЯЯоЃЌЗёдђИпЕчЦНЪфГіЪБЃЌРЕчСїЛсЪЙЪфГіЕчЦНЕЭгкUOHMINЃЛЕЭЕчЦНЪфГіЪБЃЌЙрЕчСїЛсЪЙЪфГіЕчЦНИпгкUOLMAXЁЃЫљвдЃЌРЕчСїгыЙрЕчСїЗДгГСЫЪфГіЧ§ЖЏФмСІЁЃЃЈаОЦЌЕФРЁЂЙрЕчСїВЮЪ§жЕдНДѓЃЌвтЮЖзХИУаОЦЌПЩвдНгИќЖрЕФИКдиЃЌвђЮЊЃЌР§ШчЙрЕчСїЪЧИКдиИјЕФЃЌИКдидНЖрЃЌБЛЙрШыЕФЕчСїдНДѓЃЉ гЩгкИпЕчЦНЪфШыЕчСїКмаЁЃЌдкЮЂАВМЖЃЌвЛАуПЩвдВЛБиПМТЧЃЌЕЭЕчЦНЕчСїНЯДѓЃЌдкКСАВМЖЁЃЫљвдЃЌЭљЭљЕЭЕчЦНЕФЙрЕчСїВЛГЌБъОЭВЛЛсгаЮЪЬтЁЃгУЩШГіЯЕЪ§РДЫЕУїТпМУХРДЧ§ЖЏЭЌРрУХЕФФмСІЃЌЩШГіЯЕЪ§NoЪЧЕЭЕчЦНзюДѓЪфГіЕчСїКЭЕЭЕчЦНзюДѓЪфШыЕчСїЕФБШжЕЁЃ =========================== дкМЏГЩЕчТЗжаЃЌ ЮќЕчСїЁЂРЕчСїЪфГіКЭЙрЕчСїЪфГіЪЧвЛИіКмживЊЕФИХФюЁЃ РМДаЙЃЌжїЖЏЪфГіЕчСїЃЌЪЧДгЪфГіПкЪфГіЕчСїЁЃ ЙрМДГфЃЌБЛЖЏЪфШыЕчСїЃЌЪЧДгЪфГіЖЫПкСїШы ЮќдђЪЧжїЖЏЮќШыЕчСїЃЌЪЧДгЪфШыЖЫПкСїШы ЮќЕчСїКЭЙрЕчСїОЭЪЧДгаОЦЌЭтЕчТЗЭЈЙ§в§НХСїШыаОЦЌФкЕФЕчСї,ЧјБ№дкгкЮќЪеЕчСїЪЧжїЖЏЕФЃЌДгаОЦЌЪфШыЖЫСїШыЕФНаЮќЪеЕчСїЁЃЙрШыЕчСїЪЧБЛЖЏЕФ,ДгЪфГіЖЫСїШыЕФНаЙрШыЕчСїЁЃ РЕчСїЪЧЪ§зжЕчТЗЪфГіИпЕчЦНИјИКдиЬсЙЉЕФЪфГіЕчСїЃЌЙрЕчСїЪБЪфГіЕЭЕчЦНЪЧЭтВПИјЪ§зжЕчТЗЕФЪфШыЕчСїЃЌЫќУЧЪЕМЪОЭЪЧЪфШыЁЂЪфГіЕчСїФмСІЁЃ ЮќЪеЕчСїЪЧЖдЪфШыЖЫЃЈЪфШыЖЫЮќШыЃЉЖјбдЕФЃЛЖјРЕчСїЃЈЪфГіЖЫСїГіЃЉКЭЙрЕчСїЃЈЪфГіЖЫБЛЙрШыЃЉЪЧЯрЖдЪфГіЖЫЖјбдЕФ[size=+0]ЁЃ [size=+0]+++++++++++++++++++++++++++++++++++++ [size=+0]ИјвЛИіжБЙлНтЪЭЃК [size=+0]

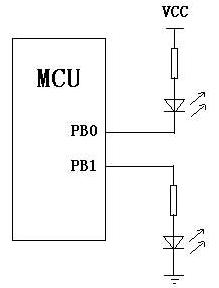

[size=+0] ЭМжаPB0ЪфГі0ЃЌLEDЛсССЃЌPB0ЕФЕчСїЗНЯђЪЧСїЯђPB0вВОЭЪЧЙрЕчСїСЫЃЛЖјPB1вЊЪфГі1ЃЌLEDЛсССЃЌPB1ЕФЕчСїЗНЯђЪЧДгPB1СїГіЃЌвВОЭЪЧРЕчСїСЫЁЃ [size=+0]+++++++++++++++++++++++++++++++++++++ [size=+0]дкЪЕМЪЕчТЗжаЙрЕчСїЪЧгЩКѓУцЫљНгЕФТпМУХЪфШыЕЭЕчЦНЕчСїЛуМЏдквЛЦ№ЖјЙрШыЧАУцТпМУХЕФЪфГіЖЫЫљаЮГЩЃЌЖСепВЮдФЭМ18-2-3здУїЁЃЯдШЛЫќЕФВтЪдЕчТЗгІИУШчЭМ18-2-4(b)ЫљЪОЃЌЪфШыЖЫЫљМгЕФТпМЕчЦНЪЧБЃжЄЪфГіЖЫФмЙЛЛёЕУЕЭЕчЦНЃЌжЛВЛЙ§ЙрЕчСїЪЧЭЈЙ§НгЯђЕчдДЕФвЛжЛЕчЮЛЦїЖјЛёЕУЕФЃЌЕїНкЕФЕчЮЛЦїПЩИФБфЙрЕчСїЕФДѓаЁЃЌЪфГіЕЭЕчЦНЕФЕчбЙжЕвВНЋЫцжЎБфЛЏЁЃ

(a) ЙрЕчСїИКди (b) РЕчСїИКди ЭМ18-2-3 ЙрЕчСїгыЗХЕчСїЪОвтЭМ

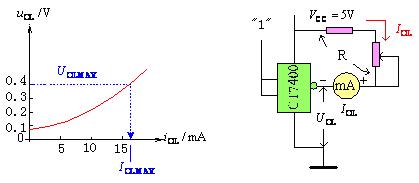

(a) ЙрЕчСїИКдиЬиадЧњЯп (b) ВтЪдЕчТЗ ЭМ18-2-4 ЙрЕчСїИКдиЬиадЧњЯпМАВтЪдЕчТЗ ЕБЪфГіЕЭЕчЦНЕФЕчбЙжЕЫцзХЙрЕчСїЕФдіМгЖјдіМгЕНЪфГіЕЭЕчЦНзюДѓжЕЪБЃЌМДuOL=UOLMAXЪБЫљЖдгІЕФЙрЕчСїжЕЖЈвхЮЊЪфГіЕЭЕчЦНЕчСїЕФСПДѓжЕIOLMAXЁЃ ВЛЭЌЯЕСаЕФТпМЕчТЗЃЌЭЌвЛЯЕСажаВЛЭЌЕФаЭКХЕФМЏГЩЕчТЗЃЌЙњМвБъзМжаЖдЪфГіЕЭЕчЦНЕчСїЕФзюДѓжЕIOLMAXЕФЙцЗЖжЕЕФЙцЖЈЭљЭљЪЧВЛЭЌЕФЁЃБШНЯГЃгУЕФЪ§жЕШчЯТ TTLЯЕСа IOLMAX=16mA LSTTL74ЯЕСа IOLMAX=8mA LSTTL54ЯЕСа IOLMAX=4mA ЩШГіЯЕЪ§NOЪЧУшЪіМЏГЩЕчТЗДјИКдиФмСІЕФВЮЪ§ЃЌЫќЕФЖЈвхЪНШчЯТ 18-2-1) NO= IOLMAX / IILMAX NoдНДѓЃЌЫЕУїУХЕФИКдиФмСІдНЧПЁЃвЛАуВњЦЗЙцЖЈвЊЧѓNoЁн8ЁЃ дкОіЖЈЩШГіЯЕЪ§ЪБЃЌе§ШЗМЦЫуЕчСїжЕЪЧживЊЕФЃЌЖдгкЭМ18-2-3ЖјбдЃЌКѓУцЫљНгЕФТпМУХЕФЪфШыЖЫгаВЂСЊЕФЧщПіЁЃЕБЪфГіЮЊЕЭЕчЦНЪБЃЌКѓУцТпМУХЪфШыЖЫСїГіЕФIILЃЌвђгаR1ЕФЯоСїзїгУЃЌгыВЂСЊЖЫЭЗЪ§ЮоЙиЁЃЕЋЪЧЃЌЕБЪфГіЮЊИпЕчЦНЪБЃЌЕчСїЕФЗНЯђИФБфЮЊСїНјЪфШыЖЫЃЌКѓУцТпМУХЪфШыМЖЕФЖрЗЂЩфМЋШ§МЋЙмЯрЕБгаСНИіШ§МЋЙмВЂСЊЁЃСїШыЕФIIHОЭвЊМгБЖЃЌгыВЂСЊЖЫЭЗЪ§гаЙиЁЃЖдгкЭМ18-2-3ЃЌNOL=2ЃЌЖјNOH=3ЃЌЪфГіЕЭЕчЦНКЭЪфГіИпЕчЦНСНжжЧщПіЯТЃЌЩШГіЯЕЪ§ПЩФмЪЧВЛЭЌЕФЁЃгЩгкIILЕФЪ§жЕБШIIHЕФЪ§жЕвЊДѓКмЖрЃЌЖдгкМЏГЩЕчТЗРДЫЕУЌЖмЕФжївЊЗНУцдкЕЭЕчЦНЩШГіЯЕЪ§ЁЃЫљвдЃЌвЛАуЮвУЧжЛашвЊПМТЧЕЭЕчЦНЩШГіЯЕЪ§ОЭПЩвдСЫЁЃ |

ЭјгбЦРТл