28nm芯片工艺, Xilinx和Altera各执一词

发布时间:2011-4-20 15:06

发布者:绝对好文

|

作者:Alicon 近期, Xilinx和Altera分别在公司召开了28nm工艺新器件发布会。与技术研究该有的严谨不同,对技术成果的展示可以生动活泼。生动活泼之中两家含沙射影的“攻击”让人感叹。 正如她们的发布会礼品都选择Sennheiser一样,她们的28nm工艺都选择了TSMC(台积电)。工艺提高意味着更大的集成度,更低的成本和更好的性能。所以,对工艺的宣传绝对是FPGA厂商的策略之一。在40nm工艺及以前,Xilinx选择的是UMC(台联电),随着摩尔定律的深入,UMC渐渐跟不上脚步,Xilinx向Altera的老搭档敞开了怀抱。FPGA就是为“差异化”而生的,所以FPGA厂商在宣传时自然不会忘记“差异化”。但是,同一供应商的同一工艺节点,她们如何在宣传上“差异化”呢? Xilinx: 传统的 FPGA 工艺技术在 28nm 工艺上已经达到了功耗极限,因此也达到了性能极限。问题的根源在于几十年来用于构建 IC 晶体管的多晶/氮氧化硅。为了提高晶体管的速度,半导体工程师一直在随着工艺技术的提高努力减小门介电层的厚度。不过,由于介电层的隧道效应和门本身的漏电流,电介质厚度的减少会导致漏电流增加,这就造成工艺技术每次节点进步都会大幅提升静态功耗。 赛灵思以创新型的三重门极氧化层电路技术成功控制隧道电流效果,从 90nm 工艺到40nm 工艺节点一直都比较成功。不过,就 28nm 工艺而言,门极氧化层太薄了,必须用最新门材料和架构来处理隧道效果。为了控制门下的漏电流 (亚阈值泄漏),赛灵思工程师在整体晶体管设计过程中进行了审慎权衡。 为了解决28nm工艺问题,赛灵思采用了二氧化铪这种新型门介电材料,该材料的介电常数 (κ) 较高,可增减门极厚度,这就使晶体管不太容易受到隧道电流效应的影响。 举例来说,40nm 工艺使用的二氧化硅 κ 值为 3.9,而 28nm 金属闸技术所用的二氧化铪 κ 值则为 25,这就成为高性能低功耗 28nm 工艺技术的最佳选择 (参见图1)。

赛灵思评估了多种 28nm 工艺技术,其中包括标准的低功耗 (LP) 和高性能 (HP) 工艺,最后决定采用 28nm HKMG 高性能低功耗工艺技术。 28nm 低功耗工艺是多晶/氮氧化硅 40nm 技术的简单升级,风险较低。不幸的是,该技术不适用于 FPGA,因为其晶体管切换速度太慢,性能不够高。与此形成对比的是,28nm 高性能技术专为实现高性能而优化,但又会造成功耗过高,也限制了可用性能 (参见图2)。

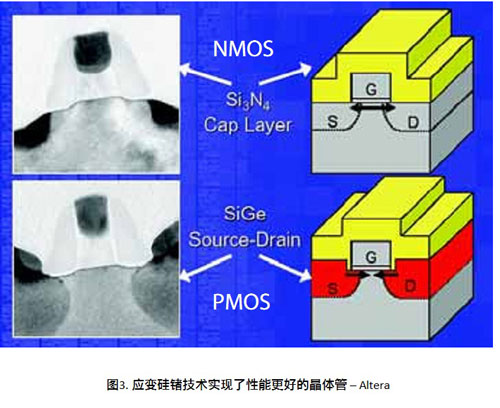

28nm 高性能(HP)工艺技术还需要将 HKMG 与 SiGe 应变技术相结合。两种高级技术在制造工艺中相结合,相对于采用 HKMG 和应力衬垫应变技术的更为简单的高性能低功耗 28nm 工艺技术而言会存在更多风险。 除了与业界领先公司 UMC 开展 40nm 工艺技术合作之外,赛灵思对多种工艺进行广泛评估之后,现在还与业界两大领先的芯片代工厂台积电和三星电子开展 28nm 工艺合作。台积电和三星电子最能满足赛灵思的新一代 FPGA 产品需求。这两家代工厂的技术都为性能和功率效率进行了平衡优化,可满足确切的产品要求。赛灵思的 28nm 技术与其业经验证的多代工厂战略一致,从而可以加速产品上市进程,保持技术领先地位,同时还能通过不同地理位置的合作减轻供应风险。 Altera: 过渡到小工艺尺寸总是能够提高集成度,性能优于以前的节点,28nm也不例外。28nm工艺具有明显的性能优势,但是,要充分发挥这些优势,需要为28nm工艺创造合适的环境。Altera选择TSMC 28HP高K金属栅极(HKMG)工艺,借助与TSMC的长期合作,优化Stratix V FPGA低功耗工艺。 不仅引入HKMG实现了28nm优异的性能,而且还采用了第二代高级应变技术加速了电路设计,包括晶体管源漏区的嵌入硅锗(SiGe)等技术。Altera通过覆盖层在NMOS晶体管产生拉伸应变,通过源极和漏极的嵌入硅锗在PMOS晶体管产生压缩应变。这些应变硅技术使电子和空穴的移动能力提高了近30%,晶体管性能增强了40%以上。通过应变硅技术在同样泄露的条件下获得了更好的性能,因此,性能的提高抵消了泄露的影响,与没有采用应变硅的工艺相比,提高了工艺性能减少了泄露。其他28nm工艺技术还没有同时结合HKMG和高级应变技术来提高性能。

应该说,Xilinx转向Altera的老搭档看上去颇有几分无奈。可能是Xilinx也没有十二分的把握,所以他选择了SAMSUNG和TSMC两家foundry。塞翁失马,焉知非福,在全世界都笼罩在日本地震中的今天来看,Xilinx的这句“通过不同地理位置的合作减轻供应风险”真是歪打正着。 另外,Altera的“应变硅锗技术”看上去应该不是“使电子和空穴的移动能力提高了近30%”,而是改变了PMOS和NMOS的沟道长度。在发布会上Altera说这是Altera和TSMC长期合作的益处,是产权属于Altera的专利技术。从Xilinx的表述中看来,是Xilinx觉得这种技术风险高所以没有采用,如果真是Altera的专利技术而且很关键,那估计Xilinx是不会主动提及的。我后来在Altera的官方文档中一直没有找到这样的说法。 |

网友评论