究竟是什么限制了MOSFET的性能——芯片、封装、驱动还是电路板?

发布时间:2011-4-16 23:34

发布者:1770309616

|

在追求不断提高能效的过程中,MOSFET的芯片和封装也在不断改进。尽管四十多年来我们对这种器件有了很多了解,但目前将它们有效地应用于电源产品依然面临挑战。根据具体应用建立FET性能模型并采用电子表格记录数据的经验丰富的设计人员,亦未能从熟悉的模型中获得满意的结果。 除了器件结构和加工工艺,MOSFET的性能还受其他几个周围相关因素的影响。这些因素包括封装阻抗、印刷电路板(PCB)布局、互连线寄生效应和开关速度。事实上,真正的开关速度取决于其他几个因素,例如切换的速度和保持栅极控制的能力,同时抑制栅极驱动回路电感带来的影响。同样,低栅极阈值还会加重Ldi/dt问题。 正因为了解电路中晶体管的性能很重要,所以我们将选用半桥拓扑。这种拓扑是电力电子装置最常用的拓扑之一。这些例子重点介绍了同步压降转换器——一个半桥拓扑的具体应用。 共源极电感效应

图1为具备杂散电感和电阻(由封装键合线、引线框以及电路板布局和互连线带来)等寄生效应的半桥电路。共源电感(CSI)倾向于降低控制FET(高边FET)的导通和关断速度。如果与栅极驱动串联,通过CSI的电压加至栅极驱动上,可使FET处于导通状态(条件:V = -Ldi/dt),从而延迟晶体管的关断。这也会增大控制FET的功耗,如图2所示。

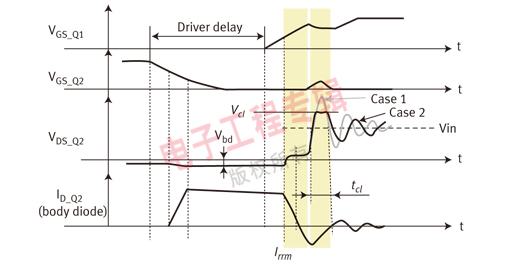

更高的功耗会导致转换效率降低。另外,由于杂散电感,电路出现尖峰电压的可能性很高。如果这些尖峰电压超过器件的额定值,可能会引起故障。 为了消除或使这种寄生电感最小化,设计人员必须采用类似无引脚或接线柱的DirecFET等封装形式,并采用使互连线阻抗最小化的布局。与标准封装不同,DirecFET无键合线或引线框。因此,它可极大地降低导通电阻,同时大幅降低开关节点的振铃,抑制开关损耗。 缓和C dv/dt感应导通 影响性能的另一个因素是C dv/dt感应导通(和由此产生的击穿)。C dv/dt通过栅漏电容CGD的反馈作用(引起不必要的低边FET导通),使低边(或同步)FET出现栅极尖峰电压。 实际上,当Q2的漏源极的电压升高时,电流就会经由栅漏电容CGD 流入总栅极电阻RG ,如图3(a)所示。因此,它会导致同步FET Q2的栅极出现尖峰电压。当该栅极电压超出规定的阈值时,它就会被迫导通。图3(b)显示的,正是在图3(a)所示 典型同步压降转换器拓扑中,同步FET Q2在这种工作模式下的主要波形。 若要准确地确定低边或同步MOSFET Q2的这种现象带来的功耗,需要对其漏源电压VDS_Q2 进行一段时间的钳位控制。在钳位控制时段,其功耗约为:

在这个等式中,Vcl 代表VDS_Q2 的钳位电压值;fs代表开关频率;Irrm 代表峰值反向恢复电流;tcl 代表反向恢复电流由Irrm 降至零所需的时间。 由上式可以看出,C dv/dt感应损耗是Vin、dv/dt和开关频率的函数,反过来,它也会受驱动速度、栅极电荷Qg、反向恢复电荷Qrr和布局的影响。因此,要想抑制这种不必要的导通,需要选择具备低荷比(QGD/QGS1)的适用同步MOSFET Q2。在QGD/QGS1中,QGD代表栅漏米勒电荷,QGS1代表栅极电压达到阈值之前的栅源电荷。尽管降低CDS 或增大CGS可降低C dv/dt感应电压,但Q2的C dv/dt感应导通还取决于漏源电压 VDS-Q2 和阈值电压Vth。由于栅极阈值电压会随着温度的升高而降低,因此这个问题在温度升高情况下会进一步恶化。因此,低阈值FET对C dv/dt问题尤其敏感。 在实际应用中,要想评估同步MOSFET Q2,需要了解栅极电容的栅极电荷性能。因此,聪明的办法是调查C dv/dt感应导通,这需要查看累积的米勒电荷。为避免Q2错误导通,设计人员必须确保当漏源电压VDS-Q2 达到输入电压时,它必须比栅源电容的总电荷低。 最大限度降低封装寄生效应 简单的数学分析表明,解决这个问题的最佳办法是选择小于1的电荷比QGD/QGS1。防止C dv/dt感应导通的其他因素包括低驱动漏极阻抗(<1 欧姆)、具备低RG的FET设计、外置的G-S电容器和具备最低寄生效应和电压振铃的Q2封装。 同步MOSFET Q2的导通电阻RDS(on) 及其封装,在抑制C dv/dt导通方面具备同等的重要性。实际上,近几年来,MOSFET供应商对各种封装进行了大幅改进,使通态电阻变得很低并最大限度降低寄生效应。例如以7引脚D2PAK封装为例,相对于同等的标准D2PAK封装,在相同漏源电压VDS条件下,它的导通电阻降低0.4 mΩ,同时大幅改进了电流处理功能。采用7引脚D2PAK封装的典型代表是IRFS3004-7PPBF。该MOSFET的额定电压为40 V,导通电阻为1.4 mΩ,漏电流(ID)为240 A。同样的芯片采用传统的D2PAK封装,其通态电阻为1.8 mΩ,额定漏电流为195 A。 其他改进的功率封装包括功率四方扁平无引脚封装(PQFN)和DirectFET等封装。PQFN封装具备多种变体。不过,与其他的封装不同,DirectFET未采用任何键合线和引线框,使封装电阻和寄生电感降至最低,如图4所示。

图5和图6为无芯片封装的电阻和寄生电感的测量值与不同类型MOSFET封装的频率的对比情况。

从这些图可以看出,DirectFET封装与DPAK、D2PAK、SO8 和微型引线框封装(MLP)等其他封装相比,相对于频率带来的电阻和电感可忽略不计。此外,DirecFET相对于带引脚的封装,其寄生感应值的变化最小,因为能够带来电阻和电感的封装已被降至最低程度。随着不久前对DirecFET材料和结构的改进,这种封装的电阻降至0.15 mΩ,寄生电感降低0.1 nH以下。唯一在封装电阻和电感方面与DirectFET接近的封装是MLP——PQFN的变体。 性能最大化

为进一步阐明上述的内容和更好地了解C dv/dt损耗对整个电路损耗的影响,让我们用两个MOSFET(参数如表1所示)例说明。1号器件具备高通态电阻和低电荷比值,而2号器件是具备低通态电阻和高电荷比值的晶体管。将这两个器件插入同步压降转换器具备相同的Q1 MOSFET和1 MHz开关频率的同步FET插槽。输入电 压为14 V,输出电压为1.3 V。

两个不同的同步FET的测量损耗如图7所示。从图7可以看到,在宽输出负载范围条件下,1号器件相对于2号器件的损耗更低。实际上,在10A负载条件下,1号器件的功耗比2号器件低0.72 W。整体而言,2号器件的功耗比1号器件高出约18%,这主要是由C dv/dt导通损耗造成的。其中的奥秘就在于,1号器件具备更低的栅漏电荷和电荷比,因此它具备更低的或不产生Cdv/dt损耗。由于负载电流对C dv/dt损耗的影响不大,因此在轻载条件下,功耗的变化基本无差别。 另一个可影响电源产品设计的MOSFET性能的因素是布局。例如,不合理的电路板布局可增大电源电路的寄生效应,反过来,增大的寄生效应又会提高电源的开关和导通损耗。此外,它还会提高电磁干扰的噪声水平,从而使设计出的产品达不到理想的性能。 若要最大限度降低电路板布局带来的影响,设计人员必须确保通过将驱动和MOSFET尽可能地背靠背放置,从而使输入回路面积最小化,如图8所示。

图8右侧有一个位于FET下方的小型陶瓷支路,利用过孔形成一个极小的输入回路。因此,需要将支路电容靠近驱动放置,并将输入陶瓷电容CIN 靠近高边MOSFET放置。在这里,控制回路FET相对于同步FET具备更高的优先权。 如果将FET并联,需要确保栅极回路阻抗匹配。另外,该布局必须采用隔离的模拟接地层和功率接地层,使大电流电路形成独立的回路,从而不干扰敏感的模拟电路。然后,必须将这两个接地层与PCB布局的一个点连接。此外,设计人员还必须利用多个过孔,使FET与输入引脚Vin或接地层连接。电路板上任何未用区域必须灌注铜。 总之,封装阻抗、PCB布局、互连线寄生效应和开关速度都是影响电源电路MOSFET性能的重要因素。因此,要想在高功率密度条件下获得最佳的转换效率,必须在设计MOSFET过程中,充分考虑封装、电路板布局(包括互连线)、阻抗和开关速度。 F3: 实际上,当Q2的漏源极的电压升高时,电流就会经由栅漏电容CGD 流入总栅极电阻RG ,如图3(a)所示。因此,它会导致同步FET Q2的栅极出现尖峰电压。当该栅极电压超出规定的阈值时,它就会被迫导通。图3(b)显示的,正是在图3(a)所示 典型同步压降转换器拓扑中,同步FET Q2在这种工作模式下的主要波形。

Figure 3a: 电流经由栅漏电容 流入总栅极电阻

Figure 3b: 同步FET的主要波形 作者:Eric Persson 国际整流器公司FAE执行总监 |

网友评论