ARM核920T性能优化之MMU

发布时间:2011-3-28 14:01

发布者:techshare

|

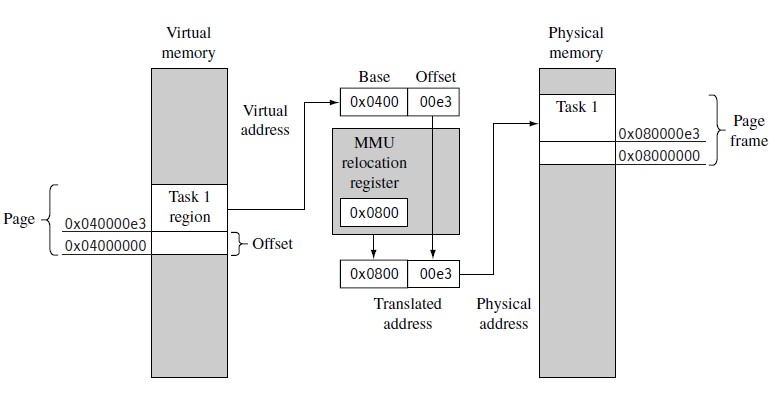

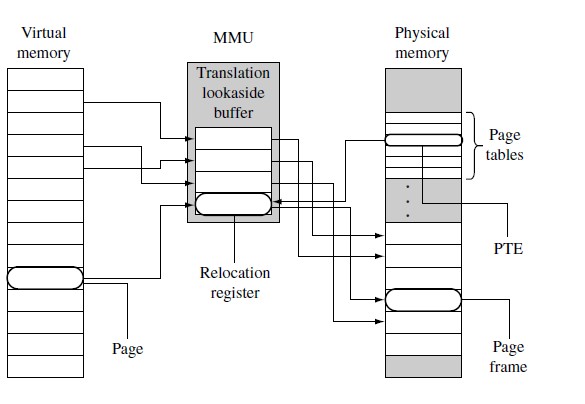

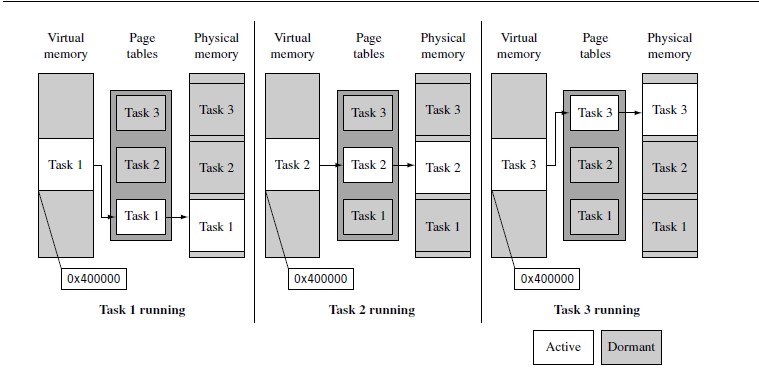

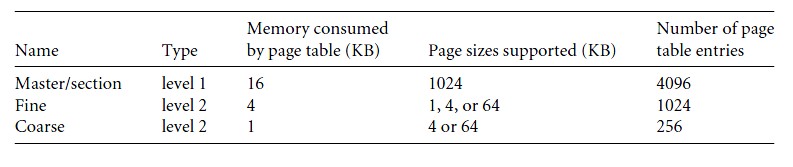

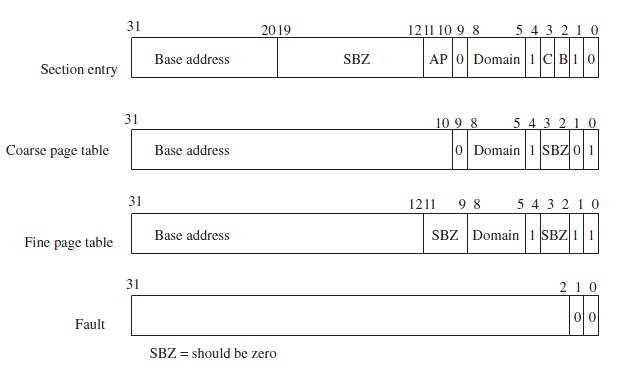

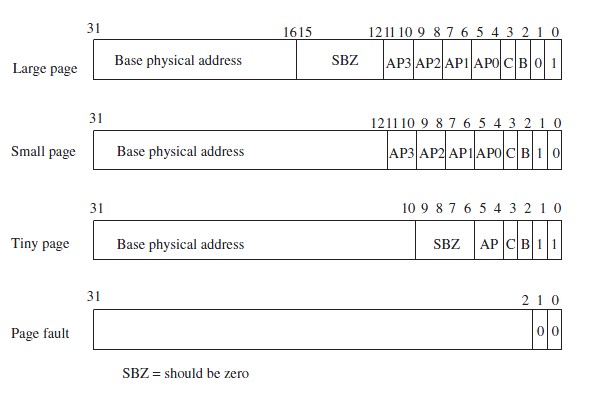

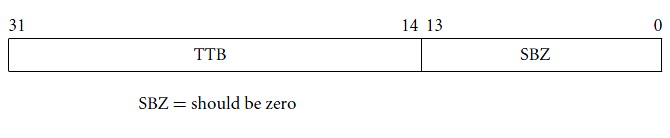

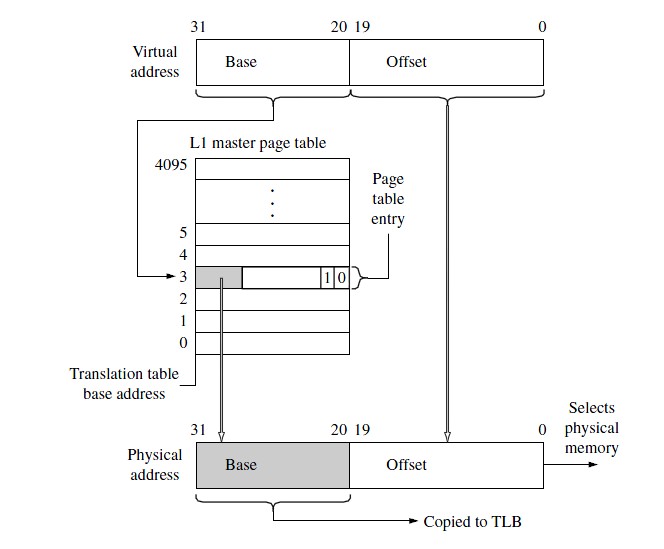

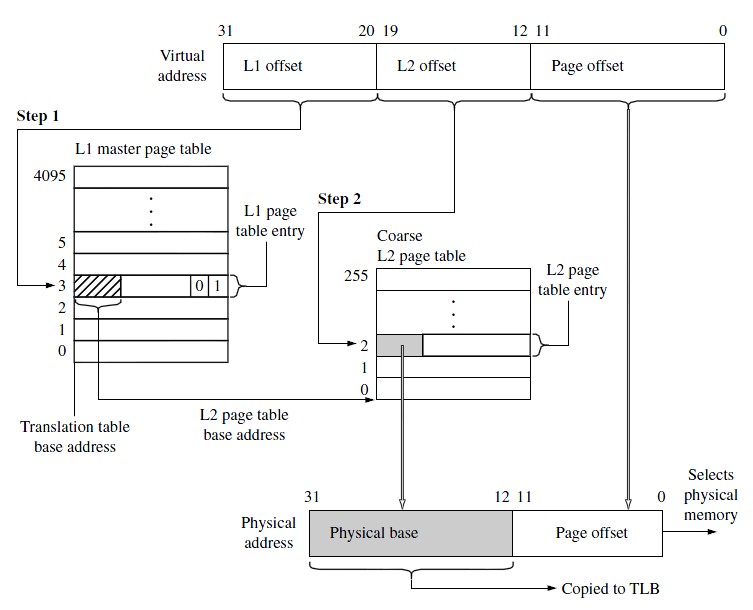

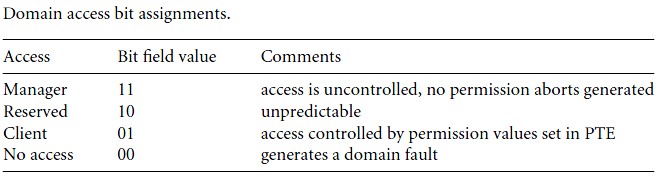

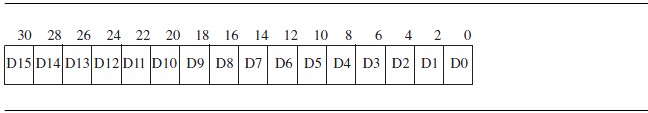

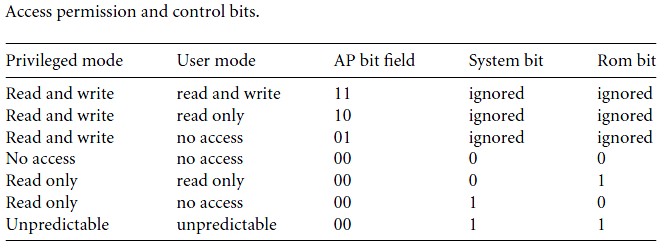

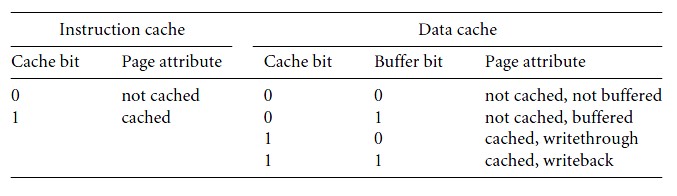

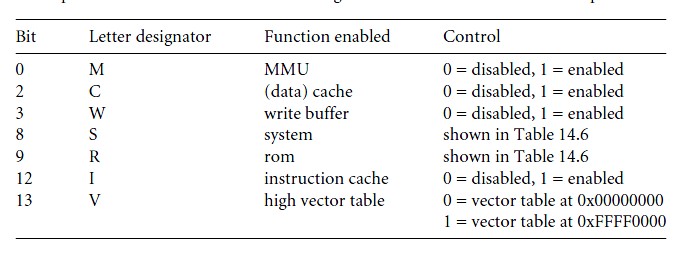

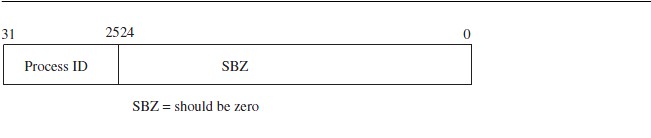

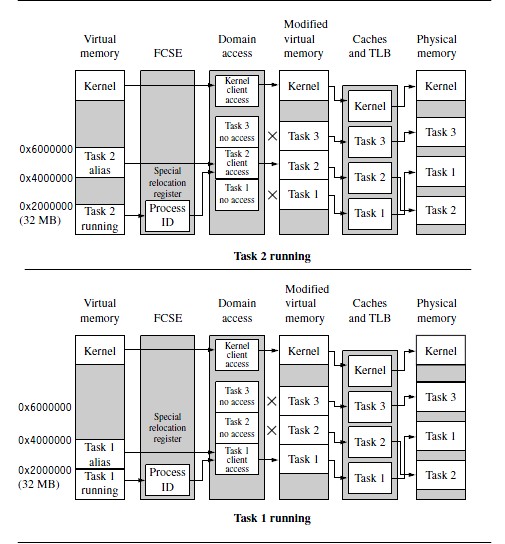

一.虚存的工作原理 为了使任务有各自的虚拟存储映射,MMU硬件采用地址重定位(address relocation),即在地址访问主存之前,转换由处理器核输出的存储器地址。可认为在介于内核和主存间的MMU中有一个重定位寄存器,这样就能很容易理解这个转换过程。  当处理器核产生一个虚拟地址时,MMU取出这个虚拟地址的高位,并用重定位寄存器中的值来替换它,从而形成一个物理地址。虚拟地址的低位是一个偏移量,它转换成物理存储器的一个特定地址。一个重定位寄存器只能转换一块存储空间,这块存储空间的大小由虚拟地址的偏移量部分所占的位数所决定。这样的一块虚拟存储空间称为一页(page),而转换过程中所对应的那块物理存储空间称为一个页帧(page frame)。  ARM MMU临时存放转换数据的一组重定位寄存器实际上是一个由64个重定位寄存器组成的全相联cache。这个cache称为转换旁路缓冲器(TLB),TLB缓存最近被访问的页的转换数据。除了使用重定位寄存器外,MMU还使用主存中的表来存放描述系统中用到的虚拟存储器映射的数据,这些转换数据的表称为页表(page tables)。页表中的每个页表项PTE(Page Table Entry)包含关于虚拟页的以下信息:用于将虚拟页转换为物理页的物理基地址,分配给该页的访问权限,页的cache和写缓冲器配置。  通过上下文切换时激活不同的页表,使得执行有重叠虚拟地址的多个任务成为可能。MMU可以重定位一个任务的执行地址,而无需在物理存储器中移动这个任务。任务的物理存储空间只是简单地通过激活和不激活页表来映射到虚拟存储空间。当刚刚提到的地址转换发生时,cache可能包括无效的,从旧的页表映射来的虚拟数据。为了保证存储器数据的一致性,cache可能需清理和清除。TLB可能也需清除,因为它也可能缓存了旧的转换数据。 任务切换需要以下步骤: 1)保存活跃任务的上下文,并将该任务置于睡眠态; 2)清除cache,如果使用回写策略,则需要清理D-cache; 3)清除TLB,从而移除原任务的转换数据; 4)配置MMU,以使用新的页表,把虚拟运行空间转换为被唤醒任务在物理存储器中的位置; 5)恢复被唤醒任务的上下文 6)继续执行恢复的任务 二.页表 ARM MMU硬件采用2级页表结构:一级页表(L1)和二级页表(L2)。一级页表只有一个L1主页表(L1 master page table)。L1主页表包含两种类型的页表项:保存指向二级页表起始地址指针的页表项和保存用于转换1MB段的页表项。L1主页表也称为段页表(section page table)。L1主页表将4GB的地址空间划分为多个1MB的段(section),因此L1页表包含4096个页表项,L1主页表是一个混合表,可作为L2页表的页目录,也可作为用于转换1MB虚拟空间的L2粗(coarse)页表或L2细(fine)页表的指针;当L1页表用于转换一个1MB的段时,其页表项(PTE)包含的是物理存储器中1MB页帧(page frame)的首地址。目录页表项和1MB的段页表项可以共存于L1主页表。  一级页表项: 一级页表支持4种类型的页表项: 1)1MB段转换项 2)指向L2细页表的目录项 3)指向L2粗页表的目录项 4)产生中止异常的错误项  二级页表项: L2页表有4种可能的页表项: 1)定义64KB页帧属性的大(large)页表项; 2)定义4KB页帧的小(small)页表项; 3)定义1KB页帧的微(tiny)页表项; 4)访问时产生页错误中止异常的错误页表项;  L1转换表基址 CP15:c2寄存器保存转换表基地址TTB(Translation Table Base address)-指向L1主页表在虚存中的位置。CP15:c2寄存器的格式如图:  三.转换旁路缓冲器(TLB) 单步页表搜索: 如果MMU搜索的是1MB大小的段页,则硬件能用单步搜索找到所要的页表项,因为1MB的页表项是存放在L1主页表里的。  2步页表搜索: 如果MMU搜索的是大小为1KB,4KB,16KB或64KB的页,则页表搜索须执行2步才能找到地址转换数据。  四.域和访问权限 有两种不同的控制用来管理一个任务的存储器访问权限,:域(domain)用于主控制(primay control),页表中的访问权限用于次控制(secondary control)。有16种不同的域可以分配给虚存的1MB段,并通过设置L1主页表项(PTE)中的域的有关位(位域)来分配给一个段。 当一个域分配给了一个段时,它必须遵守分配给这个域的访问权限。域的访问权限在CP15:c3寄存器中分配,它控制处理器核访问虚存段的能力。16个可用的域,每个域使用CP15:c3寄存器的2位来定义访问权限,域访问位取值及对应的意义如下表所列:   基于页表的访问权限。页表项中的AP位决定该页的访问权限。“AP”,“ap3”,“ap2”,“ap1”,“ap0”结合CP15寄存器C1的R/S位,决定如何进行访问权限检查。段描述符中的“AP” 控制整个段(1MB)的访问权限;大页描述符中的每个“apx”(x为0~3)控制一个大页(64KB)中1/4内存的访问权限,即“ap3”对应大页高端的16KB,“ap0”对应大页低端的16KB;小页描述符与大页描述符相似,每个“apx”控制一个小页(4KB)的1/4内存的访问权限。极小页中的“ap”就控制整个极小页1KB的访问权限。  五.Cache和写缓冲  六.CP15:c1控制寄存器  七.快速上下文切换扩展  快速上下文切换扩展FCSE(Fast Context Switch Extension),是MMU中的一个附加硬件,用于提高ARM嵌入式系统的系统性能。FCSE使得多个独立的任务可以运行在一个固定的重叠存储空间中,而上下文切换时又不需要清理或清除cache,或TLB。如果没有FCSE,则从一个任务切换到另一个任务需要改变虚拟存储映射。如果涉及两个有重叠地址的任务,则保存在cache和TLB中的信息将变为无效,这样系统就必须清除cache和TLB中的无效数据。清除这些模块的过程使任务切换增加了很多时间,因为内核不仅要清除cache和TLB中的无效数据,还要从主存中装载新的数据到cache和TLB。使用FCSE,虚拟存储管理增加了一次地址转换。FCSE在虚拟地址到达cache和TLB前,使用一个特殊的,包含进程ID值的重定位寄存器来修改虚拟地址。把修改之前的虚存地址称为VA(Virtual Address),把第一次转换之后的地址称为修改后虚地址MVA(Modified Virtual Address)。这样,任务间的切换就不用涉及到改变页表,只需简单的将新任务的进程ID写到位于CP15的FCSE进程ID寄存器。为了利用FCSE,编译链接所有的任务,使他们都运行在虚存的第一个32MB块空间,为每个任务分配一个进程ID;然后通过下边的公式,将每个任务放置在修改后虚存的不同32MB分区中: MVA = VA +(0x2000000 * 进程ID) 下图是一个快速上下文切换扩展的例子:在一个3任务的多任务环境中,切换前任务1运行,切换后任务2运行。  作者:李万鹏 |

网友评论