高性能中频采样系统的设计与实现

发布时间:2011-3-12 08:05

发布者:1770309616

关键词:

中频采样系统

|

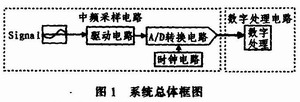

中频采样广泛应用于软件无线电、数字中频接收机、基站系统等通信领域。高性能的中频采样系统往往要求具备高信噪比、灵活可变的采样频率,支持高速高精度采样。根据以上要求。这里设计并实现了一种高性能中频采样系统。 1 系统总体设计 图1为中频采样系统总体设计框图。由图1可知,该系统主要由驱动电路、A/D转换电路、时钟电路3部分组成。

信号A/D转换前往往需要进行以下处理:1)放大或衰减,使输入信号的电平与A/D转换器的所需电平相吻合;2)直流补偿或电平转换,通过补偿提高或降低直流电平使之符合A/D转换器的工作电平;3)滤波。滤除信号杂波使频带宽度符合A/D转换器的要求。采用运算放大器设计的驱动电路可以很好的完成上述处理。 使用运算放大器作A/D转换器的接口还可作为缓存。大部分的A/D转换器并不能获得与输入电压范围相符合的输入信号,只有极少的情况下是相符的,这时需要在输入信号与A/D转换器之间加入一个缓存运放,这样可以解决以下问题:1)阻抗匹配,信号源往往并不是该系统设计所需的低阻抗,A/D转换器的输入将影响信号源。通常运算放大器缓存具有高输入阻抗,因此它不会对信号源产生影响。另外其低输出阻抗有益于A/D转换器的驱动;2)减小容性负载的影响。大多数的A/D转换器除在输入端具有电阻特性外,还具有电容效应。因此需要额外的补偿电路.通常用电阻或电容。运算放大器的低输出阻抗特性使其解决上述问题;3)将单端信号转换为差分信号,许多A/D转换器使用差分输入,而大多数信号是单端的。运算放大器可以完成这一转换。 1.2 A/D转换电路 A/D转换器的性能指标主要分为静态参数和动态参数2种。静态参数是指A/D转换电路在低频或直流下的性能参数,而动态参数则是指中频或射频信号输入时的性能参数。对于中频采样系统来说,由于输入信号频率较高,其动态特性对反映电路的性能具有更大意义。重要的动态特性指标包括:信噪比RSN、无杂散动态范围SFDR、有效比特位ENOB、积分非线性INL、微分非线性DNL等。 一个高性能的中频采样系统对噪声性能的要求很高,A/D转换器的噪声来源通常有:A/D转换器失真和量化噪声,A/D转换器等价输入噪声,内部抽样保持电路的孔径抖动,不良的接地和退耦设计,外部驱动放大器的噪声,不良的布局和信号走线设计,采样时钟噪声,外部电源噪声。针对以上噪声来源,该系统设计采用以下方法,力求减小噪声的引入:所有芯片的电源部分都采用钽电解电容与大面积,低阻抗的地层相退耦,用于去除低频噪声;使用铁氧体磁珠去除电源的高频噪声;模拟地与数字地分离。A/D转换电路如图2所示。

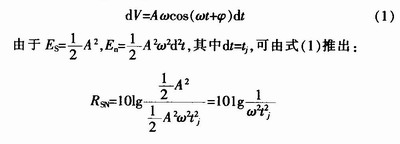

[url=]点击看原图[/url] 1.3 时钟电路 中频采样系统的时钟抖动会对系统性能产生很大影响,并且随着输入信号频率的增加,这种影响越来越明显。设输入信号V=Asin(ωt+ψ),采样时钟抖动为dt,信号能量为Es,噪声能量为En,则有:

2 系统硬件设计 2.1 A/D转换电路设计 采用AD9445作为A/D转换电路的核心器件.该器件是一款适用于中频采样的14位,单片集成A/D转换器。它采用3.3 V和5.0 V双电源供电,支持差分信号的时钟输入,支持CMOS、LVDS 2种数据输出格式。其重要引脚功能如下:DCS MODE:时钟占空周期稳定器控制引脚,该引脚为低电平时可以起到稳定时钟周期占空比的作用。

|

网友评论