英特尔发布全球最大容量的全新Stratix 10 GX 10M FPGA

发布时间:2019-11-6 14:34

发布者:eechina

|

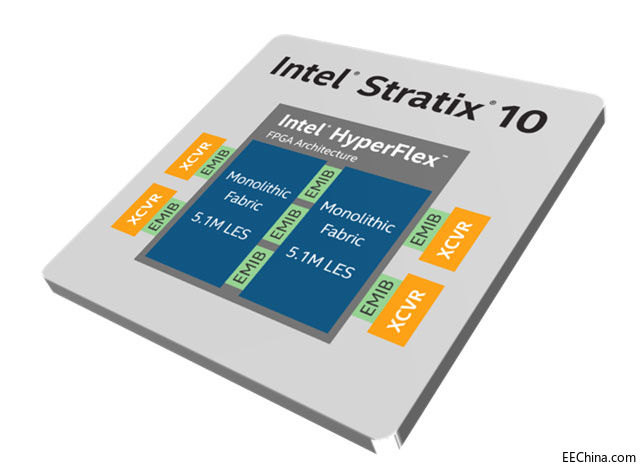

全新英特尔Stratix 10 GX 10M FPGA拥有 1020 万个逻辑单元,针对ASIC原型设计和仿真市场 本文作者:英特尔网络和自定义逻辑事业部副总裁兼FPGA 和电源产品营销总经理Patrick Dorsey 早前,多家客户已经收到全新英特尔Stratix 10 GX 10M FPGA样片,该产品是全球密度最高的FPGA,拥有1020 万个逻辑单元,现已量产。该款元件密度极高的FPGA,是基于现有的英特尔 Stratix 10 FPGA 架构以及英特尔先进的嵌入式多芯片互连桥接 (EMIB) 技术。其利用EMIB 技术融合了两个高密度英特尔 Stratix 10 GX FPGA 核心逻辑晶片(每个晶片容量为 510 万个逻辑单元)以及相应的 I/O 单元。英特尔 Stratix 10 GX 10M FPGA 拥有 1020 万个逻辑单元,其密度约为Stratix 10 GX 1SG280 FPGA 的 3.7 倍,后者为原英特尔 Stratix 10 系列中元件密度最高的设备。英特尔的 EMIB 技术只是多项 IC 工艺技术、制造和封装创新中的一项,正是这些创新的存在,让英特尔得以设计、制造并交付目前世界上密度最高(代表计算能力)的 FPGA。

英特尔 Stratix 10 GX 10M FPGA共有 1020 万个逻辑单元,是第一款使用 EMIB 技术将两个 FPGA构造晶片在逻辑和电气上实现整合的英特尔 FPGA ASIC原型设计和仿真市场对当前最大容量的FPGA需求格外急切。有数家供应商提供商用现成 (COTS) ASIC原型设计和仿真系统,对于这些供应商而言,能够将当前最大的 FPGA 用于 ASIC 仿真和原型设计系统中,就意味着获得了巨大的竞争优势。 此外,包括英特尔在内的很多大型半导体公司都开发了自定义原型设计和仿真系统,并在流片前使用该系统来验证自身最大规模、最复杂、风险最高的 ASSP 和 SoC 设计。ASIC 仿真和原型设计系统可以帮助设计团队大幅降低设计风险。因此,包括英特尔 Stratix 10 FPGA 和更早的 Stratix III、Stratix IV 和 Stratix V 设备在内的英特尔 FPGA,十多年来一直被用做很多仿真和原型设计系统的基础设备。 ASIC 仿真和原型设计系统支持很多与 IC 和系统开发相关的工作,包括: • 使用真实硬件的算法开发 • 芯片制造前的早期 SoC 软件开发 • RTOS 验证 • 针对硬件和软件的极端条件测试 • 连续设计迭代的回归测试 仿真和原型设计系统旨在帮助半导体厂商在芯片制造前发现和避免代价高昂的软硬件设计缺陷,从而节省数百万美元。芯片在制造完成后修复硬件设计缺陷的成本要高得多,通常需要昂贵的重新设计费用。当设备制造出来并交付给终端客户,解决这些问题的成本甚至会更高。正因为风险如此之高,且有可能节省的费用如此之多,这些原型设计和仿真系统为 IC 设计团队带来了实实在在的价值。仿真和原型设计系统的使用已经越来越普及,因为在经济风险如此之高的情况下,没有哪个设计团队负责人敢于忽视这项谨慎的验证性投资。 使用最大型的 FPGA,就能够在尽可能少的 FPGA 设备中纳入大型 ASIC、ASSP 和 SoC 设计。英特尔 Stratix 10 GX 10M FPGA是用于此类应用的一系列大型 FPGA 系列中的最新设备。该款全新的英特尔 Stratix 10 FPGA 支持仿真和原型设计系统的开发,适用于耗用亿级 ASIC 门的数字 IC 设计。包含 1020 万个逻辑单元的英特尔 Stratix 10 GX 10M FPGA,现已支持英特尔 Quartus Prime 软件套件。该套件采用新款专用 IP,明确支持 ASIC 仿真和原型设计。 英特尔 Stratix 10 GX 10M FPGA 是第一款使用 EMIB 技术并在逻辑和电气上将两个 FPGA 构造晶片结合到一起的英特尔 FPGA,实现高达 1020 万个逻辑单元密度。在该设备上,数万个连接通过多颗 EMIB 将两个 FPGA 构造晶片进行连接,从而在两个单片 FPGA 构造晶片之间形成高带宽连接。 以前,英特尔使用了 EMIB 技术将 I/O 和内存单元连接到 FPGA 构造晶片,从而实现了英特尔 Stratix 10 FPGA 家族的规模和种类不断扩张。例如,英特尔 Stratix 10 MX 设备集成了 8 GB 或 16 GB的 EMIB 相连的 3D 堆叠 HBM2 SRAM 单元。最近发布的英特尔 Stratix 10 DX FPGA 则集成了 EMIB 相连的 P tile,具备 PCIe 4.0 兼容能力。(参见“英特尔 Stratix 10 DX FPGA 是兼容 PCIe 4.0 的 PCI-SIG 系统集成设备清单中的第一个(也是唯一一个)FPGA。”) 英特尔 Stratix 10 DX FPGA 中使用的 P tile是兼容 PCIe 4.0 的 PCI-SIG 系统集成设备清单中的首款组件级设备。最近发布的英特尔 Agilex FPGA 中也同样紧密集成了同款 P tile,因而也能兼容 PCIe 4.0 设备。(请参阅“您当前是否需要 PCIe Gen 4 x16 1.0 版功能,并且完全符合 PCI-SIG 规范的FPGA?英特尔 Agilex FPGA 就能做到这一点。)英特尔 Stratix 10 DX 和英特尔 Agilex FPGA 中使用的 P tile是这一应用的又一绝佳范例,它展示了诸如EMIB的先进制造和生产技术,以及如何让英特尔将一系列新产品快速推向市场,并投入全面生产。 或许更重要的是,用来制造英特尔 Stratix 10 GX 10M FPGA 的半导体和封装技术,并不仅仅是为了制造世界上最大型的 FPGA,这只是一个附加值,尽管相当重要,但并不是最重点。 而重点在于: 这些技术让英特尔能够通过整合不同的半导体晶片,包括 FPGA、ASIC、eASIC 结构化 ASIC、I/O 单元、3D 堆叠内存单元和光子器件等,用于将几乎任何类型的设备整合到封装系统 (SiP) 中,以满足特定的客户需求。这些先进技术彼此结合,构成了英特尔独特、创新且极具战略性的优势。 |

网友评论