дЫЗХЕчдДШЅёюХдТЗДыЪЉ

ЗЂВМЪБМфЃК2011-3-1 10:33

ЗЂВМепЃКcircuit_share

ЙиМќДЪЃК

дЫЗХЕчдД

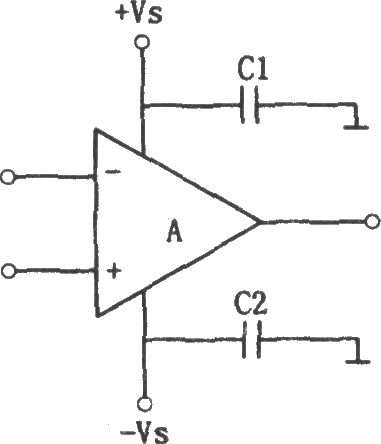

УПИіМЏГЩдЫЗХЕФЕчдДв§ЯпЃЌвЛАуЖМгІВЩгУШЅёюХдТЗДыЪЉЃЌМДДгЕчдДв§ЯпЖЫЕНЕиПчНгвЛИіИпадФмЕФЕчШнЃЌШчЭМЫљЪОЁЃЭМжаЕФИпЦЕХдТЗЕчШнЃЌЭЈГЃПЩбЁгУИпЦЕадФмгХСМЕФЬеДЩЕчШнЃЌЦфжЕдМЮЊ0.1ІЬFЁЃЛђВЩгУlІЬFЕФюуЕчШнЁЃетаЉЕчШнЕФФкЕчИажЕЖМНЯаЁЁЃдкдЫЗХЕФИпЫйгІгУЪБЃЌХдТЗЕчШнC1КЭC2гІНгЕНМЏГЩдЫЗХЕФЕчдДв§НХЩЯЃЌв§ЯпОЁСПЖЬЃЌетбљПЩвдаЮГЩЕЭЕчИаНгЕиЛиТЗЁЃЕБЫљЪЙгУЕФЗХДѓЦїЕФдівцДјПэГЫЛ§Дѓгк10MHzЪБЃЌгІВЩгУИќбЯИёЕФИпЦЕХдТЗДыЪЉЃЌДЫЪБгІбЁгУЩфЦЕХдТЗЕчШнЃЌШч0.1ІЬFдВЦЌЬеДЩЕчдкЃЌЭЌЪБУПИігЁЫЂАхЛђУП4ЁЋ5ИіМЏГЩаОЦЌдйдіМгвЛЖд(C1КЭC2)юуЕчШнЁЃЖдгкЭЈгУМЏГЩаОЦЌЃЌЖдХдТЗЕФвЊЧѓВЛИпЃЌЕЋвВВЛФмКіЪгЃЌЭЈГЃзюКУУП4ЁЋ5ИіЦїМўМгвЛЬзХдТЗЕчШнЁЃВЛТлЫљгУМЏГЩЕчТЗЦїМўгаЖрЩйЃЌУПИігЁЫЂАхЖМвЊжСЩйМгвЛЬзХдТЗЕчШнЁЃ |

ЭјгбЦРТл