技术参数详解,MOS管知识最全收录!

发布时间:2019-3-21 14:31

发布者:xunavc

|

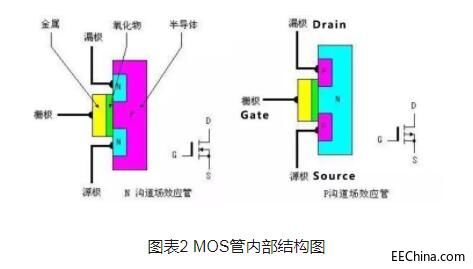

MOS管,即金属(Metal)—氧化物(Oxide)—半导体(Semiconductor)场效应晶体管,是一种应用场效应原理工作的半导体器件;和普通双极型晶体管相比,MOS管具有输入阻抗高、噪声低、动态范围大、功耗小、易于集成等优势,在开关电源、镇流器、高频感应加热、高频逆变焊机、通信电源等高频电源领域得到了越来越普遍的应用。 MOS管的种类及结构 MOS管是FET的一种(另一种为JFET结型场效应管),主要有两种结构形式:N沟道型和P沟道型;又根据场效应原理的不同,分为耗尽型(当栅压为零时有较大漏极电流)和增强型(当栅压为零,漏极电流也为零,必须再加一定的栅压之后才有漏极电流)两种。因此,MOS管可以被制构成P沟道增强型、P沟道耗尽型、N沟道增强型、N沟道耗尽型4种类型产品。 每一个MOS管都提供有三个电极:Gate栅极(表示为“G”)、Source源极(表示为“S”)、Drain漏极(表示为“D”)。接线时,对于N沟道的电源输入为D,输出为S;P沟道的电源输入为S,输出为D;且增强型、耗尽型的接法基本一样。 从结构图可发现,N沟道型场效应管的源极和漏极接在N型半导体上,而P沟道型场效应管的源极和漏极则接在P型半导体上。场效应管输出电流由输入的电压(或称场电压)控制,其输入的电流极小或没有电流输入,使得该器件有很高的输入阻抗,这也是MOS管被称为场效应管的重要原因。

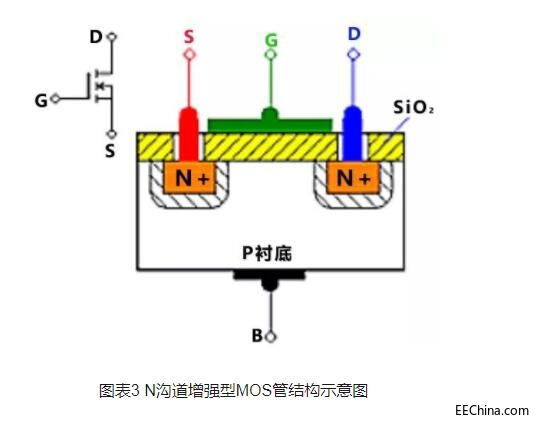

MOS管工作原理 1N沟道增强型场效应管原理 N沟道增强型MOS管在P型半导体上生成一层SiO2薄膜绝缘层,然后用光刻工艺扩散两个高掺杂的N型区,从N型区引出电极(漏极D、源极S);在源极和漏极之间的SiO2绝缘层上镀一层金属铝作为栅极G;P型半导体称为衬底,用符号B表示。由于栅极与其它电极之间是相互绝缘的,所以NMOS又被称为绝缘栅型场效应管。

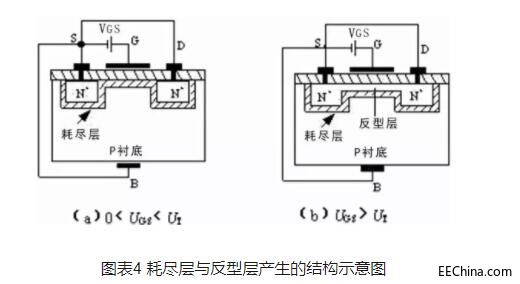

当栅极G和源极S之间不加任何电压,即VGS=0时,由于漏极和源极两个N+型区之间隔有P型衬底,相当于两个背靠背连接的PN结,它们之间的电阻高达1012Ω,即D、S之间不具备导电的沟道,所以无论在漏、源极之间加何种极性的电压,都不会产生漏极电流ID。 当将衬底B与源极S短接,在栅极G和源极S之间加正电压,即VGS>0时,如图表3(a)所示,则在栅极与衬底之间产生一个由栅极指向衬底的电场。在这个电场的作用下,P衬底表面附近的空穴受到排斥将向下方运动,电子受电场的吸引向衬底表面运动,与衬底表面的空穴复合,形成了一层耗尽层。 如果进一步提高VGS电压,使VGS达到某一电压VT时,P衬底表面层中空穴全部被排斥和耗尽,而自由电子大量地被吸引到表面层,由量变到质变,使表面层变成了自由电子为多子的N型层,称为“反型层”,如图表3(b)所示。 反型层将漏极D和源极S两个N+型区相连通,构成了漏、源极之间的N型导电沟道。把开始形成导电沟道所需的VGS值称为阈值电压或开启电压,用VGS(th)表示。显然,只有VGS>VGS(th)时才有沟道,而且VGS越大,沟道越厚,沟道的导通电阻越小,导电能力越强;“增强型”一词也由此得来。 在VGS>VGS(th)的条件下,如果在漏极D和源极S之间加上正电压VDS,导电沟道就会有电流流通。漏极电流由漏区流向源区,因为沟道有一定的电阻,所以沿着沟道产生电压降,使沟道各点的电位沿沟道由漏区到源区逐渐减小,靠近漏区一端的电压VGD最小,其值为VGD=VGS-VDS,相应的沟道最薄;靠近源区一端的电压最大,等于VGS,相应的沟道最厚。 这样就使得沟道厚度不再是均匀的,整个沟道呈倾斜状。随着VDS的增大,靠近漏区一端的沟道越来越薄。 当VDS增大到某一临界值,使VGD≤VGS(th)时,漏端的沟道消失,只剩下耗尽层,把这种情况称为沟道“预夹断”,如图表4(a)所示。继续增大VDS[即VDS>VGS-VGS(th)],夹断点向源极方向移动,如图表4(b)所示。 尽管夹断点在移动,但沟道区(源极S到夹断点)的电压降保持不变,仍等于VGS-VGS(th)。因此,VDS多余部分电压[VDS-(VGS-VGS(th))]全部降到夹断区上,在夹断区内形成较强的电场。这时电子沿沟道从源极流向夹断区,当电子到达夹断区边缘时,受夹断区强电场的作用,会很快的漂移到漏极。 2P沟道增强型场效应管原理 P沟道增强型MOS管因在N型衬底中生成P型反型层而得名,其通过光刻、扩散的方法或其他手段,在N型衬底(基片)上制作出两个掺杂的P区,分别引出电极(源极S和漏极D),同时在漏极与源极之间的SiO2绝缘层上制作金属栅极G。其结构和工作原理与N沟道MOS管类似;只是使用的栅-源和漏-源电压极性与N沟道MOS管相反。 在正常工作时,P沟道增强型MOS管的衬底必须与源极相连,而漏极对源极的电压VDS应为负值,以保证两个P区与衬底之间的PN结均为反偏,同时为了在衬底顶表面附近形成导电沟道,栅极对源极的电压也应为负。 当VDS=0时。在栅源之间加负电压比,由于绝缘层的存在,故没有电流,但是金属栅极被补充电而聚集负电荷,N型半导体中的多子电子被负电荷排斥向体内运动,表面留下带正电的离子,形成耗尽层。

随着G、S间负电压的增加,耗尽层加宽,当VDS增大到一定值时,衬底中的空穴(少子)被栅极中的负电荷吸引到表面,在耗尽层和绝缘层之间形成一个P型薄层,称反型层,如图表6(2)所示。 这个反型层就构成漏源之间的导电沟道,这时的VGS称为开启电压VGS(th),达到VGS(th)后再增加,衬底表面感应的空穴越多,反型层加宽,而耗尽层的宽度却不再变化,这样我们可以用VGS的大小控制导电沟道的宽度。 当VDS≠0时。导电沟道形成以后,D、S间加负向电压时,那么在源极与漏极之间将有漏极电流ID流通,而且ID随VDS而增,ID沿沟道产生的压降使沟道上各点与栅极间的电压不再相等,该电压削弱了栅极中负电荷电场的作用,使沟道从漏极到源极逐渐变窄,如图表7(1)所示。

当VDS增大到使VGD=VGS(即VDS=VGS-VGS(TH)),沟道在漏极附近出现预夹断,如图表7(2)所示。再继续增大VDS,夹断区只是稍有加长,而沟道电流基本上保持预夹断时的数值,其原因是当出现预夹断时再继续增大VDS,VDS的多余部分就全部加在漏极附近的夹断区上,故形成的漏极电流ID近似与VDS无关。

MOS管DMN2500UFB4-7 http://www.dzsc.com/ic-detail/9_5148.html资料 标准包装: 3,000 系列: - FET 型: MOSFET N 通道,金属氧化物FET 特点: 逻辑电平门漏极至源极电压(Vdss): 20V 电流 - 连续漏极(Id) @ 25° C: 810mA 开态Rds(最大)@ Id, Vgs @ 25° C: 400 毫欧 @ 600mA,4.5VId 时的 Vgs(th)(最大): 1V @ 250?A闸电荷(Qg) @ Vgs: 0.74nC @ 4.5V 输入电容 (Ciss) @ Vds: 60.67pF @ 16V 功率 - 最大: 460mW 安装类型: 表面贴装 封装/外壳: 3-XFDFN 供应商设备封装: 3-X2-DFN1006 包装: 剪切带 (CT) 其它名称: DMN2500UFB4-7DICT 安装方式:smd / SMT 包装/案例:X2 dfn1006 3 通道数:1通道 极性晶体管的N沟道: VDS漏源击穿电压V:20 ID的连续漏电流:810马 RDS是漏源电阻:700 mohms VGS的n次栅源电压门限值:1 V VGS栅源电压V 6: 门电荷Qg:736.6 PC 最低操作温度:55℃ 最大操作温度:150℃+ PD的功率dissipation:460 MW 配置:单 沟道增强模式: 包装:剪纸定案 包装:mousereel 包装:内卷筒 系列:dmn25 1型晶体管的N沟道: 品牌:光源公司 cnhts:8541210000 高温超导8541210095代码: mxhts:85412101 产品类型:MOSFET 厂包数量:3000 subcategory:mosfets 塔里克:8541210000

|

网友评论