БЅХЏЫМНјВНЃКжкNORЩСДцаОЦЌГЇЩЬПЊЪМЩ§МЖаОЦЌжЦГЬЙЄве

ЗЂВМЪБМфЃК2011-2-21 22:48

ЗЂВМепЃК1770309616

ЫцзХNORЩСДцЪаГЁЙЉашЦНКтЬЌЪЦЕФж№ВНзЊКУЃЌжївЊЕФМИМвNORЩСДцГЇЩЬвВвбОНЋжиаФДгМлИёеНзЊвЦЕНСЫЬсЩ§ВњЦЗжЦГЬЕШМЖЗНУцЁЃNORЩСДцжївЊГЇЩЬжЎвЛЕФ SpansionАкЭбСЫШЅФъЮхдТЗнЕФЦЦВњжизщЗчВЈЃЌЫћУЧМЦЛЎНёФъВЩгУ65nmжЦГЬЙЄвеЩњВњздМКЕФВњЦЗЃЌВЂдЄМЦНёФъздМКЕФетжжаТЩСДцЯњСПЛсгаЫљдіГЄЃЌдЄМЦНё ФъЕзЦф65nmжЦГЬВњЦЗЕФгЊЪеНЋеМзмгЊЪеЕФ25%зѓгвЁЃЫћУЧзюНќНЋЦфGL-SЯЕСаNORЩСДцВњЦЗЕФЪаГЁЗЖЮЇЭиПэЕНСЫАќРЈЦћГЕЃЌЯћЗбЕчзгвдМАгЮЯЗЛњгУЕФЧЖШы ЪНСьгђЃЌИУЯЕСаNORЩСДцВњЦЗОЭЪЧЪЙгУ65nmжЦГЬММЪѕжЦдьЁЃ

СэвЛМвNORЩСДцГЇЩЬЬЈЭхЭњКъдђМЦЛЎгкФъФкНЋЦфNORВњЦЗЧЈвЦЕН75nmжЦГЬНкЕуЃЌдйЯТвЛВНдђЛсзЊЛЛЕН57nmжЦГЬНкЕуЁЃЯрБШжЎЯТЃЌШЅФъЕкЫФМОЖШВЩгУ110nmжЦГЬЙЄвежЦзїЕФNORЩСДцВњЦЗЕФЯњСПдђеМЕНЭњКъNORЩСДцзмЯњСПЕФ57%ЁЃ ЛЊАюдђДЫЧАвВвбОЭИТЖСЫНёФъЕкШ§МОЖШНЋЦфNORЩСДцВњЦЗДг90nmжЦГЬНкЕуЬсЩ§ЕН58nmНкЕуЕФМЦЛЎЁЃ СэЭтЃЌОнДЫЧАЕФБЈЕРЯдЪОЃЌЭњКъгыЛЊАюСНМвЙЋЫОЖММЦЛЎгкНёФъдіЧПЦфNORВњЦЗдкЦћГЕЧЖШыЪНЪаГЁЕФЭЖЗХСІЖШЁЃ ИНвЛЃК NORЩСДцаОЦЌжЦдьЩЬМгЫйжЦдьЙЄвеЩ§МЖ ЬЈЭхУНЬхБЈЕРЃЌЮЊСЫШУNORЩСДцЪаГЁЙЉашИќМгЦНКтЃЌвЕНчжївЊNORаОЦЌжЦдьЩЬЖМвбОНЋжиЕуЗХдкСЫВњЦЗЙЄвеЩ§МЖЩЯЃЌЖјЗЧМлИёОКељЩЯЁЃ ИеИедкНёФъ5дТЗнзпГіЦЦВњБЃЛЄЕФSpansionвбОМЦЛЎНЋЦфаОЦЌжЦдьЙЄвеЩ§МЖЕН65nmЃЌВЂдЄМЦИУЙЄвеВњЦЗНЋеМОнЦфНёФъзмгЊЪеЕФ25%ЁЃ SpansionвЛжБЯыНЋЦфДЫЧАЦЦВњЪБЦкЖЊЕєЕФЗнЖювЛОйФУЛиЃЌЫћУЧвбОдкНќЦкНЋЦфгУгкЯћЗбЕчзгЦЗЁЂгЮЯЗКЭЦћГЕЕШЧЖШыЪНгІгУЕФGL-SМвзхNORЩСДцаОЦЌНјааРЉГфЃЌаТВњЦЗвВЪЙгУСЫ65nmДІРэЙЄвеЁЃ ЬЈЭхЭњКъвВМЦЛЎдкНёФъНЋЦфNORЩњВњЙЄвеДг0.11ЮЂУзЩ§МЖЕН75nmЃЌШЛКѓдйжБНгЩ§МЖЕН57nmЃЌ0.11ЮЂУзВњЦЗвбОеМОнЭњКъШЅФъЫФМОЖШNORЩСДцЪеШыЕФ57%ЁЃ ЛЊАюЕчзгДЫЧАвВвбОаћВММЦЛЎдкНёФъШ§МОЖШНЋЦфNORЩњВњДг90nmЩ§МЖЕН58nmЁЃДЫЭтЭњКъКЭЛЊАюЕчзгЛЙМгзуТэСІзМБИЬсЩ§ЦфЦћГЕNORЪаГЁЕФБэЯжЁЃ ИНЖўЃК Made in ChinaЃКДѓТНжаЮЂАыЕМЬхЩшБИЙЋЫОгћГхГібЧжозпЯђЪРНч ПЫЗўСЫЙЋЫОЗЂеЙЕРТЗЩЯЕФМИИіжївЊеЯАжЎКѓЃЌДѓТНжаЮЂАыЕМЬхЩшБИгаЯоЙЋЫО(AMEC)жегкзпЩЯСЫаТЕФГЩГЄТЗГЬЃЌжаЮЂАыЕМЬхЩшБИгаЯоЙЋЫОжївЊЕФВњЦЗЪЧАыЕМЬхжЦ дьгУЪДПЬЩшБИвдМАHPCVDИпбЙЛЏбЇЦјЯрГСЛ§ЩшБИЁЃЫћУЧЯждкПЊЪМбАЧѓдкбЧжовдЭтЕиЧјЕФЗЂеЙПеМфЃЌВЛНіШчДЫЃЌЙЋЫОвВЖдЩшБИЕФВњФмНјааСЫРЉГфЃЌВЂМЦЛЎРЉдівЛЬѕ аТЕФЩшБИВњЯпЃЌвдНјвЛВНЙЎЙЬЦфдкЪДПЬЩшБИСьгђЕФЕиЮЛЁЃЙЋЫОЛЙзМБИдкВЛОУЕФНЋРДЪзДЮЗЂааЙЩЦБЁЃ

жаЮЂАыЕМЬхЩшБИгаЯоЙЋЫОзмВПЮЛгкЩЯКЃЃЌФПЧАЮЊжЙетМвЙЋЫОвбОЪлГіСЫ20ЬЈАыЕМЬхЩњВњгУЩшБИЁЃВЛЙ§AMECЙЋЫОЕФИБзмВУFrank MasciocchiдђОмОјЭИТЖЦфПЭЛЇЕФУћЕЅЃЌНіГЦЦфПЭЛЇвбОНјШыЁАЕкЖўТжЁБГЩГЄЦкЃЌВЂГЦЁАЮвУЧвбОВЛдйЪЧГѕЩцЪаГЁЕФаТаЫЙЋЫОЁБЁЃОнЙлВьМвВТВтЃЌЙЋЫОЕФПЭЛЇУћЕЅжаКмПЩФмАќКЌгаGlobalfoundriesЕШжЊУћГЇЩЬЁЃ жаЮЂАыЕМЬхЩшБИЙЋЫОГЩСЂгк2004ФъЃЌ2007ФъЃЌетМвЙЋЫОЯШКѓЭЦГіСЫЗДгІРызгПЬЪДЛњКЭИпбЙЛЏбЇЦјЯрГСЛ§ЩшБИЃЈHPCVDЃЉзїЮЊздМКЕФДІХЎзїЃЌЙЋЫОЯЃЭћМгШыгыРЯХЦЩшБИГЇЩЬШчгІгУВФСЯЙЋЫО/ШеСЂЙЋЫО/TELЙЋЫО/ЗКСжЙЋЫОЃЈLamЃЉЕФОКељааСаЁЃ 2006ФъвдКѓЃЌжаЮЂЯШКѓГЩЙІДгАќРЈШ§аЧЗчЯеЭЖзЪЙЋЫОЃЌИпЭЈЕШдкФкЕФЖрМвЙЋЫО/ЭЖзЪЛњЙЙЛёЕУСЫОоЖюзЂзЪЁЃВЛЙ§ЃЌжаЮЂЕФЗЂеЙРњГЬВЂЗЧвЛЗЋЗчЫГЃЌ2007Фъ10дТЃЌРЯХЦАыЕМЬхЩшБИГЇЩЬгІгУВФСЯЙЋЫОвЛжНЫпзДНЋAMECИцЩЯСЫУРЙњМгжнББЧјЗЈЭЅЃЌжИПиAMECЗЧЗЈЕСгУЩЬвЕЛњУмЃЌЮЅЗДКЯдММАВЛе§ЕБОКељЃЌжИПиЕФУЌЭЗЩѕжСжИЯђСЫAMECЕФCEO вќжО

ЃвќжОвЂ1991ФъжС2004ФъМфдјдкгІгУАыЕМЬхЙЋЫОЕЃШЮЖржжжАЮЛЃЌШчЪДПЬВњЦЗМЏЭХЕФзмОРэЕШЁЃ 2009ФъЃЌAMECдкЗЧЗЈЕСгУЩЬвЕЛњУмАИЕФЩѓРэЙ§ГЬжаЛёЕУСЫгаРћЕФНсАИХаОіЃЌ2010ФъЃЌСНМвЙЋЫООЭетЦ№ЙйЫОДяГЩКЭНтЁЃ

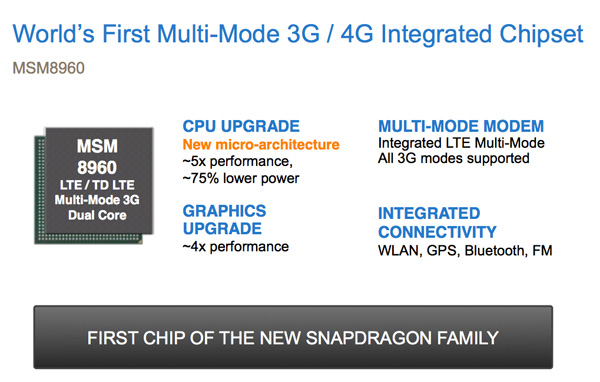

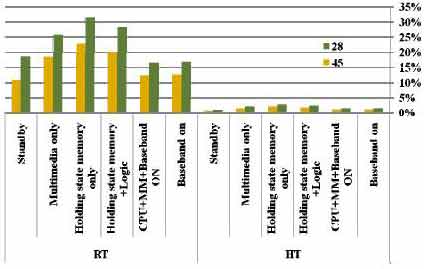

ЩЯИідТЃЌAMECаћГЦздМКгжгРДСЫвЛГЁЙйЫОЕФЪЄРћЁЃетГЁЙйЫОЪЧгЩУРЙњЗКСжЙЋЫОдкЬЈЭхЗЈдКЬсЦ№ЕФЃЌЫпзДаћГЦAMECЯњЭљЬЈЭхЕФЪДПЬЩшБИЧжЗИСЫЗКСжЕФММЪѕзЈРћЃЌзюКѓетЯюЩЯЫпдтЕНЬЈЭхЗЈдКЕФВЕЛиЃЌЖјЧвЬЈЭхжЧЛлВЦВњОжЃЈTIPOЃЉвВзюжееОдкСЫAMECЕФвЛБпЁЃ ЯждкAMECжегкжиеёЪаГЁУћЩљЃЌЖјОЁЙмвђЪмЕНЫпЫЯАИЕФИЩШХЃЌЙЋЫОвРШЛдкЪаГЁЭиеЙЗНУцШЁЕУСЫвЛаЉГЩаЇЃЌЦфГЩаЇжївЊдкЪДПЬВњЦЗЗНУцЁЃЙЋЫОЩњВњЕФ300mm Primo D-RIEЯЕЭГЃЈШЅёюЗДгІРызгПЬЪДЃЉЛљгкЫЋЙЄзїеОЃЌаЁХњСПдьаЭМЏШКЃЈmini-batch clusterЃЌmini-batchжИУПХњЩњВњЕФОЇдВВЛГЌЙ§ЪЎЦЌЃЉМмЙЙЃЌЮЊЕЅаОЦЌЩњВњЯЕЭГЃЌзАБИЩѕИпЦЕШЅёюЗДгІРызгПЬЪДдДЁЃетЬзЩшБИжївЊгУгкЪДПЬгВжЪбкФЄ(Hardmask)ЃЌВрБк(spacer)ЃЌЫЋДѓТэЪПИяЙ§ПзЃЈ dual damascene viaЃЉвдМАЙЕВл(trench)ЕШНсЙЙЕФЪДПЬГЩаЭЃЌПЩЪЪгУгк65nmвдЩЯЕШМЖЕФаОЦЌЩњВњЁЃAMECздГЦетЬзЩшБИЕФВњГіФмСІБШОКељЖдЪжЕФЯЕЭГИпГі35%зѓгвЃЌЖјЪЙгУГЩБОдђБШЖдЪжЕЭ35%ЁЃ ДѓВПЗжAMECЩњВњЕФЩшБИЪЧЯњЭљжаЙњДѓТНЃЌаТМгЦТвдМАЬЈЭхЕиЧјЃЌЖјЯждкЙЋЫОПЊЪМЯђХЗжоКЭУРЙњЕиЧјЭиеЙвЕЮёЁЃ AMECЙЋЫОЩњВњЕФЩшБИжївЊЛюдОдкЕчНщжЪЪДПЬЩњВњСьгђЃЌЫћУЧГѕЦкЩњВњЕФЩшБИЛљБОБЛгУгкАыЕМЬхЦїМўжаЗЧЙиМќВуЕФЪДПЬГЩаЭЃЌВЛЙ§AMECЕФаТФПБъЪЧНЋЦфЪДПЬЙЄОпгІгУЕФФПБъЭЦЙуЕНАыЕМЬхЦїМўжаИќЮЊЙиМќЕФВуНсЙЙЕФЪДПЬжаШЅЃЌЭЌЪБХЌСІНјШыаТаЫЕФTSVДЉЙшЛЅСЊММЪѕгУЩњВњЩшБИЪаГЁЁЃ СэЭтЃЌЙЋЫОЛЙПЊЗЂСЫДњКХЮЊA-RIEЕФаТЩшБИЃЌФПЧАетПюЩшБИЕФЯИНкЮДжЊЃЌВЛЙ§AMECГЦЩшБИЕФВњГіСПЯрБШD-RIEНЋЪЕЯжБЖдіЁЃЕННёФъ10дТЗнЃЌAMECНЋОпБИФъВњ170ЬЈЩшБИЕФФмСІЁЃ ИНШ§ЃК ДњКХRogue ШЋаТPowerVR 6вЦЖЏGPUМмЙЙЙЋВМ РДздЙњЭтУНЬхЕФБЈЕРЃЌARMКЭIntelжївЊЕФGPU IPжївЊЙЉгІЩЬImagination TechnologiesНќШеЙЋВМСЫЫћУЧаТвЛДњPowervr Series6МмЙЙЃЌДњКХЮЊЁАRogueЁБЃЌST-EricssonвбОаћВМНЋЛсдкЫћУЧЕФаТвЛДњNovaгІгУДІРэЦїжаЪЙгУетвЛаТЕФЭМаЮМмЙЙЁЃ етМвЙЋЫОЕФЭМаЮММЪѕдкЦЛЙћЁЂЕТжнвЧЦїЁЂЗЩЫМПЈЖћЁЂIntelЁЂШ§аЧЁЂNECЕШЙЋЫОЕФДІРэЦїВњЦЗжаЖМЕУЕНСЫДѓСПЕФгІгУЃЌБШШчЦЛЙћЕФЕквЛДњiPhoneОЭЪЙгУСЫЫћУЧЕФPowervr MBXЭМаЮКЫаФЁЃ Imagination TechnologiesБэЪОЫћУЧЕФаТвЛДњPowervrМмЙЙНЋЛсЙуЗКМцШнЯжгаЕФSeries5ЯЕСаВњЦЗЃЌвдШЗБЃгІгУГЬађПЊЗЂПЩвдЦНЛЌЙ§ЖЩЕНаТЕФМмЙЙЃЌВЛ Й§ЫћУЧВЂЮДЭИТЖаТМмЙЙЕФЯъЯИВЮЪ§ЁЃгаУНЬхБЈЕРГЦЃЌSeries6 IPЕФдЫааЫйЖШЯрБШЯжгаЕФSeries5ЬсИпжСЩй20БЖЁЃ ЭЌЪБImagination TechnologieЛЙБэЪОЫћУЧЕФЭМаЮКЫаФгаЭћдк2011ФъЫцSoCЦЌЩЯЯЕЭГЯњГі2вквдЩЯЁЃФПЧАвбОгаГЌЙ§10Пюе§дкЩшМЦЛђепГібљЕФSoCЪЙгУЫћУЧзюаТ ЕФSeries5 IPЃЌЦфжаЕТжнвЧЦїЕФOMAP5430КЭOMAP5432жаМЏГЩгаЫћУЧЕФЖрКЫаФPowervr SGX544MPЭМаЮМгЫйЦїЃЌШ№ШјЕФSH-Mobile APE5RФкжУгаPowervr SGX543MPЃЌЫїФсЕФNGPдђЪЙгУЫћУЧЕФSGX543MP4ЭМаЮКЫаФЁЃДЫЭтгаДЋЮХГЦЃЌЯТвЛДњЕФiPhoneКЭiPadвВНЋЛсЪЙгУSGX543MP4ЭМаЮаОЦЌЁЃ ИНЫФЃК ДгГЩБОКЭММЪѕНЧЖШПДИпЭЈ28nmВњЦЗЮЊКЮЦњгУСїааЕФHKMGЙЄве ДѓМвЖМжЊЕРМИЬьЧАИпЭЈе§ЪНЗЂВМСЫЯжгаScorpionКЫаФЕФЯТвЛДњвЦЖЏЮЂДІРэЦїkraitВњЦЗЯЕСаЃЌетПюаТВњЦЗгЩгкНЯдчЕиВЩгУСЫ28nmжЦГЬЃЌвђДЫв§Ц№СЫ ИїЗНЕФзЂвтЁЃВЛЙ§ЃЌгыДѓМвЕФЦкЭћЯрЗДЃЌВЛОУЧАИпЭЈдјОдкIDEMДѓЛсЩЯБэЪОЦфДѓВПЗж28nmжЦГЬЕФВњЦЗВЂВЛЛсВЩгУЕБНёзюЯШНјЕФHKMGЃЈН№ЪєеЄМЋ+ИпНщЕч ГЃЪ§ОјдЕВуЃЈHigh-kЃЉеЄНсЙЙЃЉЙЄвежЦзїЃЌЖјЪЧШдВЩгУНЯЮЊДЋЭГЕФЖрОЇЙшеЄ+ЕЊбѕЛЏЙшОјдЕВуЃЈpoly/SiONЃЉЕФеЄМЋНсЙЙЃЌФЧУДИпЭЈЮЊЪВУДбЁдёетжж ПДЦ№РДВЛЙЛЁАЪБїжЁБЕФРЯММЪѕФиЃПЯждкЮвУЧОЭвЛЦ№РДЛиЙЫвЛЯТИпЭЈбЁдёетУДзіЕФРэгЩЁЃ

1.ГЩБОвђЫиЃК ИпЭЈЕФгЊдЫИБзмВУJim CliffordБэЪОЃЌбЁдёзпpoly/SiONЕФРЯТЗЃЌжївЊЪЧГігкГЩБОКЭЪБМфЗНУцЕФПМТЧЁЃЫћдкIEDMЛсвщЩЯГЦЃКЁАHigh-kОјдЕВуЬьЩњОЭашвЊИќЖрЕФбкФЄВуНсЙЙВХПЩвджЦзїГіРДЃЌЖјетжжНсЙЙЯрЖдИДдгЃЌКмШнвзВњЩњжЦдьшІДУЃЌЖджЦдьепЖјбдЪЧвЛИіЬєеНЁЃЁБ ВЛЙ§ИпЭЈВЂУЛгаЭъШЋЙиЩЯHKMGЕФУХЁЃCliffordБэЪОЃКЁАШдШЛгавЛВПЗжВњЦЗЪЧашвЊВЩгУHKMGММЪѕжЦзїЕФЁБетЦфжаАќРЈЮЊЦНАхЕчФдвдМАВПЗжЁАМЋИпЖЫЁБжЧФмЪжЛњЫљЩшМЦЕФаОЦЌВњЦЗЁЃИпЭЈЛсбЁдёдкДЫРрВњЦЗЕФдЫааЦЕТЪашвЊЬсИпЕН2GHzзѓгвЪБЃЌдйЯђетВПЗж28nmжЦГЬВњЦЗжав§ШыHKMGММЪѕЁЃВЛЙ§ЖдДѓЖрЪ§жЧФмЪжЛњгУаОЦЌЃЌИпЭЈдђЛсМсГжВЩгУИќБувЫЕФpoly/SiONММЪѕжЦзїаОЦЌЁЃ CliffordЛЙЧПЕїГЦЃЌЫфШЛИпЭЈЗЧГЃПЪЭћздМКЩшМЦЕФаОЦЌВњЦЗФмЙЛВЩгУИќЯШНјЕФЙЄвеРДжЦзїЃЌЕЋЪЧЮЊзЗж№ФІЖћЖЈТЩЖјБиаыЦєгУетаЉЙЄвеЫљашЕФШчEUVЙтПЬЩшБИвдМАЦфЫќЙиСЊММЪѕЕФбаОПЗНУцЕФОоЖюГЩБОЭЖзЪШДСюИпЭЈЪЎЗжЕЃгЧЁЃCliffordЫЕЃКЁАГЩБОПижЦЖдЮвУЧЖјбдЗЧГЃживЊЁЃЁБ 2.ММЪѕвђЫиЃК ДгММЪѕНЧЖШПДЃЌдкIEDMЛсеЙЦкМфЃЌИпЭЈММЪѕжїЙмP.R. ChidambaramдђдквЛЗнУшЪіЦф28nmММЪѕЕФЮФМўжаГЦЃЌШчЙћФГжжгУгкжЦзїHKMGЕФЙЄвеЮоЗЈЮЊЙЕЕРЬсЙЉзуЙЛЕФЙЕЕРгІБфСІЃЌФЧУДВЩгУетжжЙЄвежЦдьГіРДЕФОЇЬхЙмЦфадФмБуЮоЗЈБШВЩгУДЋЭГpoly/SiON+ЧПаЇЙЕЕРЙшгІБфЙЄвежЦзїЕФОЇЬхЙмИпГіЖрЩйЁЃЫћБэЪОЃКЁБHKMG+ЧПаЇЙЕЕРЙшгІБфЙЄвеЕФзщКЯПЩвдЯджјЬсЩ§ОЇЬхЙмЕФЫйЖШЃЌЕЋЪЧВЩгУетжжЙЄвеЕФГЩБОИќИпЃЌвђДЫетжжЙЄвеИќЪЪКЯгкгУдкЦНАхЕчФдЛђГЌИпЖЫжЧФмЪжЛњЕФГЁКЯЁЃЖјВЩгУДЋЭГЕФpoly/SiONЙЄвеЃЌдђВњЦЗПЊЗЂЪБМфЖЬЃЌЖјЧвжЦГЬЗНУцЫљИКЕЃЕФЗчЯевВИќаЁЃЌдьГіЕФаОЦЌшІДУУмЖШвВИќЕЭЁЃЁА ФПЧАДѓВПЗжВЩгУИпЭЈSnapdragonДІРэЦїКЫаФЩшМЦЕФжЧФмЪжЛњгУаОЦЌЕФдЫааЦЕТЪОљдк1GhzМАвдЯТЕФЫЎЦНЃЌЖјЧвЛЙПЩвдгУЦєгУЫЋКЫЩшМЦЕФЗНЗЈРДНјвЛВНЬсЩ§адФмЁЃИпЭЈЙЋЫОЕФИпМЖММЪѕОРэGeoff YeapГЦИпЭЈФПЧАЪлГіЕФЛљгкSnapdragonКЫаФЕФаОЦЌВњЦЗЁБЪ§СПЗЧГЃОоДѓЁАЃЌЫћЛЙБэЪОФПЧАжївЊМИМваОЦЌДњЙЄГЇдкhigh-kЙЄвеЗНУцЁБЖМЛЙзМБИВЛзуЁАЁЃ YeapБэЪОИпЭЈЭэаЉЪБКђЛсНЋЦфВПЗжВњЦЗзЊЯђЪЙгУHKMGЙЄвежЦзїЁЃЫфШЛHKMGОЇЬхЙмгЩгкЗДаЭВуЕчКЩЕФдіМгЦфЧ§ЖЏЕчСїжЕвВИќДѓЃЌЕЋЪЧвВвђДЫЖјдіМгСЫЙмзгЕФПЊЙиЕчШнЃЌЖјЖдИпЭЈЖјбдЃЌОЇЬхЙмЙЄзїдкЯпадЕчСїЬиадЧјЕФЕчСїЧ§ЖЏФмСІЃЈIdlinЃЉвЊБШЙЄзїдкБЅКЭЧјЕФЕчСїЧ§ЖЏФмСІЃЈIdsatЃЉИќЮЊживЊЁЃ

ЖјЫфШЛHKMGЙЄвеЖдНтОіеЄМЋЕФТЉЕчЮЪЬтАяжњЩѕДѓЃЌЕЋЪЧетжжММЪѕЖдЙшГФЕзЃЈsubstrateЃЉвдМАТЉдДМЋЕФТЉЕчШДУЛгаКмДѓЕФИФЩЦЁЃЖјИпЭЈдђдкЦфВЩгУ28nm poly/SiONЙЄвеЕФОЇЬхЙмжаВЩгУСЫкхЦЋжУММЪѕЃЈ well biasingЃЌвЛжжПЩвдИФБфГФЕзЦЋжУЕчбЙЃЌвдМѕаЁГФЕзТЉЕчЕФММЪѕЃЉЃЌвдМААќКЌУХПиЪБжг(clock gatingМђбджЎОЭЪЧдкФГФЃПщПеЯаЕФЪБКђПЩЧаЖЯЦфЪБжгаХКХЙЉгІЕФПижЦУХЕчТЗММЪѕ)КЭУХПиЕчдД(power gating МђбджЎМДЮЊдкФГОЇЬхЙмФЃПщПеЯаЕФЪБКђПЩГЙЕзЧаЖЯЦфЕчдДЙЉгІЕФПижЦУХЕчТЗММЪѕ)ЕШММЪѕдкФкЕФЖржжЕчТЗММЪѕРДПижЦаОЦЌЕФТЉЕчЫ№КФЁЃChidambaramЛЙНщЩмСЫИУВњЦЗжагІгУЕФФГжжЬиЪтЕФУХПиЕчдДЩшМЦЃЌВЂГЦетжжММЪѕЪЧдкИпЭЈКЭЦфЮДЭИТЖЙЋЫОУћЕФаОЦЌДњЙЄЛяАщЕФЙВЭЌХЌСІЯТПЊЗЂГіРДЕФЁЃ ЕБШЛЗХПЊHKMGЛЙЪЧpoly/SiONЕФЛАЬтВЛЬИЃЌЙтЪЧДг45nmНкЕуЩ§МЖЕН28nmНкЕуЃЌИпЭЈвВПЩвдДгжаЛёРћВЛЩйЃЌетВПЗжЯраХДѓМвЖМвбОКмЧхГўЃЌетРяОЭВЛдйТорТСЫЁЃ 3 ЭтНчЕФПДЗЈЃК дкIEDMЛсвщЩЯЃЌаэЖрММЪѕзЈМвЖМЮЊИпЭЈОіЖЈШдзпpoly/SiONЙЄвеТЗЯпЕФОіЖЈИаЕНОЊбШЃЌвђЮЊвЛАуЖМШЯЮЊHKMGПЩвдИќКУЕФПижЦЙЕЕРадФмЃЌЖјЧвЙЄвеЩ§МЖгрЕивВИќДѓЁЃзмЬхЩЯПДЃЌФПЧАpoly/SiONЙЄвегіЕНЕФжївЊеЯАЪЧеЄбѕЛЏВуЕФЕШаЇКёЖШгЩгкеЄМЋТЉЕчЕШЮЪЬтЕФДцдкДг90nmНкЕужЦГЬЦ№БуФбвдНјвЛВНЫѕаЁЃЌвджСгкашвЊвРРЕЙшгІБфММЪѕРДЬсЩ§ОЇЬхЙмЕФЫйЖШЃЌЖјHKMGдђПЩвдНтОіетИіЮЪЬтЁЃ 4 ЙигкИпЭЈ28nmВњЦЗДњЙЄЩЬЕФЭЦРэЗжЮіЃК жСгкИпЭЈетаЉ28nmВњЦЗПЩФмЕФДњЙЄЩЬЗНУцЃЌЬЈЛ§ЕчКЭGlobalFoundriesЖМгыИпЭЈгаДњЙЄКЯзїЙиЯЕЁЃЖјЮвУЧвбОжЊЕРЬЈЛ§ЕчНЋЦєгУШ§жжВЛЭЌЕФ28nmжЦГЬЙЄвеММЪѕЃЌетШ§жжжЦГЬЙЄвеЗжБ№ЪЧЃК1-ЁАЕЭЙІКФЕЊбѕЛЏЙшеЄМЋОјдЕВуЃЈSiONЃЉЙЄвеЁБЃЈДњКХ28LPЃЉЃЛ2-"High-K+Н№ЪєеЄМЋЃЈHKMGЃЉИпадФмЙЄвеЁАЃЈДњКХ28HPЃЉЃЛ3-ЁБЕЭЙІКФаЭHKMGЙЄвеЁАЃЈДњКХ28HPLЃЉЁЃЫљвдДгЬЈЛ§ЕчЕФЧщПіПДЦф28LPЙЄвее§КУТњзуИпЭЈ28nmВњЦЗЕФЙцИёЁЃ ЖјОнGlobalFoundriesДЫЧАЙЋВМЕФЙЄвеММЪѕТЗЯпЭМЯдЪОЃЌGlobalFoundriesЩњВњЕФ28nmЕЭЙІКФЃЈ28nm LPЃЉМАИпадФмЃЈ28nm HPЃЉаОЦЌВњЦЗОљЛсЪЙгУgate-first HKMGЙЄвеЃЌетбљЃЌГ§ЗЧGlobalFoundriesУЛЗнДњЙЄДѓВПЗжИпЭЈ28nmжЦГЬаОЦЌЃЌЗёдђИпЭЈзп28nm poly/SiONЙЄвеТЗЯпЕФОіЖЈЃЌВЛУтЛсСюШЫВТВтЫћУЧЛсВЛЛсЮЊИпЭЈетИіПЩвдЫузїДњЙЄГЇЩЬзюДѓПЭЛЇЕФКЯзїЛяАщЖјЖдздМКЕФЙЄвеММЪѕТЗЯпЭМзіаЉаоИФЁЃВЛЙ§CliffordБэЪОВЛдИЮЊФФМвГЇЩЬНЋДњЙЄЦф28nmаОЦЌВњЦЗзїШЮКЮЦРТлЃЌГЦДњЙЄЩЬЕФОпЬхШЫбЁЛЙдкФкВПЬжТлЕФЙ§ГЬжаЁЃ гаШЄЕФЪЧЃЌОЁЙмGlobalFoundriesЕФЗЂбдШЫдкIDEMЛсЩЯДѓЫСаћДЋГЦЦф28nmЙЄвеЪЧЛљгкgate-first HKMGЙЄвеЛљДЁЩЯЕФЃЌЕЋЫћгжБэЪОЃКЁАВЛЙ§ЃЌЮвУЧвВБОзХЬиЪТЬиАьЕФОЋЩёЃЌе§дкЮЊТњзуФГаЉРДздЬиЪтПЭЛЇЕФЬиЪтЧыЧѓЖјЮЊФГаЉЬиЪтВњЦЗЬсЙЉЛљгк28nm Poly/SiONжЦГЬЕФДњЙЄЃЌетРрВњЦЗВЂВЛашвЊHKMGММЪѕДјРДЕФадФмЬсЩ§КЭТЉЕчНЕЕЭгХЪЦЁЃЁБЖјЧвGlobalFoundriesвВВЛЛсЮЊ28 nm Poly/SiONММЪѕНЈСЂвЛећЬзЭъБИЕФЕчТЗЩшМЦЯЕЭГЁЃ ЫћЛЙБэЪОGlobalFoundriesзЊЯђHKMGЙЄвеЕФМЦЛЎЁАШдШЛдке§ГЃНјаажаЃЌЮвУЧШЯЮЊетжжЙЄвеЖдПЭЛЇЕФЮќв§СІЪЧЗЧГЃДѓЕФЁЃЮвУЧдЄМЦHKMGЛсГЩЮЊ28nmЕЭЙІКФвЦЖЏЩшБИгУВњЦЗЃЌвдМА28nmИпадФмЩшБИгУВњЦЗЕФОјЖджїСїЙЄвеЁЃЁБGlobalFoundriesЛЙГЦФПЧАвбОгаЖрМвПЭЛЇЕФаОЦЌВњЦЗДІгкЙшЦЌбщжЄНзЖЮЃЌЖјЧвЙЋЫОЦьЯТЕФЕТРлЫЙЖйFab1ЙЄГЇвВвбОдкВтЪдЯрЙиЕФдаЭаОЦЌЃЌКмПьБуЛсНјШыЪдВњНзЖЮЁЃ GlobalFoundriesгыЬЈЛ§ЕчФПЧАвђЫљгУHKMGЙЄвеЕФВЛЭЌЖјдкЪаГЁЩЯЛ№вЉЮЖКмХЈЃКGlobalFoundriesдк28nmЛсЪЙгУgate firstаЭHKMGЙЄвеЃЌЖјЬЈЛ§ЕчдђЛсЪЙгУGate-last HKMGЙЄвеЁЃGlobalFoundriesЛЙаћГЦздМКЕФGate first HKMGЙЄведкГЩБОЗНУцвЊБШЬЈЛ§ЕчЕФGate-last HKMGЙЄвеНкФмдМ10-15%зѓгвЁЃ зюКѓЃЌИпЭЈЕФИпЙмYeapБэЪОдкЯТвЛДњ22/20nmНкЕуЃЌИпЭЈМЦЛЎдкМИКѕздМКЕФЫљгааОЦЌВњЦЗжаЦєгУHKMGЙЄвеЁЃ ИНЮхЃК FinFETММЪѕЕьЛљШЫПДFinFETгыFDSOIММЪѕжЎељ 12ФъЧАЃЌКње§УїНЬЪкдкМгжнДѓбЇСьЕМзХвЛИігЩУРЙњЙњЗРВПИпМЖбаОПМЦЛЎОжЃЈDARPAЃЉГізЪдожњЕФбаОПаЁзщЃЌЕБЪБЫћУЧЕФбаОПФПБъЪЧCMOSММЪѕШчКЮЭиеЙЕН 25nmСьгђЃЌЕБЪБЕФбаОПНсЙћЯдЪОгаСНжжЭООЖПЩвдЪЕЯжетжжФПЕФЃКвЛЪЧСЂЬхаЭНсЙЙЕФFinFETОЇЬхЙмЃЌСэЭтвЛжжЪЧЛљгкSOIЕФГЌБЁОјдЕВуЩЯЙшЬхММЪѕ (UTB-SOI,вВОЭЪЧЮвУЧГЃЫЕЕФFDSOIОЇЬхЙмММЪѕ)ЁЃ

Кње§УїНЬЪкЪЧЬЈЛ§ЕчЕФЬиЦИНЬЪкЃЌЫћЛЙдјОЕЃШЮЙ§ЬЈЛ§ЕчЙЋЫОЕФЪзЯЏММЪѕЙйЃЌДЫЭтЫћЛЙЪЧжаПЦдКЭтМЎдКЪПЃЌЫћдкАыЕМЬхНчзюжјУћЕФГЩОЭЪЧбажЦГіСЫFinFETСЂЬхаЭОЇЬхЙмММЪѕЁЃ ВЛЙ§ЃЌвЊШУUTB-SOIе§ГЃЙЄзїЃЌОјдЕВуЩЯЙшФЄЕФКёЖШгІЯожЦдкеЄГЄЕФЫФЗжжЎвЛзѓгвЁЃЖд25nmеЄГЄЕФОЇЬхЙмЖјбдЃЌКњНЬЪкШЯЮЊUTB-SOIЕФЙшФЄКёЖШгІБЛПижЦдк5nmзѓгвЁЃ КњНЬЪкМАЦфЭХЖгГЩдБЗЂБэСЫгаЙиFinFET(1999ФъЗЂВМ)КЭUTB-SOI(2000ФъЗЂВМ)ЕФММЪѕЮФеТКѓЃЌДѓВПЗжАыЕМЬхГЇЩЬЕФПЊЗЂЙЄзїЗНЯђзЊЯђСЫFinFETММЪѕЃЌвђЮЊЫћУЧЖМШЯЮЊвЊЯыжЦдьГіUTB-SOIЩЯШчДЫБЁЕФЙшФЄЪЕдкЬЋРЇФбСЫЁЃ КњНЬЪкЫЕЃКЁАЮвЕБЪБОѕЕУЮвУЧПжХТУЛгаАьЗЈИуЕНПЩвдТњзуетжжЬѕМўЕФSOIЛљЬхЃЌУЛгаЙЋЫОФмЙЛЖдЭтЙЉгІЙшФЄКёЖШНіга5nmЃЈ50АЃЃЌНіЯрЕБ12-15ИіЙшдзгЕФГпДчЃЉЕФSOIОЇдВЁЃЮвЕБЪБОѕЕУетВЛЬЋПЩФмЪЕЯжЃЌЛђепЫЕЕШШЫУЧОпБИетжжММЪѕФмСІЪБЃЌFinFETММЪѕПЩФмвбОЕУЕНСЫГфЗжЕФЗЂеЙЁЃВЛЙ§СНФъЧАЗЈЙњSoitecЙЋЫОИФБфСЫетжжЧщПіЃЌЫћУЧПЊЪМЭЦГі300mm UTB-SOIЕФОЇдВбљЦЗЃЌетаЉОЇдВЕФЖЅВуЙшФЄдЪМКёЖШжЛга12nmЃЌШЛКѓдйОДІРэШЅЕєЖЅВПЕФ7nmКёЖШЙшФЄЃЌзюКѓБуПЩЕУЕН5nmКёЖШЕФЙшФЄЁЃетБуЮЊUTB-SOIММЪѕЕФЪЕгУЛЏЦЬЦНСЫЕРТЗЁЃЁБ КњНЬЪкШЯЮЊЃЌFinFETКЭUTB-SOIММЪѕЪЧПЩвдВЂДцЕФЃЌВЛЙ§дкЮДРДМИФъФкЃЌСНепЖМЛсЯыОЁАьЗЈБЫДЫГЌдНЖдЗНГЩЮЊжїСїММЪѕЁЃЦфжаIntelгаПЩФмЛсВЩгУFinFETММЪѕЃЌдвђЪЧетжжММЪѕПЩвдШУЮЂДІРэЦїЕФадФмЯрЖдИќЧПЁЃ ЫћЫЕЃКЁАЮвОѕЕУСНжжММЪѕжСЩйдкЗЂеЙЕФГѕЦкЛсВЂМнЦыЧ§ЃЌFinFETММЪѕе§дкСПВњЛЏЕФНјГЬжаЁЃЖдIntelЖјбдЃЌUTB-SOIММЪѕжЦдьЕФЦїМўПЩФмЫйЖШЩЯВЛЙЛПьЃЌвђДЫЮвУЧМйЩшIntelПЩФмЛсЪЙгУFinFETММЪѕЁЃЖдЬЈЛ§ЕчЖјбдЃЌдкСНжжММЪѕжаЫћУЧЛсЪзЯШВЩгУFinFETММЪѕЃЌБЯОЙЫћУЧдкДЫЗНУцвбОНјааСЫДѓСПЕФПЊЗЂЭЖзЪЃЌЖјЧвЬЈЛ§ЕчгаДѓСПFinFETЪЪгУЕФгІгУЃЌИпадФмгІгУБуЪЧЦфжажЎвЛЁЃЁБ ВЛЙ§UTB-SOIдђдкбаЗЂИДдгадЩЯИќгагХЪЦ(вђUTB-SOIШдПЩВЩгУДЋЭГЕФЦНУцаЭОЇЬхЙмММЪѕЃЌЖјFinFETдђЪЧСЂЬхОЇЬхЙмММЪѕ)ЁЃЁАЮвШЯЮЊUTB-SOIНЋРДЛсгаЪаГЁЃЌвђЮЊетжжММЪѕЕФИДдгГЬЖШвЊЕЭгкFinFET.аОЦЌжЦдьЙЋЫОжЛашвЊТђРДUTB-SOIОЇдВМДПЩЁЃЖдЦЕТЪвЊЧѓНЯЕЭЕФЕЭЙІКФаЭгІгУЃЌUTB-SOIММЪѕНЋЪЧвЛИігаШЄЕФаТбЁдёЁЃЁБ ЪБМфЗНУцЃЌЫћШЯЮЊЬЈЛ§ЕчЙЋЫОЛсдк14nmНкЕуПЊЪМВЩгУFinFETММЪѕЃЌШЛКѓдђЛсЮЊЕЭЙІКФВњЦЗЕФгУЛЇЭЦГігІгУСЫUTB-SOIММЪѕЕФВњЦЗЁЃЖјСЊЕчЙЋЫОдђЛсМѕЧсЖдFinFETММЪѕЕФЭЖзЪСІЖШЃЌВЂжБНгзЊЯђUTB-SOIММЪѕЁЃ ЫћЛЙЫЕЃКЁАЖдЯТвЛДњАыЕМЬхаОЦЌВњЦЗЖјбдЃЈетРяжИ22/20nmНкЕужЎКѓЕФЯТвЛДњЃЉЃЌFinFETКЭUTB-SOIОљЛсгаздМКЕФгУЮфжЎЕиЁЃВЛЙ§СНепНЋГЪЯжЫЎЛ№ФбШнЕФОКељЬЌЪЦЁЃЖјГ§ЗЧUTB-SOIПЩвдДяЕННЯИпЕФадФмБэЯжЃЌЗёдђЮоЗЈЛїАмFinFETММЪѕЁЃВЛЙ§ЖдаэЖраОЦЌжЦдьЙЋЫОЖјбдЃЌШдПЩевЕНЪЪгУUTB-SOIММЪѕЕФаэЖргІгУЁЃЫљвдЮвШЯЮЊетСНжжММЪѕЖМгаПЩФмЪЕЯжВЂгЕгаИїздЕФЪаГЁЃЌЖјЧвдкЮДРДвЛГЄЖЮЪБМфФкЃЌСНжжММЪѕЛсГЄЦкВЂДцЃЌВЛЙ§ЮвОѕЕУетЪЧИіКУЯжЯѓЃЌжСЩйЮвУЧЯждкгаСЫПЩбЁдёЕФгрЕиЁЃЁБ |

ЭјгбЦРТл