гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди90ЃКFPGAЦЌФкROM FIFO RAMСЊКЯЪЕР§

ЗЂВМЪБМфЃК2018-9-7 22:22

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди90ЃКFPGAЦЌФкROM FIFO RAMСЊКЯЪЕР§ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

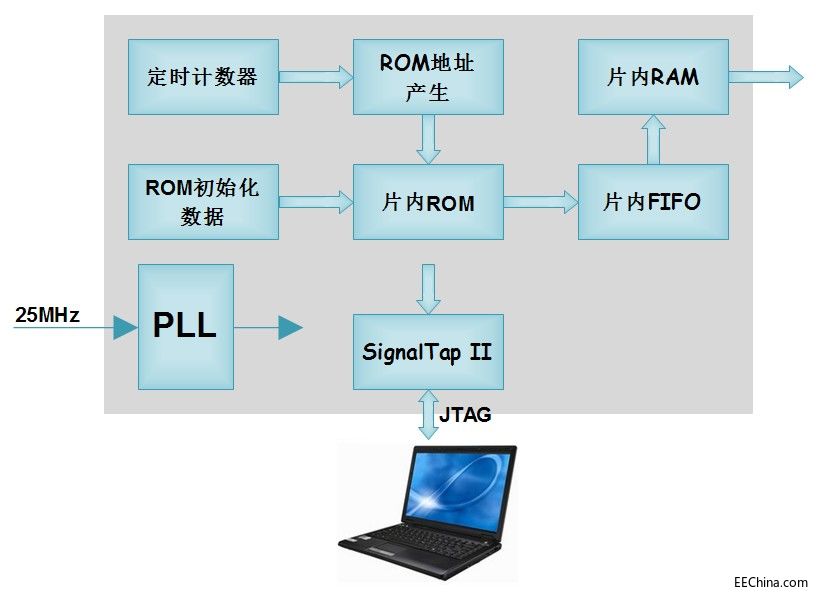

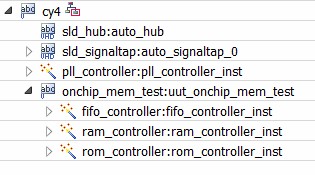

ИУЙЄГЬЪЕР§ФкВПЯЕЭГЙІФмПђЭМШчЭМ9.89ЫљЪОЁЃЮвУЧЭЈЙ§IPКЫЗжБ№Р§ЛЏСЫROMЁЂFIFOКЭRAMЃЌROMгадЄДцДЂЕФЪ§ОнПЩЙЉЖСШЁЃЌНЋЦфЗХШыFIFOжаЃЌЫцКѓдйЖСГіЫЭЕНRAMЙЉЖСШЁЁЃЭЈЙ§Quartus IIМЏГЩЕФдкЯпТпМЗжЮівЧSignalTapIIЃЌЮвУЧПЩвдЙлВьFPGAЦЌФкROMЁЂFIFOКЭRAMЕФЖСаДЪБађЃЌвВПЩвджЛБШНЯROMдЄДцДЂЕФЪ§ОнКЭRAMзюКѓЖСГіЕФЪ§ОнЃЌШЗШЯећИіЖСаДЛКДцЙ§ГЬжаЃЌЪ§ОнЕФвЛжТадЪЧЗёЪЕЯжЁЃ

ЭМ9.89 ДцДЂЦїСЊКЯЪЕР§ЙІФмПђЭМ БОЪЕР§ЙЄГЬФЃПщВуДЮШчЭМ9.90ЫљЪОЁЃ

ЭМ9.90 ДцДЂЦїСЊКЯЪЕР§ФЃПщВуДЮ Quartus IIжаЃЌЕуЛїВЫЕЅЁАTools ЈЄ Run Simulation Tool ЈЄ RTL SimulationЁБНјааЗТецЁЃНгзХЃЌModelsimжаЮвУЧПЩвдВщПДЖСFIFOЕФВЈаЮЁЃ ROMЁЂFIFOКЭRAMЖСаДВЈаЮШчЭМ9.92ЫљЪОЁЃ

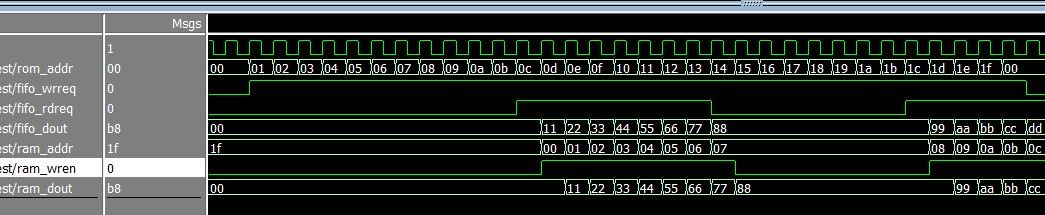

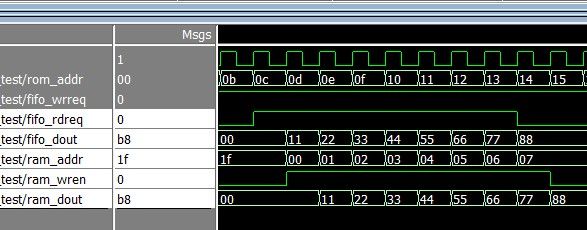

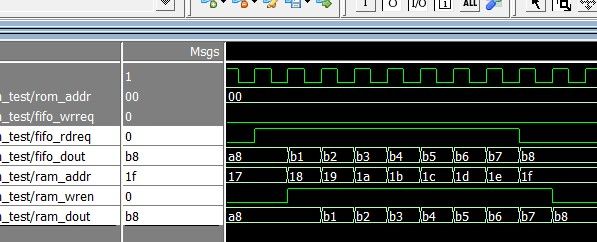

ЭМ9.92 ROMЁЂFIFOКЭRAMЖСаДВЈаЮ ROMЖСЪ§ОнВЈаЮШчЭМ9.93ЫљЪОЁЃ

ЭМ9.93 ROMЖСЪ§ОнВЈаЮ FIFOЕквЛДЮЖСВЈаЮШчЭМ9.94ЫљЪОЁЃ

ЭМ9.94 ЕквЛДЮFIFOЖСЪ§ОнВЈаЮ FIFOЕкЖўДЮЖСВЈаЮШчЭМ9.95ЫљЪОЁЃ

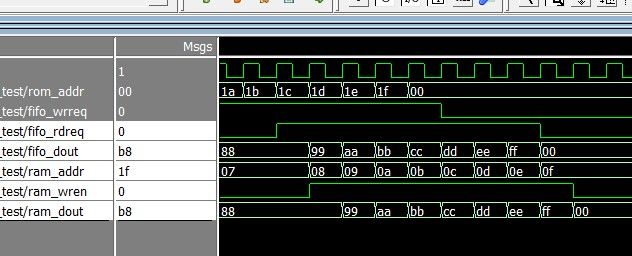

ЭМ9.95 ЕкЖўДЮFIFOЖСЪ§ОнВЈаЮ FIFOЕкШ§ДЮЖСВЈаЮШчЭМ9.96ЫљЪОЁЃ

ЭМ9.96 ЕкШ§ДЮFIFOЖСЪ§ОнВЈаЮ FIFOЕкЫФДЮЖСВЈаЮШчЭМ9.97ЫљЪОЁЃ

ЭМ9.97 ЕкЫФДЮFIFOЖСЪ§ОнВЈаЮ RAMЖСЪ§ОнВЈаЮШчЭМ9.98ЫљЪОЁЃ

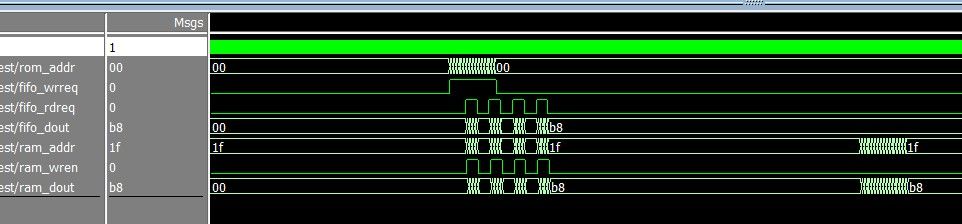

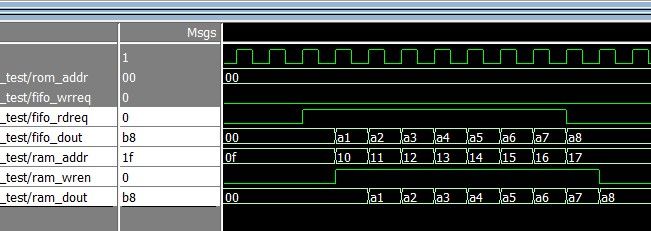

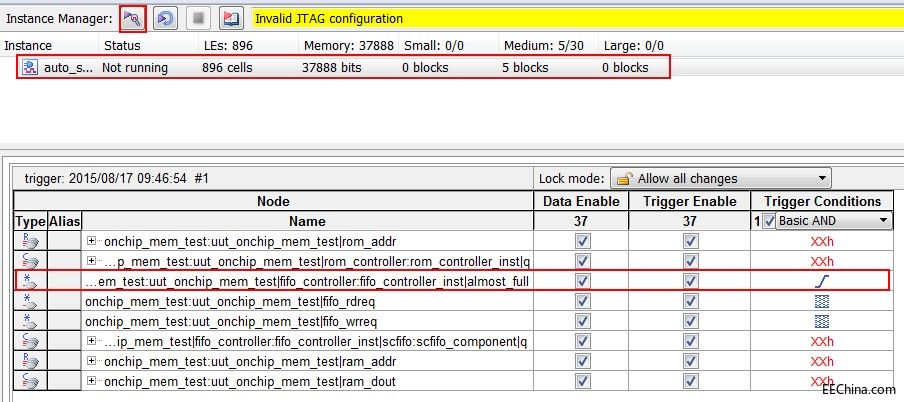

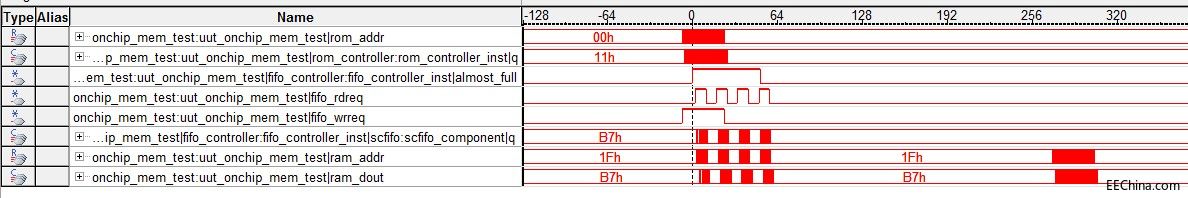

ЭМ9.98 RAMЖСЪ§ОнВЈаЮ СЌНгКУЯТдиЯпЃЌИјCY4ПЊЗЂАхЙЉЕчЁЃ ЕуЛїВЫЕЅЁАTools ЈЄ SignalTap II Logic AnalyzerЁБЃЌНјШыТпМЗжЮівЧжївГУцЁЃ дкгвВрЕФЁАJTAG ChinaConfigurationЁБДАПкжаЃЌНЈСЂКУUSB BlasterЕФСЌНгКѓЃЌЕуЛїЁАSOF ManagerЁБКѓУцЕФProgrammerАДХЅНјааЯТдиЁЃ ШчЭМ9.99ЫљЪОЃЌдкЁАtriggerЁБЯТУцТоСаСЫЮвУЧвбОЬэМгКУЕФашвЊЙлВьЕФаХКХЃЌгШЦфЪЧдкalmost_fullаХКХЕФTriggerConditionsвЛСаЃЌЮвУЧЩшжУСЫжЕЩЯЩ§биЃЌБэЪОalmost_fullЩЯЩ§биЃЈFIFOПьвЊТњСЫЃЉЪБЮвУЧНЋДЅЗЂВЩМЏЁЃСэЭтЃЌЮвУЧгУЪѓБъЕуЛїбЁжаInstanceЯТУцЕФЮЈвЛвЛИібЁЯюЃЌШЛКѓЕЅЛїInstanceManagerКѓУцЕФдЫааАДХЅЃЌжДаавЛДЮДЅЗЂВЩМЏЁЃ

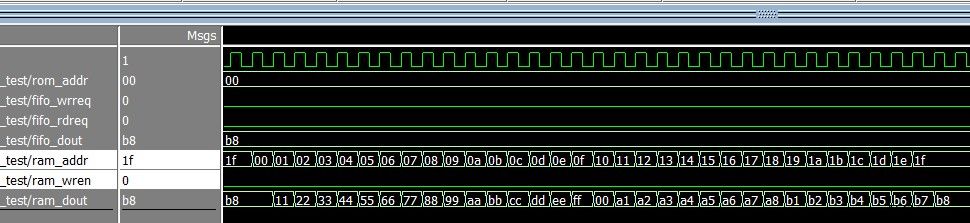

ЭМ9.99 ВЈаЮВЩбљДЅЗЂЩшжУ ВЈаЮШчЭМ9.100ЫљЪОЁЃетРяАќРЈСЫROMЕФЖСШЁВйзїЁЂFIFOЕФаДКЭЖСВйзїЁЂRAMЕФаДКЭЖСВйзїЁЃ

ЭМ9.100 ROMЁЂFIFOКЭRAMЖСаДВЈаЮ |

ЭјгбЦРТл