гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди78ЃКFPGAЦЌФкROMЪЕР§жЎЙІФмИХЪі

ЗЂВМЪБМфЃК2018-6-16 19:41

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди78ЃКFPGAЦЌФкROMЪЕР§жЎЙІФмИХЪі ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

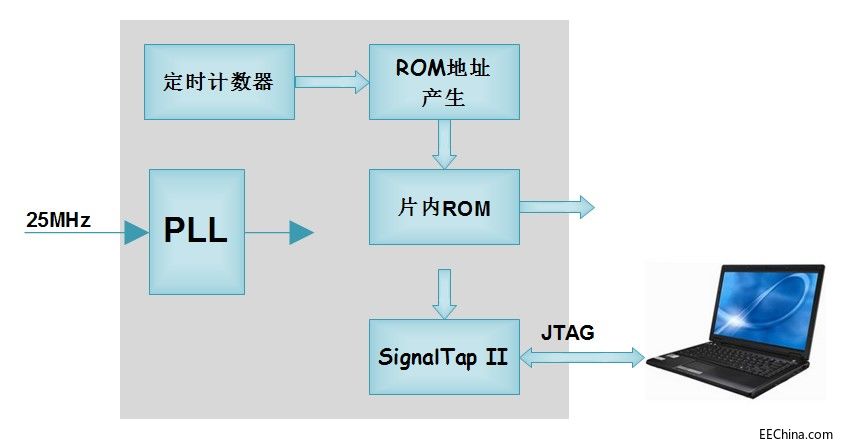

ИУЙЄГЬЪЕР§ФкВПЯЕЭГЙІФмПђЭМШчЭМ9.18ЫљЪОЁЃЮвУЧЭЈЙ§IPКЫР§ЛЏвЛИіROMЃЌЖЈЪББщРњЖСШЁЦфЫљгаЕижЗЕФЪ§ОнЁЃЭЈЙ§QuartusIIМЏГЩЕФдкЯпТпМЗжЮівЧSignalTap IIЃЌЮвУЧПЩвдЙлВьROMЕФЖСЪБађЁЃ

ЭМ9.18 ROMЪЕР§ЙІФмПђЭМ БОЪЕР§ЙЄГЬФЃПщВуДЮШчЭМ9.19ЫљЪОЁЃ

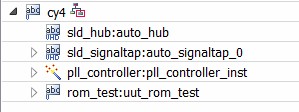

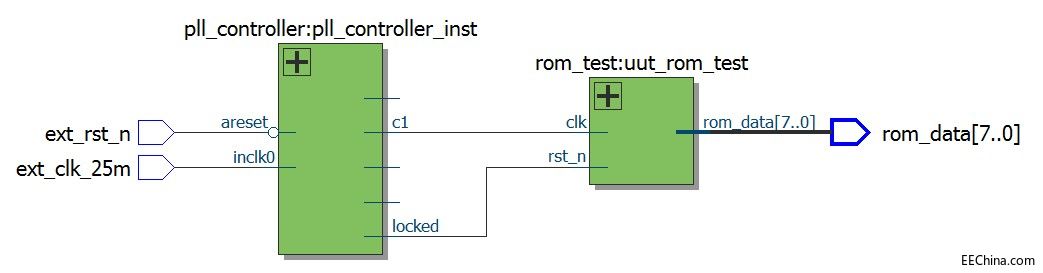

ЭМ9.19 ROMЪЕР§ФЃПщВуДЮ дкЖЅВуФЃПщcy4.vДњТыжаЃЌПЩвдВщПДЦфRTL SchematicШчЭМ9.20ЫљЪОЁЃcy4.vФЃПщжївЊЖЈвхНгПкаХКХвдМАЖдИїИізгФЃПщНјааЛЅСЊЁЃpll_controller.vФЃПщР§ЛЏPLL IPКЫЃЌВњЩњFPGAФкВПЦфЫќТпМЙЄзїЫљашЕФЪБжгаХКХclk_25mКЭИДЮЛаХКХsys_rst_nЃЛrom_test.vФЃПщР§ЛЏFPGAЦЌФкROMЃЌВЂВњЩњFPGAЦЌФкROMЖСЕижЗЃЌЖЈЪББщРњЖСШЁROMжаЕФЪ§ОнЃЛДЫЭтЃЌЭМжаЮДЪОвтЃЌИУЙЄГЬЪЕР§ЛЙАќРЈСЫSignalTapIIЕФIPКЫФЃПщЃЌИУФЃПщв§ГіROMЕФЖСШЁаХКХзмЯпЃЌПЩвддкЯпВщПДROMЖСШЁЪБађЁЃ

ЭМ9.20 ROMЪЕР§ФЃПщЛЅСЊНгПк |

ЭјгбЦРТл