гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди67ЃКUART loopbackВтЪд

ЗЂВМЪБМфЃК2018-5-5 17:44

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди67ЃКUART loopbackВтЪд ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

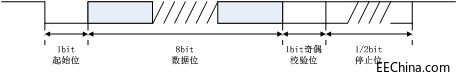

UARTЃЈUniversal Asynchronous Receiver/TransmitterЃЉЃЌМДЭЈгУвьВНЪеЗЂЃЌЫќЕФЪ§ОнДЋЪфВЛашвЊЪБжгЃЌжЛвЊСНЬѕаХКХЯпЗжБ№НјааЪ§ОнЪеЗЂЁЃМШШЛУЛгаЪБжгЃЌФЧУДЫћУЧЪЧШчКЮБЃжЄЪ§ОнЪеЗЂЕФзМШЗадЕФЃПКмМђЕЅЃЌЪеЗЂЫЋЗНЪзЯШашвЊзіЕНжЊМКжЊБЫЃЌдМЖЈКУЪ§ОнДЋЪфЕФЫйТЪЃЈМђЕЅЕФНВОЭЪЧдМЖЈКУвЛИіЪ§ОнЮЛДЋЪфЕФЪБМфЃЉКЭжЁИёЪНЃЈМДвЛжЁЕФГЄЖЬЃЌвЛжЁгЩФФаЉЮЛзщГЩЃЌЫћУЧЕФЙІФмЖМЪЧЪВУДЃЉЁЃ ЮвУЧПДПДUARTЕФвЛИіжЁЖЈвхЁЃМђЕЅЕФДЎПкжЁИёЪНШчЭМ8.49ЫљЪОЃЌЫќгЩ1ИіЦ№ЪМЮЛЃЈБиаыЮЊ0ЃЉЁЂ8ИіЪ§ОнЮЛЃЈгУЛЇЪ§ОнЃЉЁЂ1ИіЦцХМаЃбщЮЛЃЈгУгкМђЕЅЕФОРДэвдБЃжЄДЋЪфПЩППадЃЉКЭ1Лђ2ИіЭЃжЙЮЛЃЈБиаыЮЊ1ЃЉзщГЩЁЃГ§СЫЦцХМаЃбщЮЛЃЌЦфЫћШ§ИіВПЗжЖМЪЧБиаыЕФЁЃЕБаХКХЯпПеЯаЪБЃЌБиаыЮЊИпЕчЦНЁЃвЊЗЂЦ№Ъ§ОнДЋЪфЪБЃЌ1ИіЕЭЕчЦНЕФТіГхБэЪОЦ№ЪМЮЛЃЌШЛКѓСЌајДЋЪф8ИіЪ§ОнЮЛКЭШєИЩИіИпЕчЦНЕФЭЃжЙЮЛЃЌетбљБуЭъГЩвЛДЮДЋЪфЁЃ

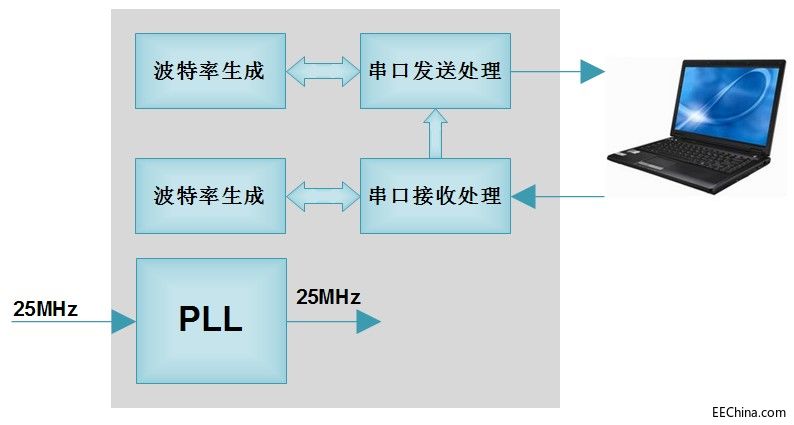

ЭМ8.49ДЎПкжЁИёЪН ИУЪЕбщвЊЪЕЯжЕФЙІФмЪЧFPGAЪЕЪБМрВтuart_rxаХКХЪЧЗёгаЪ§ОнЃЌШєНгЪеЕНЪ§ОнЃЌдђАбНгЪеЕНЕФЪ§ОнЭЈЙ§uart_txЗЂЛиИјЖдЗНЁЃPCЛњЪЙгУвЛИіДЎПкЕїЪджњЪжНјааЭЈаХЁЃ дкДњТыЩшМЦжаЃЌspeed_setting.vФЃПщРяПЩвдаоИФЪеЗЂЪ§ОнЕФВЈЬиТЪЃЌШч9600bpsЃЌ19200bpsЃЌ38400bpsЃЌ57600bpsЛђ115200bpsЕШЁЃЗЂЫЭЕФЪ§ОнжЁИёЪНЮЊЃК1bitЦ№ЪМЮЛЃЌ8bitЪ§ОнЃЌЮоаЃбщЮЛЃЌ1bitЭЃжЙЮЛЁЃ ИУЪЕР§ЕФФкВПЙІФмШчЭМ8.50ЫљЪОЁЃ

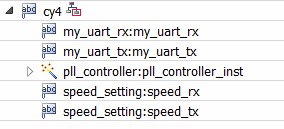

ЭМ8.50 ДЎПкЪЕР§ЙІФмПђЭМ ИУЙЄГЬЪЕР§ЕФЩшМЦФЃПщВуДЮШчЭМ8.51ЫљЪОЁЃ

ЭМ8.51 ДЎПкЪЕР§ФЃПщВуДЮ |

ЭјгбЦРТл