勇敢的芯伴你玩转Altera FPGA连载61:PLL概述

发布时间:2018-4-10 22:08

发布者:rousong1989

|

勇敢的芯伴你玩转Altera FPGA连载61:PLL概述 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1i5LMUUD

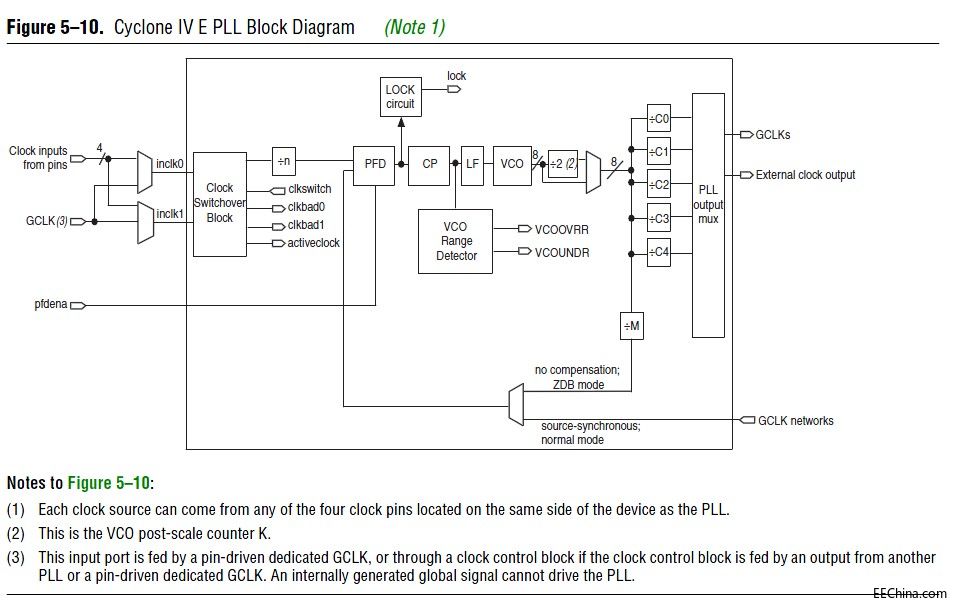

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 时钟就是FPGA运行的心脏,它的每次跳动必须精准而毫无偏差(当然现实世界中不存在所谓的毫无偏差,但是我们希望它的偏差越小越好)。一个FPGA工程中,不同的外设通常工作在不同的时钟频率下,所以一个时钟肯定满足不了需求;此外,有时候可能两个不同的模块共用一个时钟频率,但是由于他们运行在不同的工作环境和时序下,所以他们常常是同频不同相(相位),怎么办?用PLL呗。当然了,我们的FPGA里面定义的PLL,可不是仅仅只有一个反馈调整功能,它还有倍频和分频等功能集成其中。严格一点讲,我觉得这个PLL实际上应该算是一个FPGA内部的时钟管理模块了。不多说,如图8.16所示,大家看看PLL内部的功能框图自己体味体味。

图8.16Cyclone IV PLL内部结构 大家记住PLL一个最主要的功能,即能够对输入的基准时钟信号进行一定范围内的分频或者倍频,从而产生多个输出时钟信号供芯片内部的各个功能模块使用。 |

网友评论