米尔 MYD-Y7Z010/007S开发板核心板电路及底板设计说明

发布时间:2018-3-16 11:02

发布者:myir

|

型号: 米尔 MYD-Y7Z010/007S开发板 核心板电路及底板设计说明 1 核心板电源

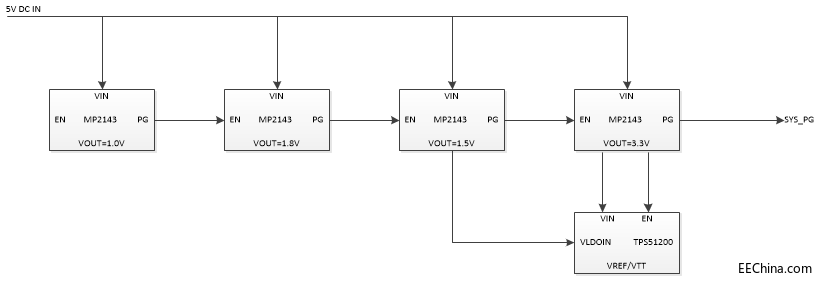

上图为开发板电源框图,通过Power good信号,按顺序级联,以1.0V->1.8V->1.5V->3.3V的顺序完成上电过程。3.3V最后上电,同时提供复位信号对系统进行复位动作,随后系统开始启动。 2引导模式选择 核心板默认QSPI启动模式,用户可通过跳线(BOOT_JP1/BOOT_JP2)选择SD卡启动或JTAG启动模式。

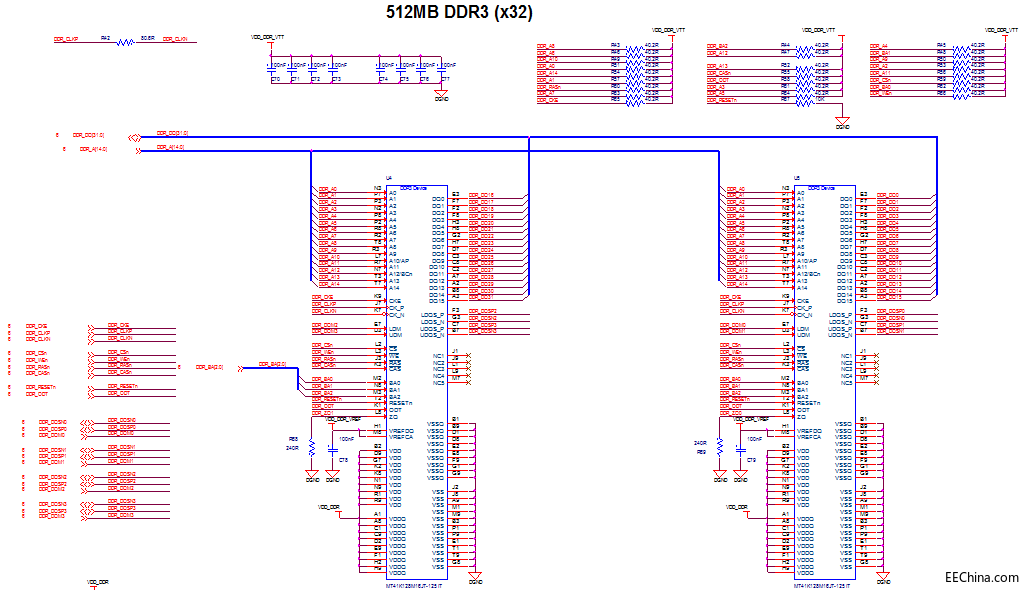

3 DDR

核心板采用两片128Mx16的DDR3内存芯片,共512MB,最高可升级到1GB。DDR控制器接口PS BANK 502,为32bit数据总线。 4 存储 4.1 SPI Flash

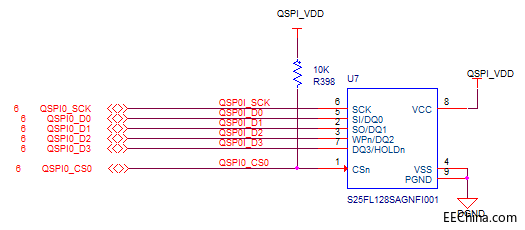

核心板板载一片16MB QSPI Flash W25Q128FVEIG,可以用于引导SoC,初始化PS并配置PL部分。接口PS BANK500 MIO[1-6]。 4.2 eMMC

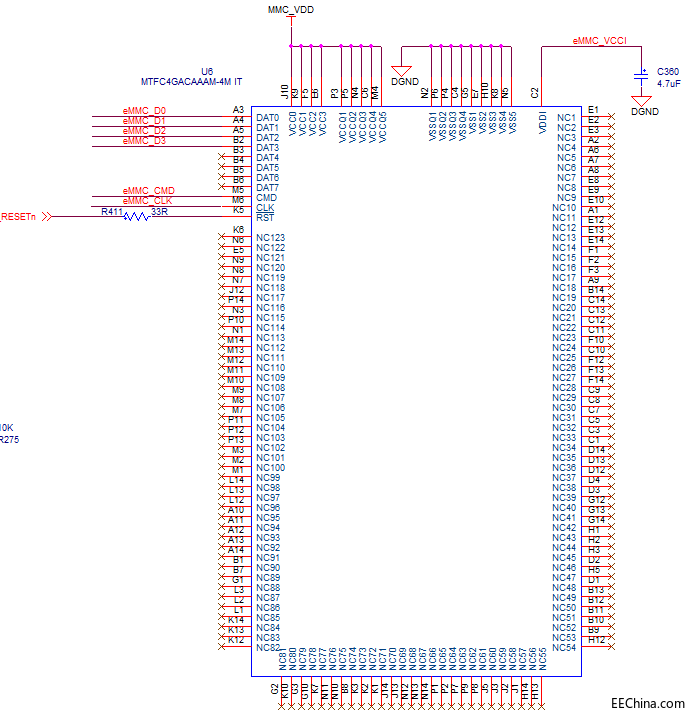

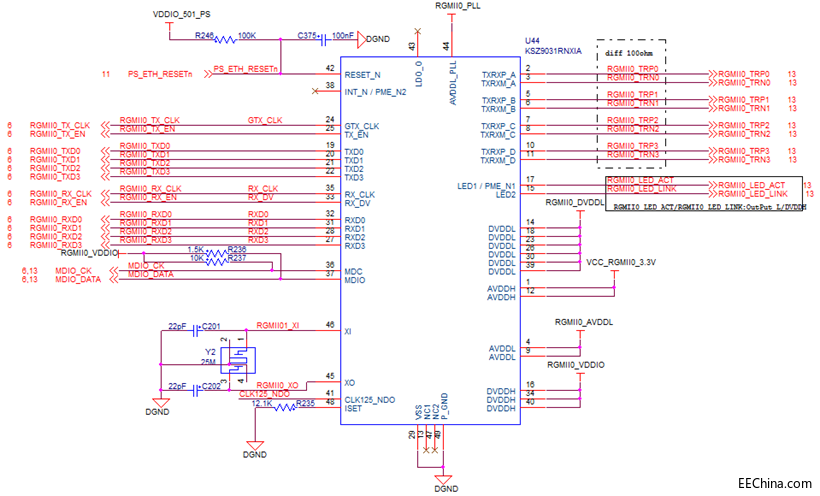

开发板板载4GB MICRON EMMC,接口PS_SDIO1,可用于系统文件或其他数据文件存储。可用作次级启动设备,与QSPI FLASH一起用于系统启动。接口PS BANK500 MIO[10-15]。 5 以太网

PS MAC0接口Ethernet PHY KSZ9031RN实现千兆网口。接口PS BANK501 MIO[16-27]。 6 USB PS USB1控制器外接PHY USB3320可实现USB OTG。接口PS BANK MIO[28-39]。 7看门狗及复位相关配置

使用外部看门狗芯片CAT823TTDI-GT3,该芯片的喂狗引脚连接到了CPU的PS_MIO0引脚,WDI未短接时看门狗不工作,调试阶段可以通过跳线禁止看门狗工作。 |

网友评论