гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди51ЃКAltera FPGAХфжУЗНЪНИХЪі

ЗЂВМЪБМфЃК2018-3-4 22:16

ЗЂВМепЃКrousong1989

|

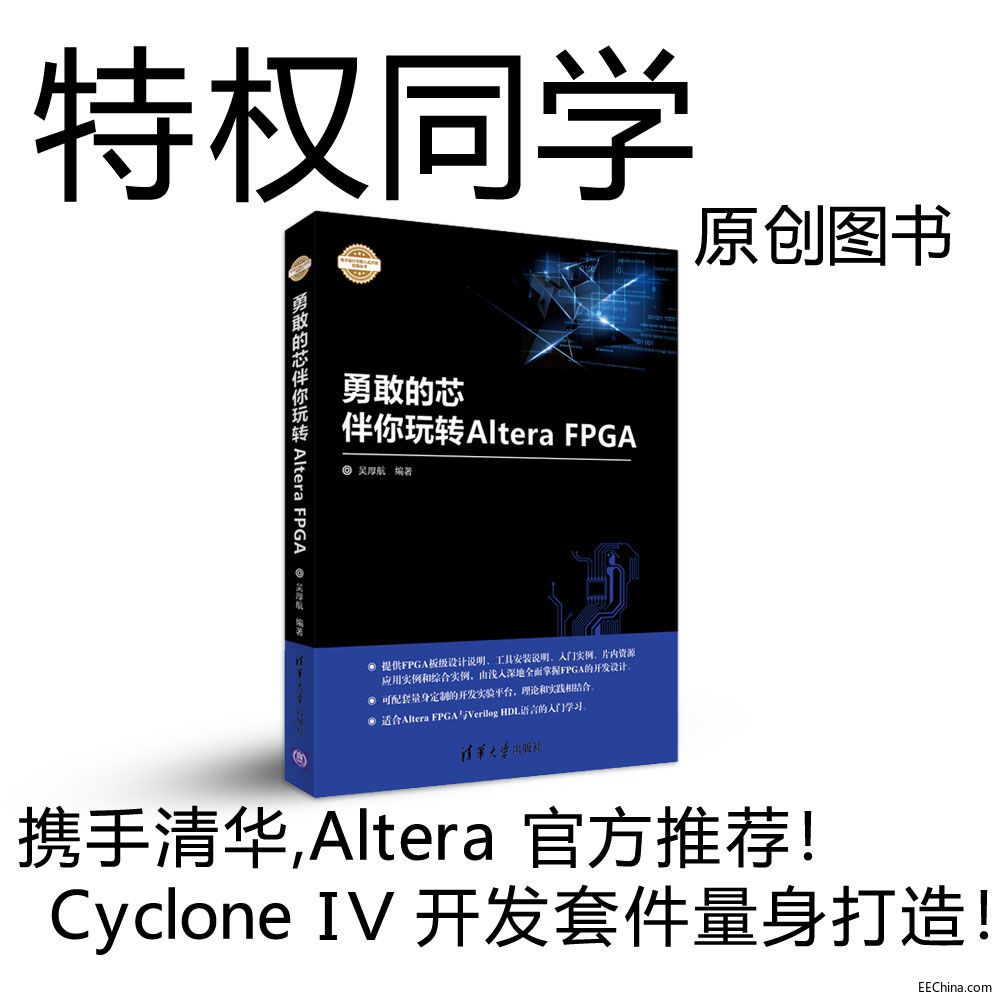

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди51ЃКAltera FPGAХфжУЗНЪНИХЪі ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

FPGAЪЧЛљгкRAMНсЙЙЕФЃЌЕБШЛСЫЃЌвВгаЛљгкFLASHНсЙЙЕФЃЌЕЋRAMНсЙЙЕФЪЧжїСїЃЌвВЪЧЮвУЧЬжТлЕФжиЕуЁЃЖјRAMЪЧвзЪЇДцДЂЦїЃЌдкЕєЕчКѓБЃДцдкЩЯУцЕФЪ§ОнОЭЖЊЪЇСЫЃЌжиаТЩЯЕчКѓашвЊдйЯТдивЛДЮВХПЩвдЁЃвђДЫЃЌЮвУЧПЯЖЈВЛЯЃЭћУПДЮжиаТЩЯЕчКѓЖМгУPCШЅЯТдивЛДЮЃЌЙЄГЬЪЕЯжвВВЛдЪаэЮвУЧетУДзіЁЃЫљвдЃЌЭЈГЃFPGAХдБпЖМгавЛПХХфжУаОЦЌЃЌЫќЭЈГЃЪЧвЛЦЌFLASHЃЌЛђепЪЧВЂааЛђепЪЧДЎааНгПкЕФЁЃВЛЙмЪЧДЎааЛЙЪЧВЂааЕФFLASHЃЌЫќУЧЕФЦєЖЏМгдидРэЛљБОЯрЭЌЃЌКѓУцЮвУЧЛсзЈУХЬжТлЁЃ FPGAЦїМўгаШ§РрХфжУЯТдиЗНЪНЃКжїЖЏХфжУЗНЪНЃЈASЃЉЁЂБЛЖЏХфжУЗНЪНЃЈPSЃЉКЭзюГЃгУЕФЛљгкJTAGЕФХфжУЗНЪНЁЃASКЭPSФЃЪНжївЊЪЧНЋbitСїЯТдиЕНХфжУаОЦЌжаЃЛЖјJTAGФЃЪНдђМШФмНЋДњТыЯТдиЕНFPGAжажБНгдкЯпдЫааЃЈЫйЖШПьЃЌЕїЪдЪБгХбЁЃЉЃЌвВФмЙЛЭЈЙ§FPGAНЋbitСїЯТдиЕНХфжУаОЦЌжаЁЃгЩгкJTAGЗНЪНСщЛюЖргУЃЌЫљвдЮвУЧЕФSF-CY4ПЊЗЂАхОЭжЛдЄСєСЫJTAGНгПкЁЃ |

ЭјгбЦРТл