гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди45ЃКЛљгкЗТецЕФЕквЛИіЙЄГЬЪЕР§жЎВтЪдНХБОДДНЈгыБрМ

ЗЂВМЪБМфЃК2018-1-26 22:55

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди45ЃКЛљгкЗТецЕФЕквЛИіЙЄГЬЪЕР§жЎВтЪдНХБОДДНЈгыБрМ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

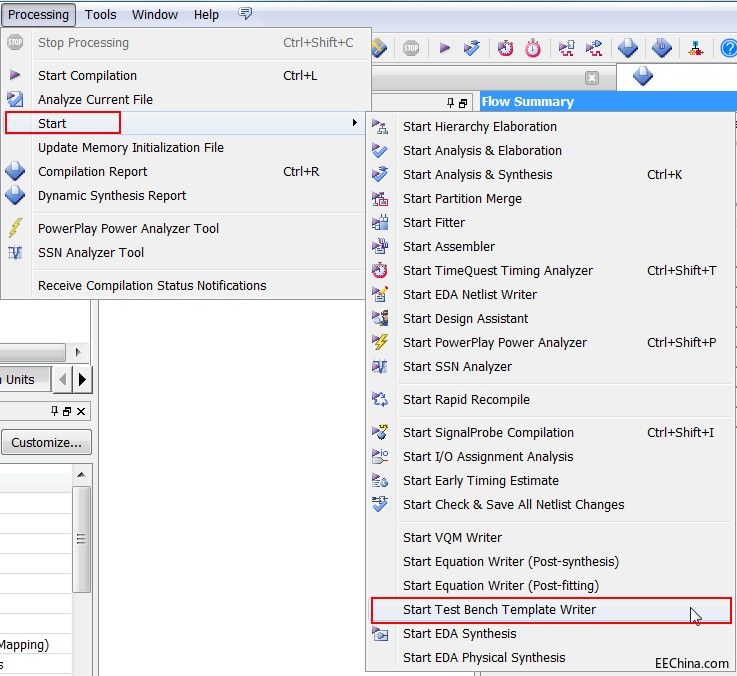

ЛиЕНQuartus IIЙЄОпжаЃЌШчЭМ6.13ЫљЪОЃЌЕуЛїВЫЕЅРИЕФЁАProcessingЈЄStartЈЄStart Test Bench Template WriterЁБЃЌЫцКѓЕЏГіЬсЪОЁАTest Bench Template Writer was successfulЁБЃЈдкДЫжЎЧАЃЌзюКУЖдећИіЙЄГЬзівЛДЮШЋБрвыЃЌЗёдђПЩФмБЈДэЃЉЃЌФЧУДЮвУЧОЭвбОДДНЈСЫвЛИіVerilogВтЪдНХБОЃЌдкДЫНХБОжаЃЌЮвУЧПЩвдЩшМЦвЛаЉВтЪдМЄРјЪфШыВЂЧвЙлВьЯргІЪфГіЃЌНшДЫЮвУЧОЭФмЙЛбщжЄдЙЄГЬЕФЩшМЦДњТыЪЧЗёЗћКЯвЊЧѓЁЃ

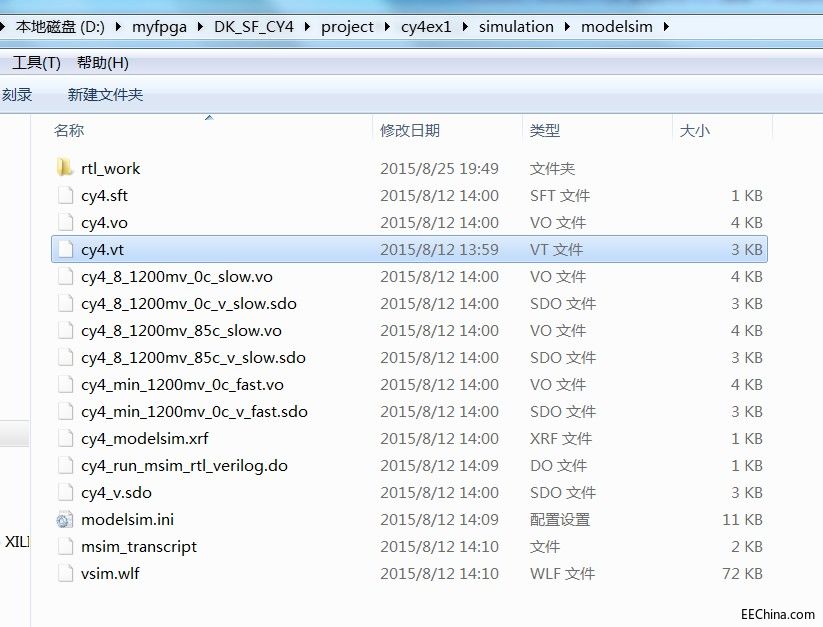

ЭМ6.13 ЩњГЩВтЪдНХБО ЮвУЧДђПЊЙЄГЬЫљдкЮФМўМаЯТЕФЁАЁ/simulation/modelsimЁБЮФМўМаЃЌШчЭМ6.14ЫљЪОЃЌПЩвдПДЕНвЛИіУћЮЊcy4.vtЕФВтЪдНХБОЮФМўДДНЈКУСЫЁЃ

ЭМ6.14 ВтЪдНХБОЮФМў ВтЪдНХБОЮФМўдкNotepad++жаДђПЊСЫЁЃетРяЕФВтЪдНХБОжЛЪЧвЛИіЛљБОЕФФЃАхЃЌЫќАбЩшМЦЮФМўcy4.vЕФНгПкдкетИіФЃПщРяУцР§ЛЏЩъУїСЫЃЌЮвУЧЛЙашвЊздЖЏЖЏЪжЬэМгИДЮЛКЭЪБжгЕФМЄРјЃЌБрМКУЕФВтЪдНХБОШчЯТЫљЪОЁЃ `timescale 1 ns/ 1 ps module cy4_vlg_tst(); // test vector input registers reg ext_clk_25m; reg ext_rst_n; // wires wire clk_12m5; // assign statements (if any) cy4 i1 ( // port map - connection between master ports and signals/registers .clk_12m5(clk_12m5), .ext_clk_25m(ext_clk_25m), .ext_rst_n(ext_rst_n) ); initial begin // Initialize Inputs ext_clk_25m = 0; ext_rst_n = 0; // Wait 100 ns for globalreset to finish #100; ext_rst_n = 1; // Add stimulus here #2000; $stop; end always #20 ext_clk_25m =~ext_clk_25m; //ВњЩњ25MHzЪБжгдД endmodule гаХѓгбПЩФмЪЧЕквЛДЮНгДЅВтЪдЗТецЃЌЙигкЗТецЕФЛљБОИХФюЧыВщПДЁЖFPGAЩшМЦЪЕеНбнСЗЃЈТпМЦЊЃЉЁЗЕкОХеТЕФЩшМЦЗТецВПЗжФкШнЁЃ |

ЭјгбЦРТл