广州创龙TL665x-EasyEVM DSP TMS320C665x + Xilinx Artix-7 FPGA处理器

发布时间:2018-1-19 14:12

发布者:zhiwing

|

1 开发板简介 TMS320C665x主频为1.0/1.25GHz,单核运算能力高达40GMACS和20GFLOPS,FPGA XC7A100T逻辑单元101K个,DSP Slice 240个; TMS320C665x与FPGA内部通过uPP、EMIF16、SRIO连接; 双SFP接口,传输速率可高达5Gbit/s,可接SFP光口模块或SFP电口模块; 支持千兆网口等高速接口,可接工业网络摄像机; PCI Express 2.0高速数据传输接口,双通道,每通道通信速率可高达5GBaud; Serial Rapid I/O高速数据传输接口,双通道,每通道通信速率可高达5GBaud; 可通过DSP配置及烧写FPGA程序,DSP和FPGA可以独立开发且互不干扰; 支持uPP、EMIF16,同时支持I2C、SPI、UART、McBSP等常见接口; 连接稳定可靠,开发板采用工业级精密B2B高速连接器,关键大数据接口使用高速连接器,保证信号完整性; 提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

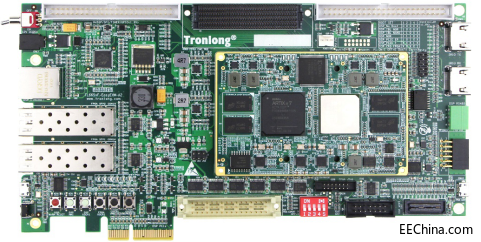

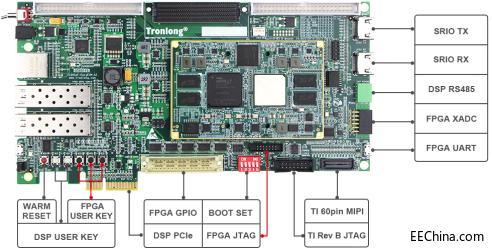

图 1 开发板正面图

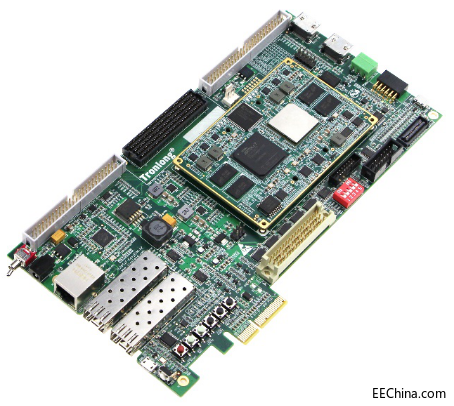

图 2 开发板斜视图

图 3 开发板侧视图1

图 4 开发板侧视图2

图 5 开发板侧视图3

图 6 开发板侧视图4 广州创龙结合TI KeyStone系列多核架构TMS320C665x及Xilinx Artix-7系列FPGA设计的TL665xF-EasyEVM开发板是一款DSP+FPGA高速大数据采集处理平台,其底板采用沉金无铅工艺的6层板设计,适用于高端图像处理、软件无线电、雷达声纳、高端数控系统、机器视觉等高速数据处理领域。核心板在内部通过uPP、EMIF16、SRIO通信接口将DSP与FPGA结合在一起,组成DSP+FPGA架构,实现了需求独特、灵活、功能强大的DSP+FPGA高速数据采集处理系统。 TL665xF-EasyEVM开发板引出DSP及FPGA全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。创龙不仅提供丰富的Demo程序,还提供DSP核间通信、DSP与FPGA间通讯开发教程以及全面的技术支持,协助客户进行底板设计和调试以及多核软件开发。 2 典型运用领域高端图像处理 软件无线电 雷达声纳 高端数控系统 机器视觉 3 软硬件参数硬件框图

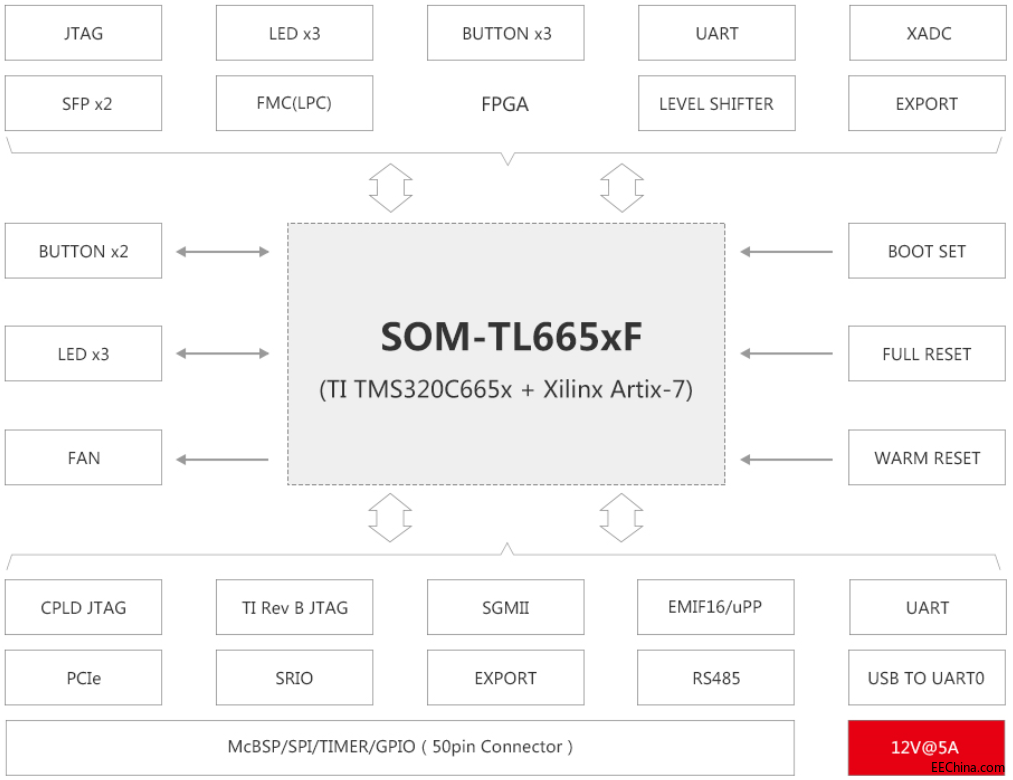

图 7 开发板硬件框图

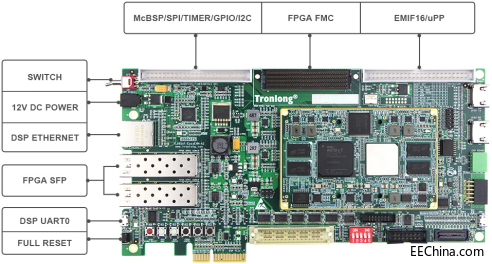

图 8 开发板硬件资源图解1

图 9 开发板硬件资源图解2 硬件参数 表 1 DSP端硬件参数

表 2 FPGA端硬件参数

软件参数 表 3 软件参数

(1) 提供核心板引脚定义、可编辑底板原理图、可编辑底板PCB、芯片Datasheet,缩短硬件设计周期; (2) 提供丰富的Demo程序,包含DSP多核通信教程,完美解决多核开发瓶颈; (3) 提供DSP与FPGA通过SRIO、EMIF16、I2C、uPP等相关通讯例程; (4) 提供完整的平台开发包、入门教程,节省软件整理时间,上手容易。 部分开发例程详见附录A,开发例程主要包括: Ø 裸机开发例程 Ø SYS/BIOS开发例程 Ø 多核开发例程 Ø FPGA开发例程 5 电气特性核心板工作环境 表 4

功耗测试 表 5

备注:功耗测试基于广州创龙TL6657F-EasyEVM开发板进行。 表 6

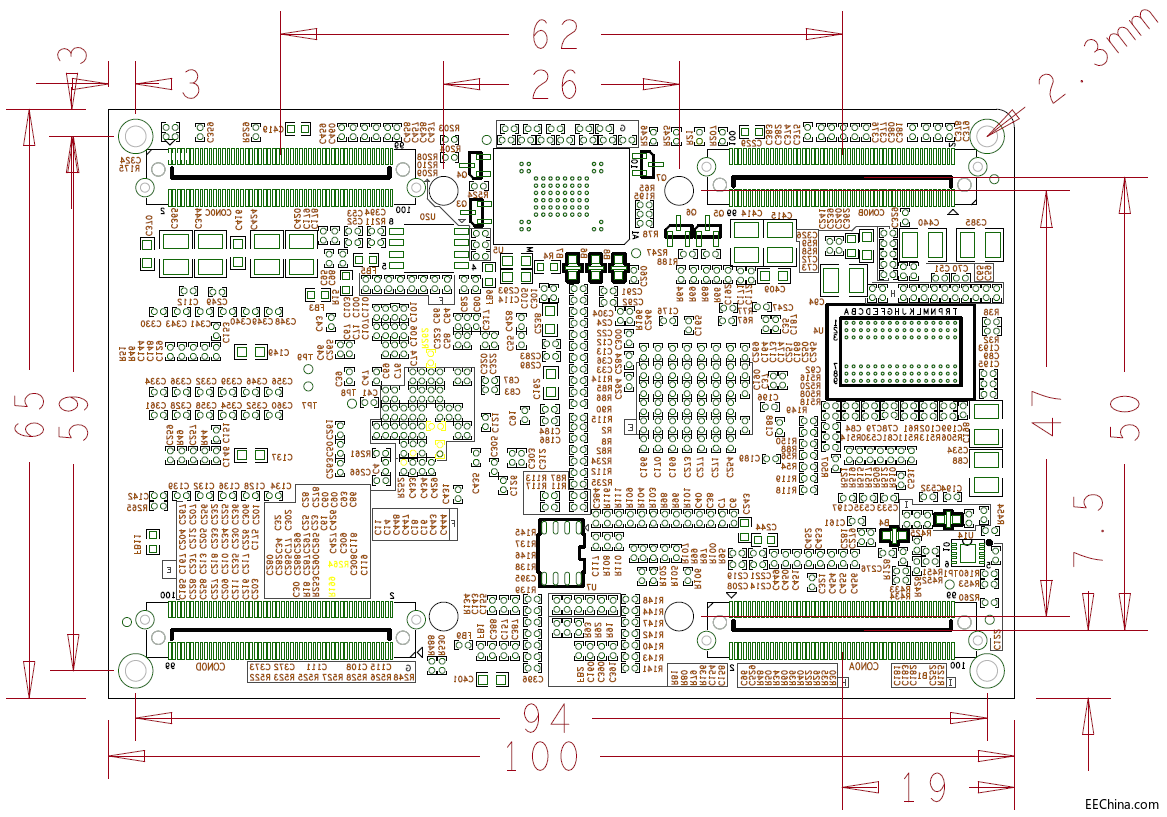

图 10 核心板机械尺寸图

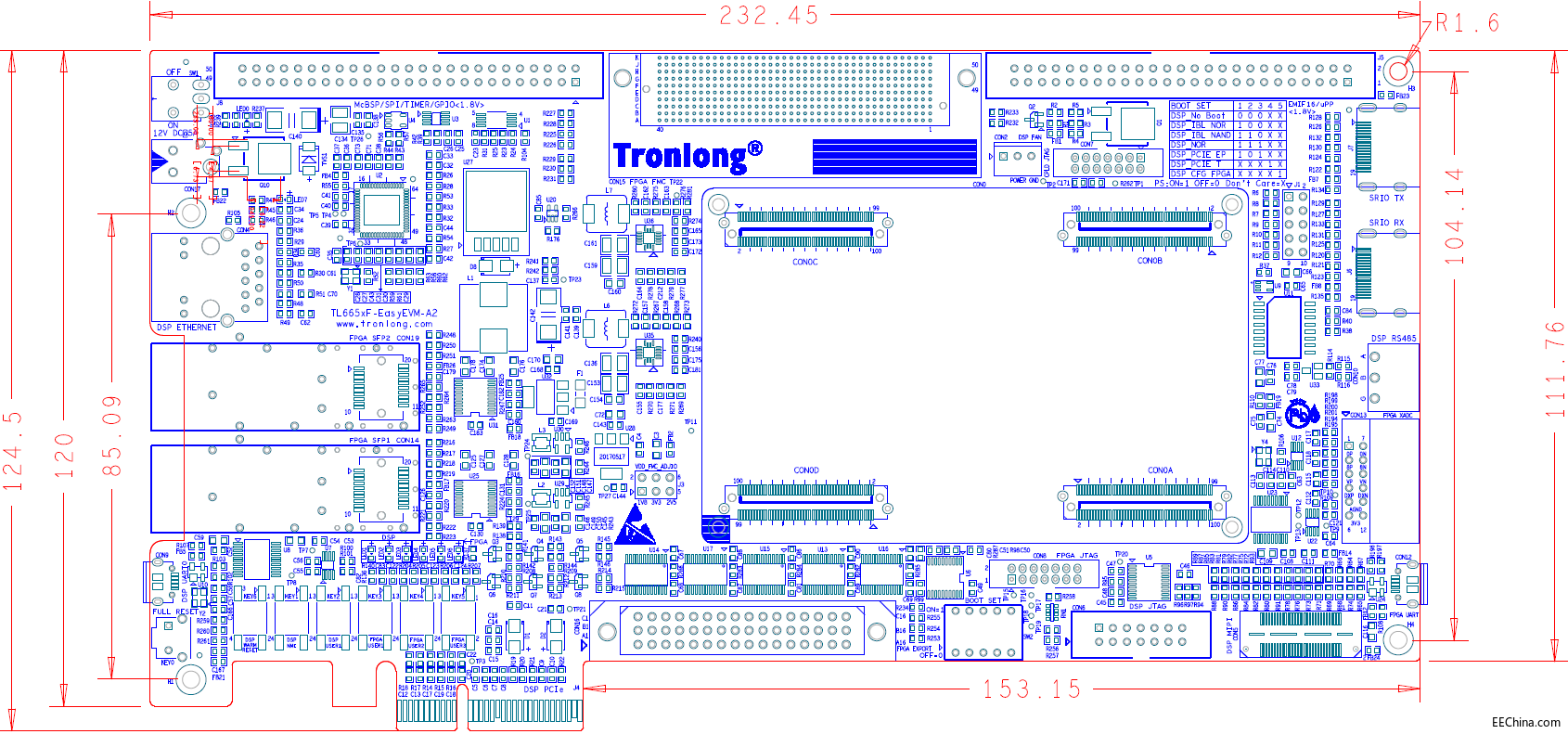

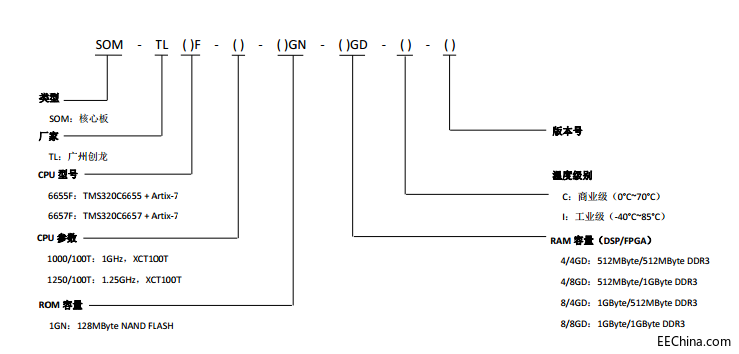

图 11 开发板机械尺寸图 表 7 核心板型号

备注:标配为SOM-TL6655F-1000/100T-1GN-4/4GD-I,其他型号请与相关销售人员联系。 |

网友评论