гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди15ЃКSRAMНгПкЕчТЗ

ЗЂВМЪБМфЃК2017-10-25 21:35

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди15ЃКSRAMНгПкЕчТЗ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

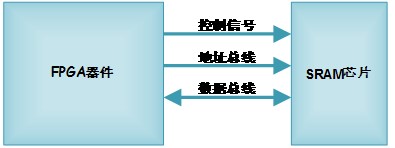

ШчЭМ2.14ЫљЪОЃЌFPGAгыSRAMаОЦЌЕФСЌНгжївЊЪЧПижЦаХКХЁЂЕижЗзмЯпКЭЪ§ОнзмЯпЁЃ

ЭМ2.14 FPGAгыSRAMаОЦЌСЌНгЪОвтЭМ ШчБэ2.1ЫљЪОЃЌетЪЧFPGAгыSRAMаОЦЌЕФв§НХаХКХЖЈвхЁЃ Бэ2.1 FPGAгыSRAMаОЦЌв§НХаХКХЖЈвх

зЂЃКЗНЯђЪЧеыЖдFPGAЦїМўЖјбдЕФЁЃ |

ЭјгбЦРТл