勇敢的芯伴你玩转Altera FPGA连载13:实验平台复位电路解析

发布时间:2017-10-23 20:47

发布者:rousong1989

|

勇敢的芯伴你玩转Altera FPGA连载13:实验平台复位电路解析 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1i5LMUUD

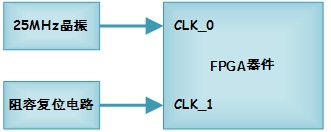

FPGA的时钟输入都有专用引脚,通过这些专用引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA的时钟和复位通常是需要走全局时钟网络的。 如图2.9所示,25MHz的有源晶振和阻容复位电路产生的时钟信号和复位信号分别连接到FPGA的专用时钟输入引脚CLK_0和CLK_1上。

图2.9 复位与时钟电路示意图 如图2.10所示,原理图上示意,我们所使用的FPGA器件共有8个专用时钟输入引脚,在不做时钟输入引脚功能使用时,这些引脚也可以作为普通I/O引脚。如我们的电路中,只使用了CLK_0和CLK_1作为专用时钟引脚功能,其他6个引脚则作为普通的I/O引脚功能。

图2.10 时钟专用输入引脚 FPGA上电复位时间需要大于FPGA器件启动后的配置加载时间,这样才能够确保FPGA运行后的复位初始化过程有效。因此,我们也可以来看看这个电路的设计是否满足实际要求。 查询器件手册中关于上电配置时间的计算,有如下的公式。 配置数据量 * (最低的DCLK时钟周期/1bit) = 最大的配置时间 其中,我们的所使用FPGA器件EP4CE6的配置数据量为2,944,088bits。最低的SPI FLASH传输时钟DCLK通常为20MHz(经实测,一般情况下,DCLK时钟频率为32MHz),那么由此便可计算出最大的配置时间为:2944088bits*(50ns/1bit) = 148ms。 另外,从器件手册上,可以查询到复位输入引脚作为3.3-V LVTTL标准电平的最低VIH电压值是1.7V,那么由此便可计算阻容复位电路从0V上升到1.7V所需的时间。 设V0为电容上的初始电压值;V1为电容最终可充到或放到的电压值;Vt 为t时刻电容上的电压值。则有公式t = RC*Ln[(V1-V0)/(V1-Vt)]。 求充电到1.7V的时间。将已知条件V0=0,V1=3.3V,Vt=1.7V代入上式得:1.7=0+3.3*[[1-exp(-t/RC)],算得t = 0.7239RC。 代入R=47k ,C=10uf得t = 0.34s,即340ms。 由此我们验证了阻容复位的时间远大于FPGA器件的上电复位时间。当然了,这里没有考虑FPGA器件从上电到开始配置运行所需的电压上升时间,一般这个时间不会太长。所以我们的阻容复位肯定是有效的。如果需要实际的确认,还是要通过示波器设备来辅助观察实际信号的延时情况。 |

网友评论