гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди10ЃКЕчдДЕчТЗ

ЗЂВМЪБМфЃК2017-10-17 22:08

ЗЂВМепЃКrousong1989

|

гТИвЕФаОАщФуЭцзЊAltera FPGAСЌди10ЃКЕчдДЕчТЗ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1i5LMUUD

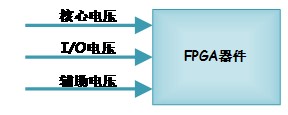

гыШЮКЮЕчзгдЊЦїМўвЛбљЃЌFPGAЦїМўашвЊгаЕчдДЕчбЙЕФЙЉгІВХФмЙЄзїЁЃгШЦфЖдгкЙцФЃНЯДѓЕФЦїМўЃЌЦфЙІКФвВЯрЖдНЯИпЃЌЦфЙЉЕчЯЕЭГЕФКУЛЕНЋжБНггАЯьЕНећИіПЊЗЂЯЕЭГЕФЮШЖЈадЁЃЫљвдЃЌЩшМЦГіИпаЇТЪЁЂИпадФмЕФFPGAЙЉЕчЯЕЭГОпгаМЋЦфживЊЕФвтвхЁЃ ВЛЭЌЕФFPGAЦїМўЁЂВЛЭЌЕФгІгУЗНЪНЛсгаВЛЭЌЕФЕчбЙЕчСїЕФашЧѓЁЃШчЭМ2.4ЫљЪОЃЌМђЕЅЕФЙщФЩЃЌПЩвдНЋFPGAЦїМўЕФЕчбЙашЧѓЗжЮЊШ§РрЃККЫаФЕчбЙЁЂI/OЕчбЙКЭИЈжњЕчбЙЁЃ

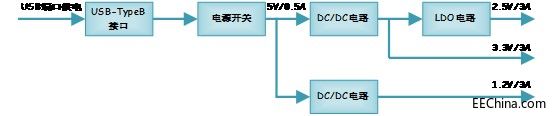

ЭМ2.4 FPGAЦїМўЕФЙЉЕчЕчбЙ КЫаФЕчбЙЪЧFPGAФкВПИїжжТпМЕчТЗе§ГЃЙЄзїдЫааЫљашвЊЕФЛљБОЕчбЙЃЌИУЕчбЙгУгкБЃжЄFPGAЦїМўБОЩэЕФЙЄзїЁЃЭЈГЃбЁЖЈФГвЛПюFPGAЦїМўЃЌЦфКЫаФЕчбЙвЛАувВЖМЪЧвЛИіЙЬЖЈжЕЃЌВЛЛсвђЮЊЕчТЗЕФВЛЭЌгІгУЖјИФБфЁЃКЫаФЕчбЙжЕПЩвдДгЙйЗНЬсЙЉЕФЦїМўЪжВсжаевЕНЁЃ I/OЕчбЙЙЫУћЫМвхБуЪЧFPGAЕФI/Oв§НХЙЄзїЫљашЕФВЮПМЕчбЙЁЃдкв§НХХХВМЩЯЃЌFPGAгыASICзюДѓЕФВЛЭЌЃЌБуЪЧFPGAЫљгаЕФПЩгУаХКХв§НХЛљБОЖМПЩвдзїЮЊЦеЭЈI/OЪЙгУЃЌЦфЕчЦНжЕЕФИпЕЭЭъШЋгЩЦїМўФкВПЕФТпМОіЖЈЁЃЕБШЛСЫЃЌЫќЕФИпЕЭЕчЦНБъзМвВЪмЯогкЫљЙЉИјЕФI/OЕчбЙЁЃШЮКЮвЛЦЌFPGAЦїМўЃЌЫќЕФI/Oв§НХЭЈГЃЛсИљОнХХВМЮЛжУЗжЮЊЖрИіbankЁЃЭЌвЛИіbankФкЕФЫљгаI/Oв§НХЫљЙЉИјЕФI/OЕчбЙЪЧЙВгУЕФЃЌПЩвдИјВЛЭЌЕФbankЬсЙЉВЛЭЌЕФI/OЕчбЙЃЌЫќУЧБЫДЫЪЧВЛСЌЭЈЕФЁЃвђДЫЃЌВЛЭЌbankЕФВЛЭЌI/OЕчбЙЮЊFPGAЦїМўЕФВЛЭЌНгПкгІгУЬсЙЉСЫСщЛюадЁЃетРяОйвЛИіР§згЃЌCyclone IVЯЕСаЦїМўЕФФГаЉbankжЇГжLVDSВюЗжЕчЦНБъзМЃЌДЫЪБЦїМўЪжВсЛсвЊЧѓЩшМЦепИјгУгкLVDSВюЗжгІгУЕФbankЕФI/OЕчбЙЙЉ2.5VЕчбЙЃЌетОЭВЛЭЌгквЛАуЕФLVTTLЛђLVCOMSЕФ3.3VЙЉЕчашЧѓЁЃЖјвЛЕЉетаЉгУгкLVDSДЋЪфЕФI/O bankЕчбЙЙЉИјЮЊ2.5VЃЌФЧУДЫќОЭВЛФмзїЮЊ3.3VЛђЦфЫћЕчЦНжЕБъзМДЋЪфЪЙгУСЫЁЃ Г§СЫЧАУцЬсЕНЕФКЫаФЕчбЙКЭI/OЕчбЙЃЌFPGAЦїМўЙЄзїЫљашЕФЦфЫќЕчбЙЮвУЧЭЈГЃЖМГЦЮЊИЈжњЕчбЙЁЃР§ШчFPGAЦїМўЯТдиХфжУЫљашЕФЕчбЙЃЌЕБШЛСЫЃЌетРяЕФИЈжњЕчбЙжЕПЩФмгыКЫаФЕчбЙжЕЛђI/OЕчбЙжЕЪЧвЛжТЕФЁЃКмЖрFPGAЕФPLLЙІФмПщЕФЙЉЕчЛсгаЬиЪтвЊЧѓЃЌвВПЩвдШЯЮЊЪЧИЈжњЕчбЙЁЃгЩгкPLLБОЩэЪЧФЃФтЕчТЗЃЌЖјFPGAЦфЫћВПЗжЕФЕчТЗЛљБОЪЧЪ§зжЕчТЗЃЌвђДЫPLLЕФЪфШыЕчдДЕчбЙвВКмгаНВОПЃЌашвЊзЈУХЕФЕчШнЕчТЗзіТЫВЈДІРэЃЌЖјЫќЕФЕчбЙжЕвЛАуКЭI/OЕчбЙжЕВЛЭЌЁЃДЫЭтЃЌР§ШчCyclone V GXЯЕСаFPGAЦїМўДјИпЫйGbitДЎааЪеЗЂЦїЃЌЭЈГЃгаЖюЭтЕФВЮПМЕчбЙЃЛMAX10ЯЕСаЦїМўЕФADCЙІФмв§НХЕчТЗвВашвЊЖюЭтЕФВЮПМЕчбЙЃЛвЛаЉДјDDR3ПижЦЦїЙІФмЕФFPGAв§НХЩЯЭЈГЃвВгазЈУХЕФВЮПМЕчбЙЁЁжюШчДЫРрЕФВЮПМЕчбЙЮвУЧЖМПЩвдЙщРрЮЊFPGAЕФИЈжњЙЉЕчЕчбЙЃЌдкЪЕМЪЕчдДЕчТЗСЌНгКЭЩшМЦЙ§ГЬжаЃЌЖМБиаыгшвдПМТЧЁЃ ФПЧАБШНЯГЃМћЕФЙЉЕчНтОіЗНАИжївЊЪЧLDOЮШбЙЦїЁЂDC/DCаОЦЌЛђЕчдДФЃПщЁЃLDOЮШбЙЦїОпгаЕчТЗЩшМЦМђЕЅЁЂЪфГіЕФЕчдДЕчбЙЮЦВЈЕЭЕФЬиЕуЃЌЕЋЪЧЫќЕФвЛИіУїЯдСгЪЦЪЧаЇТЪвВКмЕЭЃЛЖјЛљгкDC/DCаОЦЌЕФНтОіЗНАИФмЙЛБЃжЄНЯИпЕФЕчдДзЊЛЛаЇТЪЃЌЩЂШШШнвзвЛаЉЃЌЪфГіЕчСївВИќДѓЃЌЪЧДѓЙцФЃFPGAЦїМўЕФзюМббЁдёЃЛЖјЕчдДФЃПщМђЕЅЪЕгУВЂЧвФмЙЛгаИќЮШЖЈЕФадФмЃЌжЛВЛЙ§МлИёЭЈГЃБШНЯАКЙѓЃЌдкГЩБОвЊЧѓВЛУєИаЕФЧщПіЯТЃЌЪЧFPGAЕчдДЩшМЦЕФвЛжжзюЮЊМђЕЅПьНнЕФНтОіЗНАИЁЃвдБЪепЖрФъЕФОбщРДПДЃЌдкLDOЮШбЙЦїЁЂDC/DCаОЦЌЛђЕчдДФЃПщЕФбЁдёЩЯЃЌвЛАузёбвдЯТддђЃК Ёё ЕчСїЕЭгк100mAЕФЕчбЙПЩвдПМТЧЪЙгУLDOЮШбЙЦїВњЩњЃЌвђЮЊЕчТЗМђЕЅЁЂЪЙгУдЊЦїМўЩйЁЂPCBУцЛ§еМгУаЁЃЌЧвГЩБОвВЯрЖдЕЭСЎЁЃ Ёё ЖдЕчдДЕчбЙЕФЮЦВЈМЋЮЊУєИаЕФЙЉЕчПМТЧЪЙгУLDOЃЌШчCMOS SensorЕФФЃФтЙЉЕчЕчбЙЁЂADCаОЦЌЕФВЮПМЕчбЙЕШЁЃ Ёё Г§СЫЩЯЪіЧщПіЃЌвЛАуЕчСїНЯДѓЁЂЖдЕчдДЕчбЙЮЦВЈвЊЧѓВЛИпЕФЧщПіЃЌЖМОЁСППМТЧЪЙгУDC/DCЕчТЗЃЌБЯОЙЫќФмЙЛЬсЙЉДѓЕчСїЙЉЕчЃЌЧвЬсЙЉзюКУЕФЕчдДзЊЛЛаЇТЪЁЃ Ёё ЖдгкЕчдДФЃПщЃЌБЪепМћЕНзюЖрЕФЪЧОќЙЄЕШГЩБОВЛУєИаЁЂАхМЖPCBПеМфНЯДѓЕФгІгУжаЪЙгУЃЌЫќЦфЪЕЪЧLDOЮШбЙЦїКЭDC/DCЕчТЗгХЪЦЕФећКЯЁЃ ЭЈГЃЖјбдЃЌЖдгкFPGAЦїМўЕФЕчдДЗНАИЕФбЁдёвдМАЕчдДЕчТЗЕФЩшМЦЃЌвЛЖЈвЊЪТЯШзіКУЧАЦкЕФзМБИЙЄзїЃЌШчвдЯТМИЕуЪЧБиаыПМТЧЕФЃК Ёё ЦїМўашвЊЙЉИјМИЕЕЕчбЙЃЌбЙжЕЗжБ№ЪЧЖрЩйЃП Ёё ВЛЭЌЕчбЙЕЕЕФзюДѓЕчСївЊЧѓЪЧЖрЩйЃП Ёё ВЛЭЌЕчбЙЕЕЪЧЗёгаЩЯЕчЫГађвЊЧѓЃПЃЈДѓВПЗжЕФFPGAЦїМўЪЧУЛгаДЫЯювЊЧѓЕФЃЉ Ёё ЕчдДШЅёюЕчШнИУШчКЮЗжХфКЭХХВМЃП Ёё ЕчдДЕчбЙЪЧЗёашвЊЩшМЦЬиЪтЕФШЅёюЕчТЗЃП ЙигкЩшМЦепашвЊШЗЖЈЕФИїжжЕчЦјВЮЪ§вдМАЕчдДЩшМЦЕФИїжжзЂвтЪТЯюЃЌЦфЪЕдкЦїМўГЇЩЬЬсЙЉЕФЦїМўЪжВсЃЈhandbookЃЉЁЂгІгУБЪМЧЃЈapplication notesЃЉЛђЪЧАзЦЄЪщЃЈwhite paperЃЉжавЛАуЖМЛсИјГіВЮПМЩшМЦЁЃЫљвдЃЌЩшМЦепШєЯЃЭћФмЙЛНЯКУЕФЭъГЩFPGAЦїМўЕФЕчдДЕчТЗЩшМЦЃЌЪТЯШдФЖСДѓСПЕФЙйЗНЮФЕЕЪЧБиаыЕФЁЃ ЫЕЕНЕчдДЃЌвВВЛФмВЛЬсвЛЯТЕиЖЫЃЈGNDЃЉЕчТЗЕФЩшМЦЃЌFPGAЦїМўЕФЕиаХКХЭЈГЃЪЧКЭЕчбЙХфЖдЕФЁЃвЛАугІгУжаЃЌЭГвЛЙВЕиСЌНгЪЧУЛгаЮЪЬтЕФЃЌЕЋвВашвЊзЂвтЬиЪтгІгУжаЪЧЗёгаИєРывЊЧѓЁЃFPGAЦїМўЕФв§НХв§ГіЕФЕиаХКХжЎМфЭЈГЃЪЧЕМЭЈЕФЃЌЕБШЛвВВЛФмХХГ§гаР§ЭтЕФЧщПіЁЃШчЙћТЉНгИіБ№ЕиаХКХЃЌЦїМўЭЈГЃвВФме§ГЃЙЄзїЃЌЕЋЪЧБЪепвВгіЕНЙ§вЛаЉЬиЪтЕФзДПіЃЌШчAlteraЕФCyclone IIIЦїМўЕзВПЕФжабыгаИіНгЕиКИХЬЃЌШчЙћЩшМЦжаКіТдСЫетИіНгЕиаХКХЃЌФЧУДFPGAКмПЩФмОЭВЛИЩЛюСЫЃЌвђЮЊетИіЕиаХКХЪЧСЌНгFPGAФкВПЕФКмЖржаМфаХКХЕФЕиЖЫЃЌЫќВЂВЛКЭFPGAЕФЦфЫќЕиаХКХжБНгЕМЭЈЁЃвђДЫЃЌдкЩшМЦжавВвЛЖЈвЊСєвтЕиаХКХЕФСЌНгЃЌЕчдДЕчТЗЕФШЮКЮЯИаЁЪшКіЖМгаПЩФмЕМжТЦїМўЕФАеЙЄЁЃ дкЮвУЧЫљЩшМЦЕФетИіЪЕбщЦНЬЈЩЯЃЌШчЭМ2.5ЫљЪОЃЌгЩPCЕФUSBЖЫПкНјааЙЉЕчЃЌЭЈГЃПЩвдЬсЙЉ5V/0.5AЕФЕчбЙКЭЕчСїЁЃ5VЕчбЙЪфШыЕНСНИіDC/DCЕчТЗЗжБ№ВњЩњ3.3VКЭ1.2VЕФЕчбЙЃЌDC/DCаОЦЌжЇГжЕФзюДѓЕчСїПЩвдДяЕН3AЃЌЕБШЛЮвУЧЕФFPGAЦїМўЪЕМЪЩЯИљБОВЛашвЊетУДДѓЕФЕчСїЁЃжЎЫљвдВЩгУDC/DCЕчТЗВњЩњ3.3VКЭ1.2VЕчбЙЃЌЪЧПМТЧЕН3.3VЪЧFPGAЕФI/OЕчбЙЃЌвВЪЧАхЩЯДѓЖрЪ§ЭтЩшЕФЙЉЕчЕчбЙЃЌЫќЕФЕчСїЯрЖдНЯДѓЃЛЖј1.2VЪЧFPGAЦїМўЕФКЫЕчбЙЃЌЕчСївВНЯДѓЃЛвђДЫЃЌЫќУЧЪЙгУDC/DCЕчТЗИќКЯЪЪЃЌМШПЩвдБЃжЄНЯДѓЕчСїашЧѓЃЌвВФмЙЛЪЕЯжИќКУЕФЕчдДзЊЛЛаЇТЪЁЃЖј2.5VЕчбЙЪЙгУ3.3VзЊ2.5VЕФLDOЕчТЗЃЌЪЧгЩгк2.5VНіНіжЛЪЧFPGAЕФЯТдиХфжУЕчТЗЪЙгУЃЌЕчСїЯрЖдНЯаЁЃЌЫќЖдзЊЛЛаЇТЪвЊЧѓвВВЛИпЃЌЪЙгУМђЕЅЕФLDOЕчТЗРДЕУИќЁАОМУЪЕЛнЁБвЛаЉЁЃ

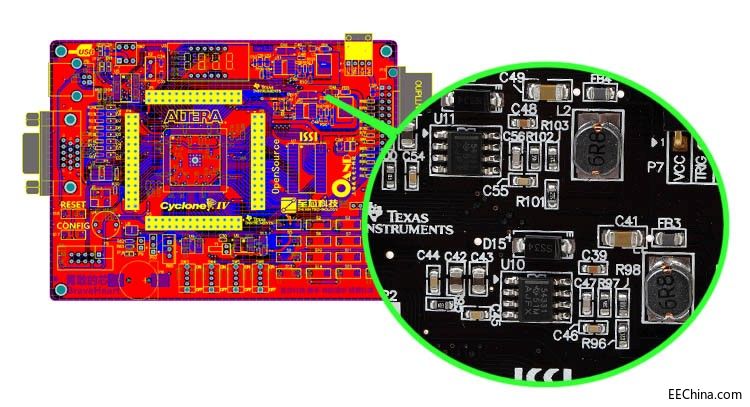

ЭМ2.5ЕчдДЕчТЗЪОвтЭМ ШчЭМ2.6ЫљЪОЃЌетЪЧЕчдДЕчТЗЕФlayoutЪОвтЭМЃЌЮЊСЫЛёЕУИќДѓЕФЕчСїЙЉИјФмСІЁЂИќИпЕФЕчдДзЊЛЛаЇТЪЃЌЮвУЧжЛФмВЛЯЇЪЙгУИќЖрЕФЗжРыдЊЦїМўКЭИќДѓЕФВМАхПеМфРДЁАЭзаЁБЁЃ

ЭМ2.6 ЕчдДЕчТЗЕФlayout |

ЭјгбЦРТл