基于FPGA的数字分频器设计

发布时间:2017-9-5 10:12

发布者:eechina

|

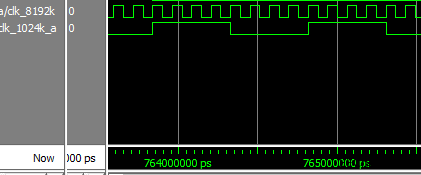

作者:赵厉,张志国,唐芳福 珠海欧比特控制工程股份有限公司,珠海 519080 摘要:在设计数字电路过程中,通常所需的频率要根据给定的频率进行分频来得到。时钟分频又分为整数分频和小数分频,有时还有会有分数分频。当基准时钟与所需的频率成整数倍关系时为整数分频,可以采用标准的计数器实现,也可以采用可编程逻辑器件实现。当基准时钟与所需的频率不成整数倍关系时为小数分频,可以采用小数分频器实现分频。本文通过XC2V1000-4FG456型号的FPGA对8192kHz的基准时钟进行分频,分别得到1024kHz、512kHz、256kHz和1kHz的时钟频率。设计中利用了VHDL硬件描述语言,通过ISE9.1逻辑设计工具和Modelsim6.5仿真工具完成了数字分频器的设计。 关键词:分频器;FPGA;VHDL;Modelsim6.5 1. 概述 随着集成电路技术的快速发展,半导体存储、微处理器等相关技术的发展得到了飞速发展。FPGA以其可靠性强、运行快、并行性等特点在电子设计中具有广泛的意义。作为一种可编程逻辑器件,FPGA在短短二十年中从电子设计的外围器件逐渐演变为数字系统的核心。伴随着半导体工艺技术的进步,FPGA器件的设计技术取得了飞跃发展及突破。 分频器通常用来对某个给定的时钟频率进行分频,以得到所需的时钟频率。在设计数字电路中会经常用到多种不同频率的时钟脉冲,一般采用由一个固定的晶振时钟频率来产生所需要的不同频率的时钟脉冲的方法进行时钟分频。 在FPGA的设计中分频器是使用频率较高的基本设计,在很多的设计中也会经常用到芯片集成的锁相环资源,如用Xilinx的DLL以及Altera的PLL来进行时钟的分频、倍频与相移。在一些对时钟精度不高的场合,会经常利用硬件描述语言来对时钟源进行时钟分频。 分频器是一种基本电路,一般包括数字分频器、模拟分频器和射频分频器。根据不同设计的需要,有时还会要求等占空比。数字分频器采用的是计数器的原理,权值为分频系数。模拟分频器就是一个频率分配器,用带阻带通实现(比如音箱上高中低喇叭的分配器)。射频分频器也是滤波器原理,用带内外衰减,阻抗匹配实现。 随着FPGA技术的发展,基于FPGA技术的硬件设计数字分频器已成为数字系统设计的研究重点。数字分频器通常分为整数分频器和小数分频器。在有些需求下还要分数分频器。 本设计是基于FPGA的数字分频器,通过VHDL硬件设计语言,在Modelsim6.5上对设计的分频器进行仿真验证。 2. 数字分频器的设计 数字分频器的设计与模拟分频器的设计不同,数字分频器可以使用触发器设计电路对时钟脉冲进行时钟分频。分频器的一个重要指标就是占空比,即在一个周期中高电平脉冲在整个周期中所占的比例。占空比一般会有1:1,1: N等不同比例的要求,由于占空比的比例要求不一样,所以采用的时钟分频原理也各不同。在FPGA的数字分频器设计中,主要分为整数分频器、小数分频器和分数分频器。现在分别介绍整数分频器的设计、小数分频器的设计和分数分频器的设计。 2.1 整数分频器的设计 整数分频器是指基准时钟与所需的时钟频率成整数倍关系。整数分频器的分频种类一般包括奇数分频和偶数分频。虽然时钟分频原理会根据时钟分频的要求不同而不同,但均可采用标准计数器原理来实现。 偶数分频器的设计原理较为简单,主要是利用计数器来实现。假设要进行n(n为偶数)分频,设定一个在分频时钟上升沿触发的计数器循环计数来实现。当计数器值为0-((n/2)-1)时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,由此不断循环。 奇数分频器的设计原理与偶数分频的设计方法很相似,都是通过计数器来实现的。如果要进行n(n为奇数)分频,直接设计n进制的计数器即可。还有一种方法就是选择两个计数器cnt1和cnt2,分别在时钟上升沿和下降沿触发计数。cnt1和cnt2均当计数器值为0-((n/2)-1)时,输出时钟信号进行翻转,同时给计数器一个时钟复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,如此进行循环下去。由此可知,计数器cnt1和cnt2的实现方法一样,只是翻转边沿不一样,最终输出的时钟为clkout = clk1 + clk2。 2.2 小数分频器的设计 小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需的小数分频值,分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。 小数分频器有很多种设计方案,但其基本原理是一样的,都是在若干个分频周期中采取某种方法使几个周期多计一个数或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比。还有一种分频方法就是,利用状态机和计数器。假设时钟信号的频率为1khz,需要产生750khz的分频信号,其分频系数为6/8。基本设计思想是,在8个时钟信号中保留6个时钟信号。这种方法是需要预先设定状态机的个数,主要用于已经知道需要使用哪一个小数分频系数的情况下。如果分频系数发生变化,则需要在程序内部进行修改。 双模前置小数分频的设计方法是,假设要进行m,n时钟分频(其中m、n都是整数,且n<10),因为只有一位小数,所以总共要进行10次分频。总的规律是:进行n次m+1分频,10-n次m分频。例如,设计一个分频系数为3.6的分频器,将小数部分的6按倍累加,假设累加的值为a,如果a<10,则进行3分频,如果a<10下一次则加上6。此后,如果a>=10,则进行4分频,4分频过后再将累加值减去4后与10比较以决定下一次分频是4分频还是3分频,这样分频器设计成6次4分频,4次3分频,总的分频值为(6×4+4×3)/(6+4) = 3.6。 2.3 分数分频器的设计 分数分频器的数据输入部分与小数分频基本相同,差别仅在于数码管显示部分显示三位分频系数。由于分数在一定情况下可以转化为小数进行计算,所以分数分频的设计思想与小数分频的很相似。假设进行分频,总分频数由分母m决定,规律是进行n次j+1分频和m-n次j分频。两种分频交替进行的计算方法和小数分频的很类似。累加分结果是大于等于分母还是小于分母决定是进行j分频还是j+1分频。 3. 数字分频器的FPGA设计及仿真 利用FPGA对8192kHz的基准时钟进行时钟分频,分别得到1024kHz、512kHz、256kHz和1kHz的时钟频率,需要分别进行8分频、16分频、32分频和8192分频。在利用FPGA进行设计整数分频器时,通过VHDL硬件描述语言利用计数器方式来实现。 3.1 1024kHz时钟分频 根据所需的时钟频率为1024kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是8倍的整数倍关系,因此需要对8192kHz的晶振时钟进行8分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行8分频的分频器设计。然而8又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-1所示。

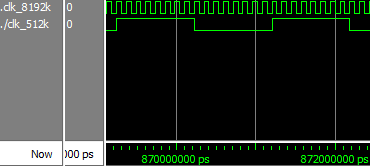

图3-1 1024kHz时钟分频 由图3-1得知,当8192kHz的晶振时钟输入8个时钟,系统输出1个时钟,即一个1024kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-3时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。 3.2 512kHz时钟分频 根据所需的时钟频率为512kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是16倍的整数倍关系,因此需要对8192kHz的晶振时钟进行16分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行16分频的分频器设计。然而16又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-2所示。

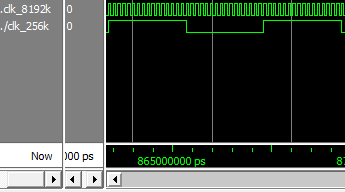

图3-2 512kHz时钟分频 由图3-2得知,当8192kHz的晶振时钟输入16个时钟,系统输出1个时钟,即一个512kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-7时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。 3.3 256kHz时钟分频 根据所需的时钟频率为256kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是32倍的整数倍关系,因此需要对8192kHz的晶振时钟进行32分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行32分频的分频器设计。然而32又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-3所示。

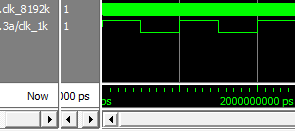

图3-3 256kHz时钟分频 由图3-3得知,当8192kHz的晶振时钟输入32个时钟,系统输出1个时钟,即一个256kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-15时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。 3.4 1kHz时钟分频 根据所需的时钟频率为1kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是8192倍的整数倍关系,因此需要对8192kHz的晶振时钟进行8192分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行8192分频的分频器设计。然而8192又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-4所示。

图3-4 1kHz时钟分频 由图3-4得知,当8192kHz的晶振时钟输入8个时钟,系统输出1个时钟,即一个1kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-4095时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。 4. 结束语 本文给出了基于FPGA的数字分频器设计方法。采用计数器设计方法实现了对8192kHz的基准时钟进行分频,分别得到1024kHz、512kHz、256kHz和1kHz的时钟频率。其他的偶数倍分频也可采用类似的方法分频的到需要的频率时钟。通过在Modelsim6.5仿真工具验证了设计的正确性。 参考文献 [1] 夏宇闻.Verilog数字系统设计教程[M].北京航空航天大学出版社,2008 [2] (美)Parag K.Lala著,乔庐峰等译.现代数字设计与VHDL [M].电子工业出版社,2010 [3] 潘松,黄继业,潘明.EDA技术实用教程[M].科学出版社,2010 [4] 张奇惠,武超,王二萍,蒋俊华,张伟风.基于VerilogHDL的分频器的优化设计[J].河南大学学报(自然科学出版).2007,37(4):343 [5] 王世元,谢开明,石亚伟,陈孟钢,龙正吉.一种新的可控分频器的FPGA实现[J].西南大学学报(自然科学版)2007,29(1):89-93 [6] 刘亚海,林争辉.基于FPGA的小数分频器的实现[J].现代电子技术,2008,28(3):113-117 [7] 蔡晓燕,FPGA数字逻辑设计[M].清华大学出版社,2013 [8] 徐志军,徐光辉.CPLD/FPGA的开发与应用[M].电子工业出版社,2002 [9] 王诚,薛小刚,钟信潮.FPGA/CPLD设计工具[M].人民邮电出版社,2003 [10] 李秋生.一种改进的小数分频器设计方法[J].现代电子技术.2009,08:43-46 [11] 徐德成.任意数分频设计方法[J].科技广场.2007,(11):219-220 [12] 古良玲,杨永明,郭巧惠.基于FPGA的半整数及整数分频器的参数化设计[J].电子器件,2005,28(2): 404-406 |

网友评论