基于J750EX测试系统的SRAM VDSR32M32测试技术研究

发布时间:2017-8-30 16:42

发布者:eechina

|

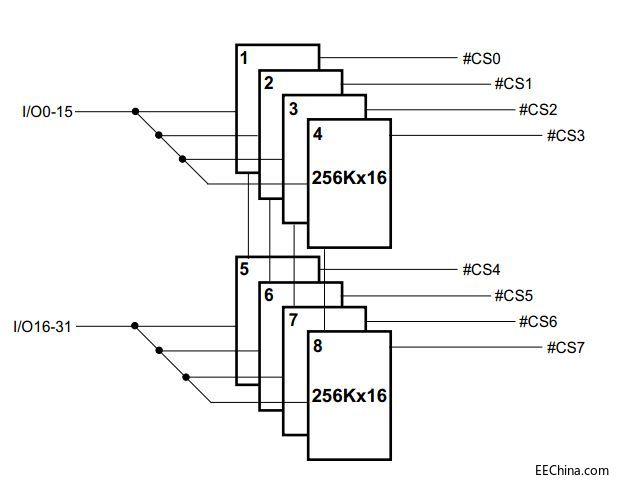

作者:王鑫,王烈洋,占连样,陈像,张水苹,汤凡,黄小琥,李光 摘要: VDSR32M32是珠海欧比特公司自主研发的一种高速、大容量的静态随机器(SRAM)用其对大容量数据进行高速存取。本文首先介绍了该芯片的结构和原理,其次详细阐述了基于J750测试系统的测试技术研究,提出了采用J750EX测试系统的DSIO及其他模块实现对SRAM VDSR16M32进行电性测试及功能测试。另外,针对SRAM的关键时序参数,如TAA(地址变化到数据输出有效时间)、TACS(片选下降到数据输出有效时间)、TOE(读信号下降到数据输出有效时间)等,使用测试系统为器件施加适当的控制激励,完成SRAM的时序配合,从而达到器件性能的测试要求。 关键词:J750EX,VDSR32M32,SRAM,DSIO 1 引言 SRAM静态随机存取存储器是一种具有静止存取功能的内存,不需要刷新电路技能保存它内部存储的数据。它的主要优点是速度快,不必配备刷新电路,可提高整体的工作效率。集成度低,功耗小,相同容量的体积较大,而且价格较高。但在串行低速数据到并行高速数据转换的过程中,存储器起的是数据缓冲作用。为了得到更高的传输速度和更大的传输容量,需要更高的速度和更大容量的存储器。VDSR32M32是珠海欧比特公司研制出的一种高速、大容量的TTL同步静态存储器,内部由8片256Kbit CMOS SRAM组成,实现了由8个存储容量为256K×16bits字节的芯片扩展成容量为1M×32bits的SIP大容量存储器芯片,同时具有设计简单,应用灵活等特点。 2 VDSR32M32芯片介绍 2.1 VDSR32M32的结构 本器件是一种大容量、高速的SRAM。采用了先进的立体封装技术,把8片高速大容量的SRAM分八层进行叠装,组成了总容量为32M bit数据宽度为32位的大容量存储器,具体内部结构见图1. 这种结构不但大大的扩充了存储器的容量和数据位宽,而且还可以在应用时大量节省了PCB板的使用空间。通过应用了立体封装的技术缩短了互连导线,从而降低了寄生效应,使得器件具有高性能、高可靠、长寿命、大容量等的性能特点。图2为VDSR32M32中的任一Block的结构框图,它主要由控制逻辑、存储整列等组成。 VDSR32M32主要特性如下: 总容量:32M bit; 工作电压:3.3V(典型值),3.0~ 3.6V(范围值); 数据宽度:32位; 访问周期:12ns; 所有输入输出兼容TTL电平; 68脚SOP II 封装。

图1 VDSR32M32原理图

图2 VDSR32M32内部Block的结构框图 VDSR32M32立体封装SRAM芯片采用8片型号为R1RW0416DSB-2PI的基片利用欧比特公司的SIP立体封装工艺堆叠而成,分为独立的8个片选信号(#CS0~#CS7),实现了由8个存储容量为256K×16bits字节的芯片扩展成容量为1M×32bits的SIP大容量存储器芯片。各引脚的功能使用说明如下: VCC:+3.3V电源输入端; VSS:接地引脚; A0~A17:地址同步输入端; #LB:低字节选择; #UB: 高字节选择; #OE:输出使能, 数据读取时需置为低,写时置为低; #CE0/#CE7:片选信号,低电平有效时选中该片; DQ0~DQ32:数据输入/输出脚; #WE: 写使能信号. 2.2 VDSR32M32电特性。 表 1 产品电特性

2.3 VDSR32M32功能操作 表 2 器件功能真值表1)

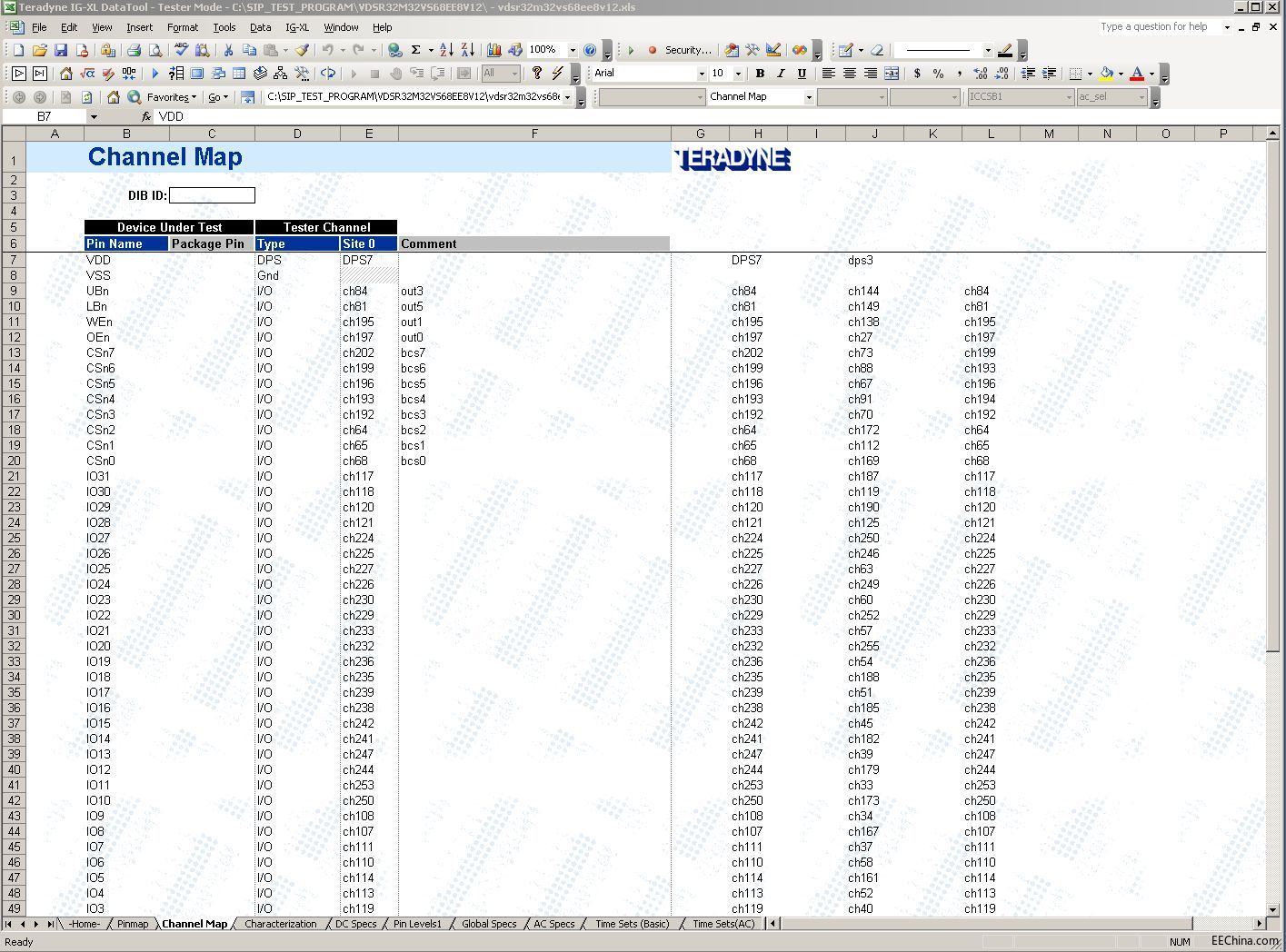

注:1)、 X=任意, H=高电平, L=低电平, Z=高阻。 2)、#CSn有效为#CS0、#CS1、#CS2 #CS3、#CS4、#CS5、#CS6和#CS7同时有效。 3 VDSR32M32测试方案 在本案例中,我们选用了Teradyne公司的J750测试系统对VDSR32M32进行全面的性能和功能评价。该器件的测试思路为典型的数字电路测试方法,即存储阵列的读写功能测试及各项电特性参数测试。 3.1 J750测试系统简介 J750测试系统是上海Teradyne公司生产的存储器自动测试机,Teradyne J750的高容量并行测试能力的设备测试效率可以高达95%。零脚印系统允许测试头里面可以容纳多达1,024 个输入/输出(I/O)通道,提供一整套选项,包括转换器测试选项、内存测试选项、冗余分析和混合信号选项。这些极大地拓宽了测试能力范围。该系统还有IG-XL (TM) 测试软件,把最新PC技术和Windows NT操作系统的力量和性能与标准的Windows工具(比如Microsoft Excel 和Visual Basic)融合在一起。 3.2 DSIO简介 DSIO即为Digital Signal Input/Output(数字信号输入/输出)模块的简称,它能使J750EX对数字信号进行发送(source)、抓取(capture)及分析(analyze)等操作。此模块的应用方法十分灵活,转换测试需要输入的高速数字波形,器件寄存器需要动态写入的数字数据,独立存在于数字测试矢量中的数据发送,以及对上述各类数据的抓取操作均可以使用该模块顺利完成。对VDSR16M32的测试就采用了DSIO可以独立于测试矢量,对个别管脚单独发送所需的数字数据这一功能。 3.3 采用J750测试系统DSIO模块测试方案设计 1) 硬件设计 按照J750测试系统的测试通道配置规则,绘制VDSR32M32的测试转接板,要对器件速率、工作电流、抗干扰等相关因素进行综合考量。 2)软件设计 考虑到使用该模块为器件提供需要施加激励信号的特殊性,我们采用了 J750测试系统基于Visual Basic 和Microsoft Excel工具,在IG-XL测试软件下对程序进行编写,具体实施步骤如下: A. 按照J750的标准编程方法,先完成对VDSR32M32的Pin Map、Channel Map、等芯片管脚进行定义;

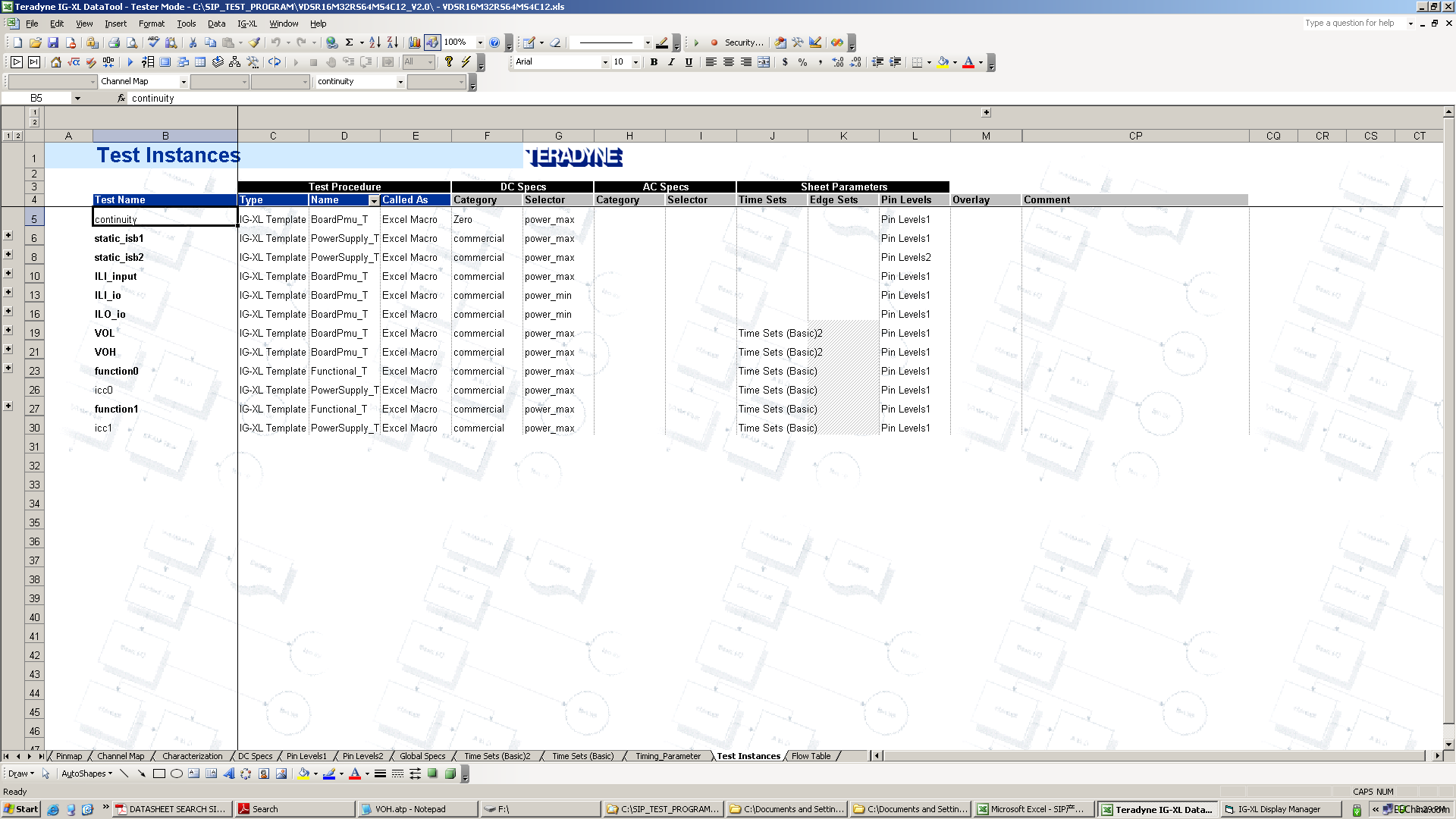

引脚定义 B. 对DC测试项进行定义包括DC Spec、Pin Levels等,此项不需进行Pattern编辑; C. 编辑pattern所使用的function测试项VOL,VOH,时序参数包括AC Spec、Time Sets、Test Instance等编辑。

测试界面编辑 3.4 VDSR16M32的功能测试 针对SRAM等存储单元阵列的各类故障模型,如阵列中一个或多个单元的一位或多位固定为0或固定为1故障(Stuck at 0 or 1 fault)、阵列中一个或多个单元固定开路故障(Stuck open fault)、状态转换故障(Transition fault)、数据保持故障(Data maintaining fault)、状态耦合故障(Coupling fault)等,有相应的多种算法用于对各种故障类型加以测试,本文采用棋盘格CHECKBOARD、全0、全1的测试吧算法。 不论何种算法,对于大容量的存储器来说,测试矢量的长度也会随其容量的增加而递增,相应地,测试时间随之增长。对此,J750EX测试系统的DSIO模块可以提供一个很好的解决方案。 3.5 VDSR32M32的电性能测试 针对SRAM类存储器件,其电性测试内容主要有管脚连通性测试(continuity)、管脚漏电流测试(leakage),管脚工作电流测试(ICC)、休眠电流(ISB)、输出高/低电平测试(voh/vol),时序参数测试(TAA、TACS、TOE等)。 1) PMU简介 PMU即为Parametric Measurement Unit,可以将其想象为一个电压表,它可以连接到任一个器件管脚上,并通过force电流去测量电压或force电压去测量电流来完成参数测量工作。当PMU设置为force 电流模式时,在电流上升或下降时,一旦达到系统规定的值,PMU Buffer就开始工作,即可输出通过force电流测得的电压值。同理,当PMU设置为force 电压模式时, PMU Buffer会驱动一个电平,这时便可测得相应的电流值。SRAM 器件的管脚连通性测试(continuity)、漏电流测试(leakage)、voh/vol测试均采用这样的方法进行。 2) VDSR32M32的工作电流测试((ICC)、休眠电流(ISB)、时序参数测试(TAA、TACS、TOE) VDSR32M32的休眠电流测试不需要编写pattern测试,而工作电流测试需要测试pattern,,需要注意的是测试静态电流时器件的片选控制信号需置成vcc状态,测试动态电流时负载电流(ioh/iol)需设为0 ma。 对时序参数进行测试时, pattern测试是必不可少的,并需要在Time Sets ,Characterization进行相应的时序参数设置。 下图为测试项目界面:

参考文献: [1] Neamen,D.A.电子电路分析与设计——模拟电子技术[M]。清华大学出版社。2009:118-167. [2] 珠海欧比特控制工程股份有限公司. VDMR4M08使用说明书[Z]. 2013. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

网友评论