美新内存技术号称可替代DRAM/flash

发布时间:2011-1-27 08:18

发布者:1770309616

|

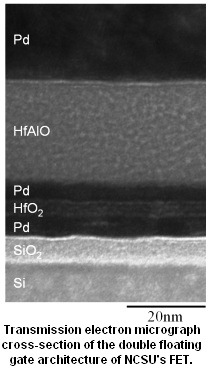

美国北卡罗莱纳州立大学(North Carolina State University)最近宣布开发出一种“通用(universal)”内存技术,号称结合了DRAM的速度,同时具备闪存的非挥发特性与密度优势。 研究人员表示,这种新内存技术采用了双浮动栅(double floating-gate)场效晶体管(FET),能允许计算机将目前未被存取的内存断电,因此能大幅降低包括可携式/桌上型PC与服务器、数据中心等各种计算机的耗电量。“采用我们的新式双浮动栅架构之内存,速度应可媲美DRAM,但需要经常刷新(refresh);其密度则可达到闪存的水平。”北卡罗莱纳州立大学电子工程教授Paul Franzon表示。 双浮动栅是以直接穿隧(direct tunneling)方式储存电荷来代替位,而不是像闪存那样透过热电子注入(hot electron injection),并因此能以较低的电压运作。由于堆栈中的第一个浮动栅会泄漏(leaky),因此需要跟DRAM差不多的刷新频率(16毫秒);但透过提高电压,其数据值(data value)可被转移到第二个浮动栅——其角色更类似传统闪存,可提供较长期间的非挥发性储存。 当计算机在运作中,可正常使用双浮动栅FET作为主存储器;在计算机闲置时,其数据值就能转移到第二个浮动栅,以将内存芯片断电。当计算机需要再次存取所储存的数据值,第二个浮动栅会快速将所储存的电荷转回去第一个浮动栅,并恢复正常运作。“我们相信这种新内存组件,能实现依运算需求比例式分配功率(power-proportional)的计算机,让内存可在低使用率期间被关闭,又不影响系统性能。”Franzon表示。

双浮动栅FET内存架构 到目前为止,研究人员仅在新的FET设计采用该种双浮动栅架构,现在正进行周期性测试,以确保可从浮动栅进行内存储存与复原,且不会造成最终使内存组件耗损的疲乏效应。举例来说,如闪存是在热载子注入时采用非常高的电压,因此该类内存组件仅能耐受约1万次的读/写周期。双浮动栅FET采用低电压,不过还需透过周期性测试才能确定该类组件是否会出现过度疲乏效应。 如果测试组件通过了周期性测试,研究人员接下来将以该架构打造真正的半导体内存;该任务预定在2012年开始进行。 翻译:Judith Cheng |

网友评论