超宽带无线通信中LDPC码硬件仿真实现

发布时间:2010-12-6 12:54

发布者:techshare

|

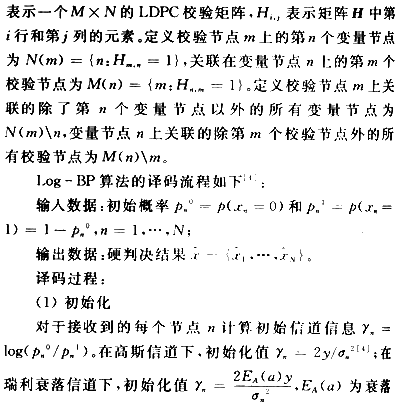

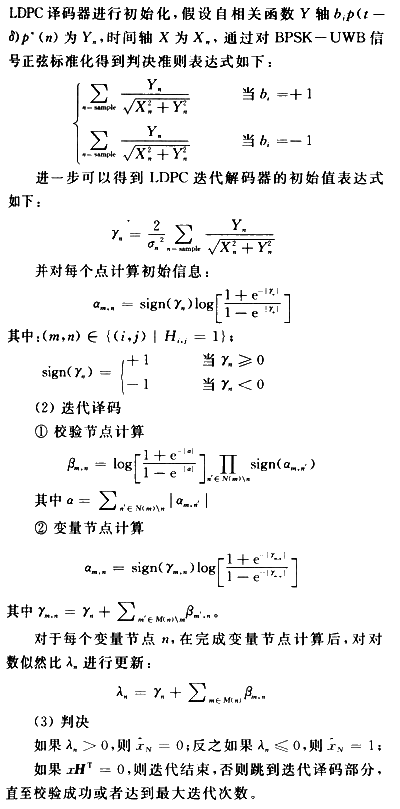

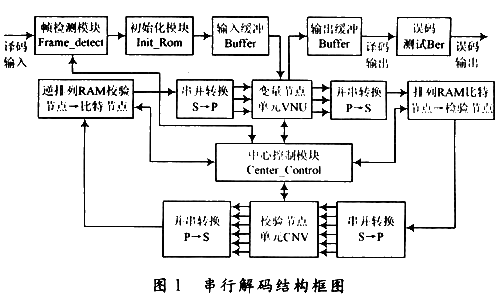

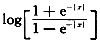

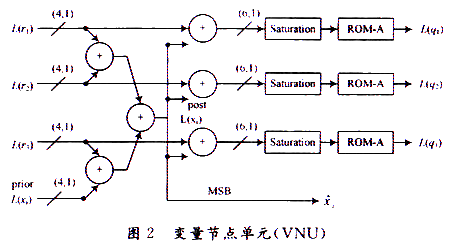

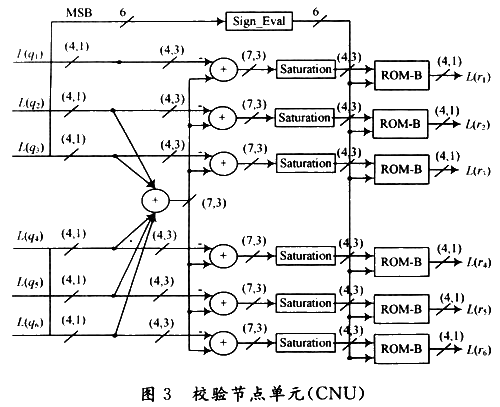

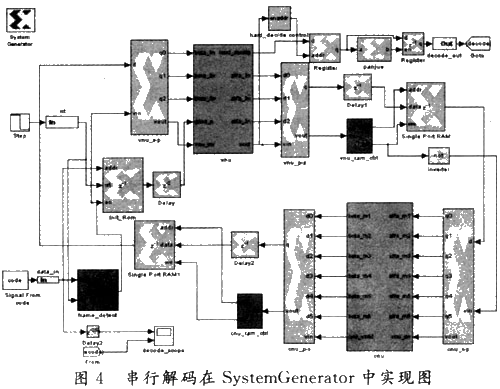

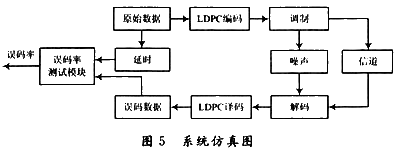

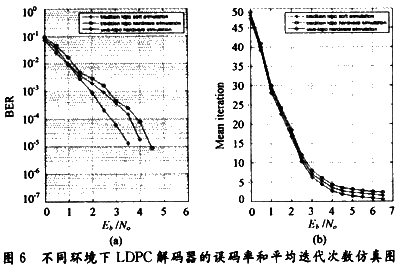

1 引 言 码长较长的低速LDPC编码在信噪比较低的应用场合呈现出其他编码无法匹敌的优势,已经证明非规则的LDPC码性能甚至优于Turbo码高速LDPC编码性能也比较好.尤其是在磁记录等一些应用场合,码长较短的高速LDPC编码有着较为广阔的应用前景。在不久的将来,LDPC编码将用于更多高速高质量的通信场合。而UWB通信技术因其传输速率高、功耗低等优点在短距离的网络中得到越来越多的关注。特别是UWB无线通信因其具有良好的时域可分辨性尤其适合于密集多径环境中的短距离多用户接入。本文在SvstemGenerator中对LDPC码整个编译码系统进行了参数化的硬件实现,并构建了超宽带通信系统LDPC码硬件仿真平台,验证了LDPC码在UWB通信中的优异性能。 2 UWB~LDPC的译码算法及不同环境下的初始化方法 LDPC码采用置信传播算法(BP)可以有效地解码,由于存在大量的乘法运算,直接采用BP算法会导致很高的硬件复杂性,因此采用了对数(Log)运算将乘法变换为加法,这种算法叫做Log-BP算法。实际上,BP和Log-BP算法实现的是同样的译码准则。 首先定义几个可能用到的几个变量及符号的意义:H  因子的统计平均值,当瑞利信道平均能量为1时,Ea(a)=0.8662。在UWB通信中,采取文献给出的混合软标准化算法,利用UwB信号的归一化的自相关值对  3 LDPC码硬件解码结构 由于并行解码性能与串行解码在性能上并无差别,只是占用更多的硬件资源来换取更快的速度,并且每一种并行结构只能针对具有某一特定校验矩阵的LDPC码。所以本文就以串行解码硬件实现方式进行实现分析。 3.1串行解码结构 串行解码结构图如图1所示,帧检测单元检测到帧头后表示后面的输入有效,启动译码器。初始化单元完成译码器的初始化;校验节点单元和变量节点单元分别完成校验节点和变量节点的更新计算,其中校验节点单元还要判断是否满足校验条件或达到最大迭代次数;两个RAM完成特定校验矩阵迭代信息的位置置换;中心控制模块完成整个系统的流程控制;缓冲模块是为了达到速率匹配和能够连续译码而设置的。  (1) 初始化单元 初始化信息是整个译码器最重要的译码依据,在对一帧初始化信息进行译码判决的过程中,迭代运算不断调用的初始化信息必须保持不变,因此采用存储器将初始化信息进行存储,在一帧的时间内保持不变。一帧时间后将开始接收新的信息为下一帧译码做准备。初始化单元在SystemGenerator中实现比较简单,只要用一个ROM存储所需的初始化信息,然后根据量化后的软信息查表即可。 (2)VNU(变量节点)单元 VNU的功能为计算"变量一校验"信息以及更新后验对数似然比。其硬件实现图如图2所示,3个"校验一变量"信息和1个比特初始化信息相加减去相对应的1个"校验一变量"信息所得到的值舍人处理后作为查找表运算的输入,查找表用于计算公式  ,最后将查找表运算结果按符号位正负输出至CNU处理单元,硬判决位输出至校验单元进行奇偶校验。  (3)CNU(校验节点)单元 CNU的功能为计算"校验一变量"信息。CNU实现与VNU基本相似,6个"变量一校验"信息相加减去相对应的1个"变量一校验"信息所得到的值舍入处理后作为查找表运算的输入,最后将查找表运算结果按计算的符号位正负输出至VNU处理单元。由于是二进制系统,本文采用异或运算代替乘法运算计算符号位,其硬件实现图如图3所示。  3.2 串行解码在SystemGenerator中的整体实现 串行解码在SystemGeneratot中的整体实现如图4所示,其中frame detect实现图1中的帧检测模块用来启动译码器,VNU,CNU完成变量节点和校验节点更新的计算,2个单口RAM通过读写和地址的控制完成迭代信息的位置置换,其置换地址是预先在软件中计算得出存在ROM中的。这种串行解码结构比较灵活,只需要改变ROM中的读写地址就可以适用于不同的LDPC码(校验矩阵的维数,行重、列重必须相同),而对于每个LDPC码其地址置换信息只需计算一次即可。原始信息经过延迟用以与解码后的数据比较。  4 UWB-LDPC的SystemGenerator参数化硬件仿真 4.1 系统仿真的总体框图 系统仿真的总体框图如图5所示,原始数据通过LDPC编码和调制,通过信道加上噪声,然后解调后的量化软信息进入LDPC译码器进行解码,由于编码和解码都需要一定的时间,因此原始数据必须经过延时后才能与译码数据进行比较和计算误码率。  4.2 仿真环境 我们在SystemGenerator环境下实现了串行和并行两种解码方式以及不同初始化方案的LDPC码,整个实现都采用参数化方式。为了方便验证性能,本文还建立了VC仿真界面来设置不同的参数。SystemGenerator是DSP高层系统设计与Xilinx FPGA实现之间的"桥梁",他在Matlab/Simulink的环境下完成算法的建模,然后生成相应的工程。ISE可对工程进行仿真、综合、最后完成算法的硬件化。仿真环境和参数设置见表1。  其中高斯信道的硬件模拟是采用文献的BoxMuller算法。仿真采用蒙特卡罗仿真方法,LDPC解码在不同环境下的BER性能和迭代次数如图6所示。  图6(a)表示的是误码率仿真图,图6(b)表示的是平均迭代次数仿真图。仿真结果表明,对于传统的LDPC码采用硬件仿真的性能由于量化的影响略差于软件仿真,但采用了文献改进初始化方案的UWB-LDPC的硬件仿真性能要好于软件仿真的传统LDPC编码方式。尤其是信噪比大于1.5dB时,UWB-LDPC的BER性能有较大的改善,在10-4时大约比传统的LDPC大约有1.2 dB的编码增益,平均迭代次数也有所减少。因此改进的LDPC码比传统的LDPC码更能满足UwB通信需求。 5 结语 本文对LDPC码在UWB通信中的应用做了探索,整个仿真都在SystemGenerator中参数化实现并构建了硬件仿真环境,为LDPC码在UWB通信中的应用和实现进行了有益的尝试。 |

网友评论