通用DSP的RISC核心开发单处理器VoIP

发布时间:2010-11-26 18:39

发布者:designer

|

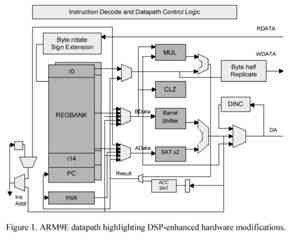

各种服务不断匯整至IP网路环境,促使业者开发各种创新的Voice over IP (VoIP)终端产品,包括IP电话、商用与家用VoIP闸道器以及无线IP电话等。市场亦开始朝向将IP系统与语音功能整合的方向发展,例如:PDA等掌上型装置、汽车、全球卫星定位系统以及其它装置。虽然某些具备更高密度语音频道的系统仍需搭配传统的多重处理器与独立的专属RISC与DSP核心,但更多的设计方案在面临成本、功耗及复杂度持续紧缩的限制下,採用单处理器架构更能达成最好的功效。此外,同业竞争压力以及急迫的上市时程,更激发系统设计业者对完整单处理器VoIP平台的迫切需要,协助业者克服不同处理器之间的整合挑战。 单处理器VoIP设计方案能够协助业者达到成本、功耗、效率及上市时程等整体目标。然而,使用单一元件取代独立式DSP尚须克服各种效能上的问题,各种语音处理演算,例如:支援语音压缩与解压缩的各种ITU-T相容语音编/解码器、Line Echo Cancellation、Voice Activity Detection (VAD)以及Comfort Noise Generation (CNG),都可能衍生出可观的讯号处理需求。此外,处理器核心亦须处理各种电信演算作业,例如:DTMF、拨号音产生、来电显示功能、服务品质(QoS)、使用者介面功能(显示、播号键、铃声等)以及连结外部应用系统的API介面。 由于即时效能的确切性对语音应用至关重要,故研发人员不能仅在标准型RISC核心上重新建置现有的DSP应用,就希望达到最佳的效能结果。一套成功的单核心VoIP系统须结合各种DSP导向的强化方案,作为RISC硬体的基础,并开发各种软体的创新化最佳方案,以充份发挥处理器功能。以下文章将探讨HelloSoft 如何运用ARM9E(tm)系列处理器核心与各项DSP强化元件,达成上述的各项目标。 核心中的DSP强化技术 建立一套可行的单处理器VoIP平台,首先必须选择适合的RISC核心负责各种讯号处理功能。HelloSoft的参考设计方案中採用ARM926EJ-S(tm),主要原因即为该处理器核心的DSP延伸元件直接嵌入RISC处理器的架构中,其内部的特殊改良设计包括单週期16x16 与32x16 Multiple Accumulate (MAC) 功能、饱和演算函式(例如:saturating add、saturating double add及saturating subtract等功能)以及Count Leading Zeros (CLZ) 指令。这些强化指令可用来迅速开发稳定的控制迴圈以及bit-exact的精准演算法,满足各种先进讯号处理系统的需求,例如:语音编/解码器、迴音消除等。CLZ功能针对固定小数点演算与除法运算进行改良(如图1所示)。  图1 DSP强化延伸技术避免大幅变更核心成熟的五阶式管线以及Harvard记忆体架构,因此对硬体资源的冲击能够降至最低程度。此套技术并未增加暂存器或状态,也为增加对暂存器的使用限制。ARM9E系列资料路径仅增加少量的区块,包括一套高速32x16 乘数器、CLZ区块以及两组饱和运算区块。因此,ARM926EJ-S核心的运作状况与其他ARM9核心的效能息息相关(ARM9核心採用0.13微米原生型制程,提供220MHz以上的时脉速度)。 ARM9E系列延伸元件亦与其它ARM系列核心中的DSP延伸元件相容,例如:ARM10E(tm)系列及ARM11(tm)系列。这种特性为研发业者提供一套稳固的基础,协助他们建置高效能、低功耗、单处理器型的VoIP系统,并提供最佳化的研发弹性及新技术转移升级的管道。 人工开发创造出的DSP软体效率 开发高效率VoIP程式码不仅只是将现有的DSP演算法重新建置在RISC核心。由于DSP功能原本就极为依赖处理器,并且须用组译语言撰写,才能充份发挥硬体功能。因此,除了採用ARM9E系列DSP延伸技术外,VoIP函式皆以人工撰写,以彻底发挥底层ARM9E系列处理器的资源,打造出仅需17MHz的频宽即可建置G.729AB codec的优异系统,同时,G.168/16ms线路迴音消除则仅需15MHz的频宽。 目前在专属的DSP处理器上建置语音处理演算法的技术已变得更为简便,因为现今的DSP硬体通常拥有足够的爆发管线处理功能,能够克服一定程度的软体低效率问题。由于DSP透过单一指令同步执行多组作业,因此软体设计师在处理迴圈的序列及时序,或是考量载入资料数量上不需花费太多心思。相较之下,在DSP优化的RISC处理器上建置各种VoIP函式,必须彻底掌握关键的硬体相关议题,如:资料流、迴圈时序、跨迴圈排序以及资料载入的效率等。 ARM9E 系列较独特的优点为其32x16 MAC能够处理暂存器中的32位元资料以及两组独立的16位元运算元。除了为许多包含传统16位元运算法的DSP函式运算提供相容的环境外,32x16 MAC架构亦提供最佳化的资料载入效率,能有效利用处理器的暂存器。相较于其它32位元的RISC架构,软体能运用ARM9E系列元件中的32x16 MAC,协助整体资料载入效率提高4倍。 RISC建置方案中所需的程式记忆体数量虽然高于传统的DSP,但是单处理器型的ARM9E系列元件所打造的VoIP设计方案却不需要使用大量的晶片内部记忆体支援各项DSP功能。研发业者可运用低成本的记忆体资源,大幅降低单核心ARM926EJ-S处理器建置方案的整体记忆体与功率成本,这些资源包括晶片外部的SRAM搭配较小的晶片内部快取等。举例而言,参考设计方案中的8K位元组指令与资料快取就能为两组标准型VoIP通路提供充裕的处理频宽。 HelloSoft的语音演算法在载入资料时能降低35%至40%的耗用资源,这是因为其智慧功能可自动中止与重新调整处理迴圈,提升可用性以及重复使用资料的可能性,同时也提高ARM9E系列16位元MAC处理资源的使用效率。此外,HelloSoft的语音演算法针对特定的运算作业使用预先储存的数值与资料元素,以降低整体运算的负荷。 ARM9E架构的另一项优点为具有自动递增功能的计数器(pointer),运用该项功能能够在每次资料载入运作时均省下两个週期。该项功能对建置标准型VoIP函式相当重要,例如:在G.729AB语音编/解码器中,演算的速度达每秒1千万次MAC,此时若能使用自动递增计数器,则代表着每秒能节省200万个週期。 除了独立的指令与资料快取外,ARM926EJ-S处理器核心亦建置Tightly Coupled Memories (TCM)记忆体。Hellosoft建置的DSP演算法大量运用这些TCM作为暂存RAM,能够有效率地存取经常使用的资料区段,因此能排除关键密集运算迴圈中发生快取错失的可能性。 系统层级的成本缩减以及设计效率 在ARM9E系列核心上的DSP子系统建置语音编/解码器、迴音消除、VAD以及其它讯号处理功能,能够协助HelloSoft参考解决方案将所有VoIP子系统结合成单一处理器架构(如图2所示)。该架构的重要元件包括DSP子系统、服务品质(QoS)、拨号讯号与管理以及所有其它高阶系统功能,例如:GUI图形介面、平台管理以及IP网路介面层。 由于不须使用独立的DSP,单处理器VoIP电话建置技术至少能减少5至10美元的零组件成本。此外,在相同的处理器环境下开发DSP程式、讯号堆叠以及作业系统功能,更可造就出直接且强固的建置方案。 ARM926EJ-S 核心内建的记忆体管理单元(MMU)协助设计方案能够搭配像Embedded Linux 与WinCE等作业系统。Hellosoft的设计使用SIP与RTP通讯协定堆叠搭配VoiceOS(tm)架构。在参考设计方案中,这些与作业系统独立的通讯协定,运用开放原始码的嵌入型Linux核心进行建置,因此更能有效运用硬体资源,且能调针对不同的作业系统/即时作业系统环境调整基础架构,其中包括VxWorks与WinCE等作业系统。 Hellosoft的VoiceOS是一套系统层级的架构,提供精简的抽象层,整合DSP子系统、通讯协定堆叠、媒体处理功能,并提供连结至OS与ARM9E系列处理器硬体平台的介面,因此能简化移至其它作业系统与ARM系列硬体平台的工作。VoiceOS亦提供一套弹性的抽象层,经过扩充后可支援各种新功能与介面,并且在各种IP系统中建置"voice as a service"的语音功能。  图2 能够支援超低成本终端装置,且能配合其它装置匯整各种语音服务的高效率解决方案产品将会广为VoIP市场採纳接受。这些解决方案须依赖单核心VoIP处理平台,协助系统设计师能因应紧缩的成本、功耗以及产品尺寸的限制,同时缩短产品研发週期以及产品上市时间。 |

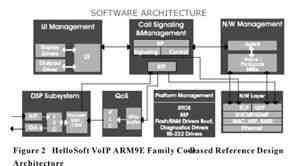

网友评论