基于SoC的实时信号处理系统中存储系统的容错设计

发布时间:2010-11-18 11:44

发布者:eetech

|

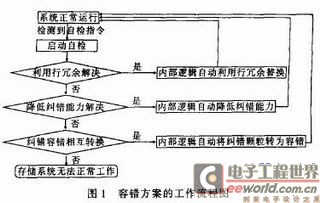

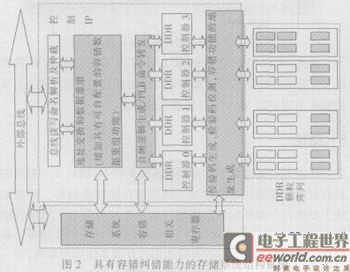

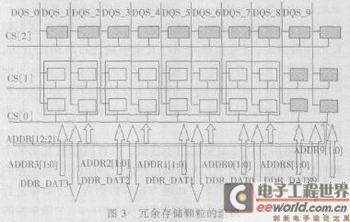

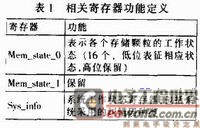

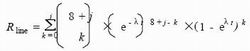

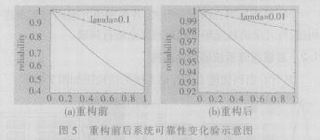

在现代信息社会中,嵌入式系统由于其灵活性及方便性得到了越来越广泛的使用。采用SoC技术可以将整个系统集成到单个芯片之中,其具有体积小、重量轻、功耗小、IP复用等优点。SoC技术目前正成为嵌入式实时系统发展的一个趋势,得到越来越广泛的应用。 系统的纠错和容错能力具有十分重要的意义。这里的容错是指当部分存储器件损坏无法工作时,系统可以有效地利用冗余器件,通过硬件检测或软件指令配置,使存储系统能够继续正常工作。纠错是指当读写数据中出现一位或多位数据出错时,系统自动计算出正确数据的机制,通常情况下,是通过被动硬件冗余防止故障造成差错。常用的方法有三模冗余(TMR)、N模冗余、表决技术等。但此类方法所需附加硬件多,花费代价非常昂贵,同时造成功耗、重量及体积增大很多。当系统发生故障时,通过对整个系统进行替换来保证整个存储系统的可靠性;另一方面,此类方法由于欠缺灵活性,如果多个冗余部分同一位置上的芯片都发生故障,则整个系统仍然无法使用,备份效率也不是很高。 本文针对潜入式实时数字信号处理系统的特点,重新组织DDR存储颗粒的结构,添加冗余颗粒和相关寄存器,改写控制IP,设计了一种新的具有容错纠错自适应功能的二级冗余存储体系结构。它仅需增加少量的冗余器件就可以容忍系统中较多数目的器件故障。在系统没有故障的情况下,存储颗粒可以采用海明码等EDAC码进行纠错;当系统中部分器件出现故障时,系统可以通过软件配置或硬件自动检测,自动利用冗余模块进行容错;当故障进一步增多时,可以适当降低系统的纠错能力,若错误过多,还可以将原先用于纠错的颗粒改为用于容错,使系统能够继续正常地工作。通过数学模型的量化分析,新的存储系统容错方案可以有效地提高存储系统的可靠性。 存储系统容错方案系统结构 容错存储系统工作流程 冗余存储颗粒排放方式采用二级冗余的组织形式,整个存储系统容错方案的工作流程如图1所示。  该容错方案具有以下几个特点: (1)可变的纠错能力。系统支持海明码或CRC等EDAC码,并且当系统出现部分不可逆转故障时,可以自动降低纠错能力。比如,原先系统可以支持每16bit纠1bit错的能力,当存储颗粒出现部分错误时,可以降低为每32bit纠1bit错。 (2)系统自检和容错系统自修复。当系统出现不可逆转故障时,系统可以通过简单的软件命令实现系统错误自检,并自动利用冗余模块启动容错功能,使系统仍然保持正常工作。 (3)纠错能力与容错能力之间的转换。当系统故障的模块过多,冗余模块已经不能保证系统的正常工作,则系统可以自动将部分原先用于纠错的存储颗粒改为用于容错功能。这时,系统的纠错能力会下降或被放弃,但至少能保证系统继续基本正常的工作。 (4)采用行列二级冗余形式,首先利用冗余的行冗余进行纠错,行冗余消耗完毕再利用列冗余进行纠错。 容错存储系统的硬件支持 具有容错纠错能力的存储系统的结构图如图2所示。存储系统的容错方案和不考虑容错的存储系统相比,需要在原有模块的基础上进行修改并增加一些设计。主要包含以下几个方面: (1)增加存储颗粒。为了实现存储系统的容错和纠错能力,增加一定数量的存储颗粒是必须的。在存储颗粒阵列中增加冗余的行列按照行列的二级冗余存储形式组织。为了适应SoC实时信号处理系统的特点,需要对存储系统颗粒阵列的信号连线进行有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持包含纠错容错转换的总体方案。  (2)在寄存器堆中为容错系统分配一定的寄存器地址空间。这些寄存器地址空间由多个部分组成,主要包括系统工作状态寄存器,记录系统各个存储期间的状态;系统纠错方案配置寄存器,配置系统可以采用的纠错方式和纠错能力。 (3)增加纠错码编码解码模块具有容错功能的地址生成。纠错码可以采用多种方式,如海明码、CRC码等。具有容错功能的地址生成模块使系统可以根据容错寄存器的内容,重新生成数据的写入地址和读出地址。 (4)增加自测逻辑生成模块。当软件命令配置了寄存器开始进行自检时,自测逻辑不再处理总线上接收的命令,自动生成测试用代码和地址进行写读检测,使系统可以根据对存储颗粒的工作状态进行有效的分析,并且当发现硬件故障时,就修改寄存器空间中的相关寄存器,以便系统自动启动纠错和容错功能。 (5)修改地址变换和数据重组功能模块。修改后的数据重组需要依据寄存器空间中的故障情况对数据进行重新组织,以便达到容错和纠错的功能。 冗余存储颗粒的组织 为了实现存储系统的容错,在存储颗粒阵列中采用行列二级冗余组织模式。但是根据SoC系统的特点,需要对存储系统颗粒阵列的信号连线进行有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持包含纠错容错转换的总体方案。设计具有纠错容错功能的存储系统主要需要考虑以下几个方面:①系统的纠错能力。②系统的容错能力。由于存储系统受到辐射的影响,可能会发生不可逆转的硬件错误,这时候可以启动系统中的冗余模块来实现容错功能。容错系统正常工作的概率是系统容错能力的衡量标准。③冗余存储颗粒的数目。加入冗余颗粒是实现容错存储系统的必要条件,但是冗余颗粒的位置、连接方式和控制策略等方面都会影响整体的容错能力,用尽量少的冗余存储颗粒实现尽量强的容错功能是系统的设计目标。④需要增加的管脚数目。存储颗粒的数目以及存储颗粒的组织方式都会影响实时信号处理系统需要外连的管脚数目。 在综合考虑了以上四个方面以后,形成了具有容错纠错的存储系统中颗粒的排放方式。在原系统中,共有16片512Mbit的存储颗粒,组织方式如图3所示。  在容错颗粒组织方式中,冗余存储模块的基本排放采用的是行列二级冗余模式。为了适应实时信号处理器的特点,新方案对存储系统颗粒阵列的信号连线进行了有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持了包含纠错容错转换的总体方案。设在系统中增加i排j列存储颗粒,则用Mem(i,j)表示此时的容错存储系统。信号线所需要的改动包括如下几个部分: (1)每列的颗粒。需要新的8bit数据线,新的地址线低2bit,每列增加一根DQS信号线。 (2)每排增加的颗粒。数据和地址与已有的每排颗粒复用,每排增加一根CS片选信号。 (3)除CS之外,所有颗粒共用所有控制信号。存储系统增加冗余存储颗粒后,存储颗粒、信号连线和所占管脚都需要相应地增加。Mem(i,j)存储系统中关于颗粒需要增加的资源包括:①共需要8i+2j+ij个冗余颗粒。②共需增加i根CS信号,j根DQS信号,2j根低位地址信号,8j根数据信号。这样对于实时信号处理器,共需增加管脚数为i+11j,Mem(i,j)存储系统所具有的容错能力以及Mem(i,j)的选择将在第4节进行详细讨论。 逻辑设计对容错的支持 为了实现纠错容错方案,必须在逻辑设计上作出相应的改动,主要包括:①为容错系统分配一定的寄存器地址空间。②增加纠错码生成、纠错码解码模块,具有容错功能的地址生成。③增加自测逻辑生成模块。④修改地址变换和数据重组功能模块。 容错系统的相关寄存器 为了实现整个存储系统的容错和纠错,需要在寄存器堆中为容错系统分配一定的寄存器地址空间。这些寄存器地址空间由多个部分组成,主要包括:系统工作状态寄存器,记录系统各个存储期间的状态;系统纠错方案配置寄存器,配置系统可以采用的纠错方式和纠错能力。相关寄存器的功能定义如表1所示(以Mem(i,j)为例)。  数据重组和地址重新生成 该纠错容错逻辑采用了多种方法进行容错,主要包括采用行冗余模块实现容错、降低纠错能力进行容错、将用于纠错的模块用于容错等。当自检模块发现存储颗粒出现故障时,将Mem_state寄存器的相应位置为1。而存储系统的数据组合以及地址生成都是与Mem_state寄存器相关的可配置逻辑。 (1)采用行冗余模块实现容错。当自测逻辑发现某个颗粒出现故障时,首先选择采用行冗余模块进行容错的方法。CS片选信号可以看作地址信号的一部分,当寄存器Mem_state中存在一位为1,则出现故障的颗粒所在的存储颗粒行就会被关闭(拉高CS信号),同时打开冗余行(拉低CS信号),其他信号不变。 (2)将用于纠错的模块用于容错。当自测逻辑发现某个颗粒出现故障且所有的冗余行都已经启用,可以适当将纠错的模块用于容错。这时需要在地址方面和数据重组方面都进行一定的改动,主要包括:①在故障颗粒所在的行内,故障颗粒的地址和数据都被转发到空闲颗粒。②所有的数据线依然直接与控制器模块相连,但在模块内部,数据重组逻辑自动将冗余颗粒的数据通路重组到故障颗粒的数据通路上来。③纠错码编解码逻辑自动调整编解码方案。根据相关寄存器的值,纠错码的编解码逻辑自动降低纠错能力,数据重组逻辑也自动定向纠错码的数据通路。图4为数据重组示意图。  系统纠错容错能力分析 假设各个DDR颗粒之间发生错误的概率是互相独立的,设每个颗粒发生错误的概率恒定为λ,则每个DDR颗粒的可靠性符合泊松分布,其可靠性为Rm=e-λt。在Mem(i,j)系统中,每行的可靠性为  整个系统的可靠性为  重构前后系统可靠性的变化如图5所示。  由此,可以根据故障概率λ计算出系统的整体可靠性Rsystem,根据系统要求的可靠性可以反向计算出所需要的i,j,从而构建出完整的Mem(i,j)容错存储系统。 结论 针对SoC实时数字信号处理系统的特点,设计了一种新的具有自适应容错纠错能力的二级冗余存储体系结构。详细论述了系统在存储颗粒组织排列和信号连接方面对于纠错容错能力的支持、系统在逻辑设计上对纠错容错能力的支持等。新的存储系统容错方案可以有效地提高存储系统的可靠性,下一步的工作将集中在整个系统的低功耗优化方面。 |

网友评论