一种SoC芯片在Magma Talus下的物理实现

发布时间:2010-11-10 13:34

发布者:eetech

|

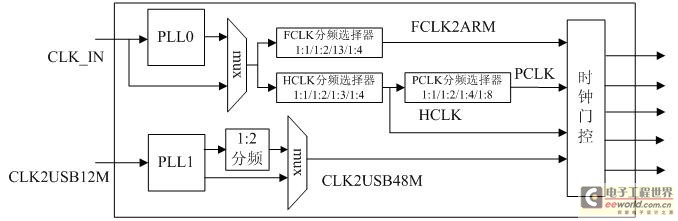

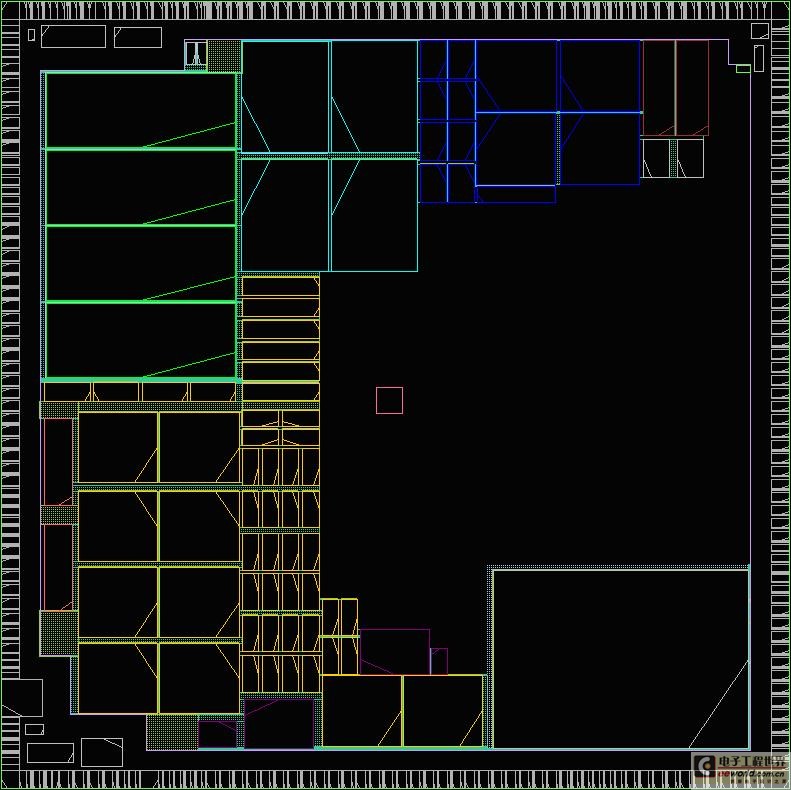

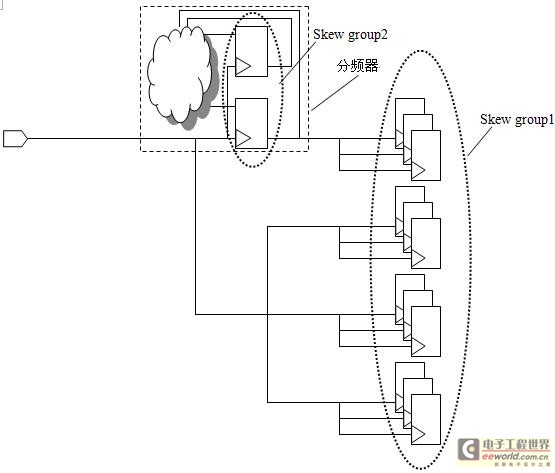

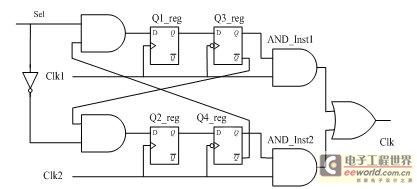

本文介绍了一种SoC芯片架构,及其在0.18um CMOS工艺上以talus为主导EDA工具的物理实现。该芯片包含41个时钟域,4种低功耗工作模式,2个相互隔离的1.8v内部电源域,约有65万个标准单元,94个宏模块,250个pad,合计约900万个逻辑等效门,3600万个晶体管,芯片面积10.5mmx10.5mm。 关键字索引: 约束设计、布局规划、时钟树设计 第一章 芯片结构及物理实现流程介绍 该芯片主要由32位处理器、静态随机存储器、以太网MAC接口、SPI接口、USB1.1 Device接口、USART同异步通信接口、SCI智能卡接口、片外存储器控制器等模块组成。该芯片具备高处理能力、低功耗等特点。其结构框图如图1所示:  图1 SoC芯片的结构框图 我们采用以Magma工具为主,Mentor、Cadence、Synopsys工具为辅的工具套件来完成RTL2GDSII的整个后端流程,如图2所示:  图2 SoC后端实现流程 逻辑实现阶段:用Magma Blast Rtl 来进行逻辑综合,综合完成后利用Mentor DFT进行扫描链的插入。 某算法模块在进行物理综合时,无论采取何种措施(包括优化宏模块位置,添加blockage,加大库单元的outline尺寸等),std cell 部分的Congestion都很严重,如图3所示。而采用Magma Blast Rtl进行逻辑综合,再采用Magma Talus Vortex来进行物理综合时,std cell部分的congestion可以消除。  图3 某算法模块congestion图 物理实现阶段:用Magma Talus Vortex来进行布局规划和电源网络规划、物理综合、时钟树插入及布线工作。 在整个实现过程中,我们采用Magma工具内嵌的静态时序分析引擎和RC参数提取引擎来进行MMMC(Multi-Mode Multi-Corner,多模式多功能角)时序分析,参数提取,信号完整性的分析、避免和修复工作;使用Quartz Rail工具来进行功耗分析,以及包括电子迁移和电压降在内的电源完整性分析。 第二章 时序约束设计 本SoC芯片时序约束设计的关键在于功耗管理控制模块的时序约束。 2.1 功耗管理控制(Power Management Controller, PMC)模块简介 整个设计中首先考虑的是PMC模块的约束。PMC模块是系统用来控制系统功耗的的控制器,可以通过寄存器配置,使SoC芯片在不同工作模式之间进行切换:Slow、Normal、Idle 和Sleep。这些工作模式可以让用户根据芯片不同的应用,通过动态地管理芯片内部各子模块的时钟源供给和系统的工作频率来控制芯片的整体功耗。另外,PMC 还包含了各个子模块的初粒度的时钟门控电路,通过寄存器配置可以集中控制、关闭不必要打开的模块,从而达到降低功耗的目的。模块具有以下性能指标: ?内置锁相环、可动态变频; ? 支持Slow、Normal、Idle、Sleep等4种工作模式; ? 支持模块工作时钟集中控制策略,芯片各模块的时钟可以通过PMC来关闭和打开; ? 低功耗sleep模式下支持DRAM/SDRAM 的数据自刷新,使得DRAM 中的数据可以得到保持; ? 内部具有完整的reset 解决方案,提供3 种reset 选择:hard reset、soft reset、watchdog reset; ? 内部具有完整的唤醒功能。 PMC模块包含了异步时钟动态选择电路、同步时钟动态选择电路、时钟分频电路、时钟门控电路、跨时钟域电路,既存在输入时钟,又存在输出时钟,是一个与时钟高度相关、时序违例集中、时序分析较为复杂的电路。PMC模块的时钟生成电路结构示意图如图4所示:  图4 时钟生成图 系统时钟经过可配置参数的系统PLL和动态选择逻辑后分频(有1:1、1:2、1:3、1:4四种)。选择默认的2分频为CPU 提供时钟,动态选择默认的3分频为高速总线提供时钟,高速总线时钟通过分频后(有1:1、1:2、1:4、1:8四种),动态选择默认的2分频为低速总线提供时钟。 2.2 时序约束的一些策略 一个完整的时序约束文件包含时钟的创建、时钟的约束、输入输出端口的约束及时序违例等。SDC格式的约束可以采用丰富的语法表达出上述内容。而Magma后端工具可以比较容易地识别出该格式的约束。我们采用SDC v1.7格式编写时序约束,这样既能为后端实现工具blast、talus识别,又能被静态时序分析工具PrimeTime识别。 首先根据设计规格要求确定时钟周期,在整个后端设计过程中的不同阶段加以调整和修改。为保守计,我们采取冗余设计,最终设定的周期值比规格要求的值严格。Clock latency和clock skew的设置也要根据实际的时钟树结构不断地进行调整和修改。最终合理的时序约束文件是经过反复地实验不断地修正而得到的。 复杂的时钟,复杂的功能模式,必然带来复杂的时序约束。对其正确、完备的约束施加,是保证后端设计时序分析和优化有效的关键所在。 而PMC模块的主要电路,如时钟门控电路、分频电路,动态选择电路等,采用例化的标准单元以网表的形式直接给出,在用Magma Blast Rtl进行逻辑综合前,将这些以网表形式存在的单元使用force keep命令,保证时序约束施加点的固定。 在Fix Time前设置时序约束时,采用的方法是3分频PLL后的源时钟作为高速总线上的时钟,低速总线时钟与高速总线时钟频率一致,这样在逻辑综合阶段时因为还没有真正的时钟树,而设置的约束又比较保守,使综合结果的时序有较大的冗余,又加快了综合的速度。 在时钟树优化时,采用MMMC来进行。我们仅以功耗模式中Normal模式里的两种在应用时较常用的时钟使用模式来设置MMMC:一种是3分频PLL后的源时钟作为高速总线上的时钟,低速总线时钟是高速总线时钟的2分频;另外一种模式是使用 1分频PLL后的源时钟作为高速总线时钟,低速总线时钟与高速总线时钟频率及PLL后的源时钟频率一致,此时低速总线时钟频率高于前一种模式下的时钟频率,达到低速总线上模块能达到的最高频率。其他模式仅用来分析及优化。这样可以有效加速时钟树创建的时间及分析效率。 在约束设计过程中,不可避免的会涉及到各种模式下时钟间异步关系的设置,我们采用SDC v1.7里面的set_clock_group命令来进行,该命令能有效的表征各个时钟之间的异步关系,避免了set_false_path繁琐的设置,并且能够被Magma Talus软件转换为force timing clockgroups命令。下面是该设计中的两个clock group设置的例子: set_clock_group -name func_async_ck1 -logically_exclusive \ -group [get_clocks "fck2_n"] \ -group [get_clocks "hck3_n hck2anu3_n"] \ -group [get_clocks "hck2anu4_n"] set_clock_group -name func_async_ck2 -asynchronous \ -group [get_clocks "usb_dev_ck"] \ -group [get_clocks "usb_pll_ck" 另外分频时钟与源时钟关系的设置上,我们根据仿真波形来确定分频时钟与源时钟之间的相位关系,从而为create_generated_clock命令在-divide_by,-edges,-invert,-combinational间选择不同的选项,使分频时钟和源时钟之间的source latency关系很容易就能确定下来,简化了时序分析。 下面是该设计中几个分频时钟约束的例子: create_generated_clock -name usb_dev_ck \ -divide_by 4 -invert \ -source [get_pins "…/OR2CLK_Inst/Z"] \ -master_clock [get_clocks "pllout48m"] -add \ [get_pins "…/clk_1x_reg/Q"] create_generated_clock -name rngck8\ -edges "7 15 23" \ -source [get_pins "…/OR4CLK_Inst/Z"] \ -master_clock [get_clocks "pck_n"] -add \ [get_pins "…/CLK_CNT_reg/Q"] create_generated_clock -name pck8_n \ -edges "3 11 19" \ -source [get_pins "…/OR4CLK_Inst/Z"] \ -master_clock [get_clocks "hck3_n"] -add \ [get_pins "…/PCLK_DIV8_reg/Q"] create_generated_clock -name hck_out \ -combinational \ -source [get_pins "…/OR2CLK_Inst/Z"] \ -master_clock [get_clocks "hck3_n"] -add \ [get_ports "hclk"] 2.3非时序逻辑时序弧(data-to-data timing arc)的处理 SoC中使用到的EE模块是一个异步IP,时序模型存在非时序逻辑的时序弧(non-sequential library arc,也即data-to-data timing arc):输入的数据或控制信号与输入pin——CEN、WEN之间有data-to-data 的时序弧存在、其中的控制信号CHER、CHWR、ER_ONLY、WR_ONLY与输出pin——READY之间也存在着data-to-data 的时序弧。综合工具并不区分时序逻辑与非时序逻辑的时序弧,只要设计中有时序弧的单元存在,综合工具就认为应该在相应pin脚设置时钟,因此在综合的过程中会认为在CEN、WEN、READY这几个信号pin应设置时钟。如果不设置,在综合过程中,综合工具的时序分析引擎是报不出任何经过或到CEN、WEN、READY的路径。而一旦设置为时钟,就会产生很多false path。我们最后的做法是不在逻辑综合阶段将其设为时钟,而是将该问题留到时钟树优化时,使用config timing check data_to_data on 将data-to-data check选项打开,并使用force timing check命令约束相应的时序关系。 第三章 布局规划 该设计采用flatten的方式进行布局规划,使用2P/6M EE工艺,包含Hard Macros 94个,共占面积50.3mm2。其中有13种81个由memory compiler生成的memory、7个定制模拟/数模混合模块、2个PLL以及其它IP模块。为两个同为1.8v相互隔离的电压域创建两个floorplan,并使用polygon相关的命令为primary flloorplan创建多边形形状。另外,以data create cluster region命令将PMC模块中除PLL部分外的其他逻辑以region的形式固定到布局的中央位置。 在IO布局上,除了由memory compiler生成的memory IP不需单独供电,其余宏模块均需单独供电,其中为RTC供电定制的电源切换模块所需的电源PAD的隔离还更加复杂。 由于需要单独供电的模拟/数模混合模块较多,电源域较多,在布局规划阶段就确定了各模拟/数模混合模块在芯片中的大致位置及其供电pad在pad环上的顺序。 7个定制的模拟/数模混合模块及2个PLL均位于pad环和电源环之间;位于内部的存储器模块和CPU core由于数量众多,其位置的摆放首先考虑的是固定几个尺寸较大的IP模块的位置,并使用force plan clearance添加blockage;然后使用Magma Talus Vortex中的run place cluster命令来自动摆放余下较小存储器,确定初步的布局规划,而后微调各存储器的相对位置,做到规则规整,控制各个存储器模块之间的布线通道的布局利用率,在较窄的地方不允许任何标准单元摆放,在一些较宽的布线通道我们设置了50%-100%不等的blockage利用率。最后的布局规划如图5所示:  图5 布局规划 第四章 时钟树设计 时钟树设计的内容包括时钟树约束的设置、MMMC、OCV(On Chip Variation)及 CPPR (Clock Path Pessimism Removal,或称 Clock Reconvergence Pessimism Removal)的考虑等。 本芯片时钟树设计的难点在于基于latch的时钟门控单元、时钟分频电路以及动态选择电路带来的时钟树平衡问题而导致的时钟树约束的复杂性。 4.1 分离时钟门控单元的时钟树约束 由于PMC模块中存在大量的由latch和and标准单元构成的非集成的时钟门控单元, latch的D端具有endpoint属性,如果不做特殊处理,在时钟树生成时会与其它具有endpoint属性的触发器、锁存器一起进行平衡。这不是我们想要的结果,我们想要的平衡是把latch和and一起构成的时钟门控单元看成一个组合门电路,仅需要其后的触发器和其它没有受时钟门控控制的触发器一起进行平衡,而将latch排除在外。如图6所示:  图6 分离门控时钟电路的skew group 为了达到上述目的,我们将分离分控时钟的latch和and置于一个skew group之内,并将and门的时钟输入端设置为skew anchor。以下面的SoC芯片中的一个分离门控时钟电路为例,约束如下: force plan clock $m -pin ".../PmcHCLKGate_Inst/i_latch/GN \ .../PmcHCLKGate_Inst/i_and/A" -skew_group 49 force plan clock $m -pin .../PmcHCLKGate_Inst/i_and/A -skew_anchor 4.2 分频电路时钟树约束 SoC芯片的PMC模块中分频时钟之间,以及分频时钟和源时钟之间,存在非例外的时钟路径,因此,我们将分频电路时钟域和未分频电路时钟域内的触发器置于一个skew group之内。分频电路本身由于是孤立的逻辑,与其它功能逻辑电路的触发器之间在逻辑上不存在有效数据路径,因此可以单独做成一个skew group。但由于它处于分频时钟域路径上,为使置于同一skew group之内的分频时钟域和源时钟域内的触发器之间的skew在规定的范围内,必须控制分频电路的时钟路径,如图7所示:  图7 分频电路的skew group 我们以某三分频电路为例,下面的命令是对其时钟树创建时的相关约束: force plan clock $m -pin "…/PmcFHClkDiv3/QQ_reg[0]/CK \ …/PmcFHClkDiv3/QQ_reg/CK" -skew_group 54 force plan clock $m -pin "…/PmcFHClkDiv3/QQ_reg/CK" -skew_anchor force plan clock $m -pin "…/PmcFHClkDiv3/DQ_reg/CKN \ …/PmcFHClkDiv3/OR2CLK_Inst/A" -skew_group 55 force plan clock $m -pin …/PmcFHClkDiv3/OR2CLK_Inst/A -skew_anchor 4.3 动态时钟选择电路的时钟树约束 另外,PMC模块中使用动态时钟选择电路用来消除异步时钟间及同步时钟间动态切换过程中的毛刺,其中动态异步时钟选择电路结构如图8所示:  图8 动态异步时钟选择电路结构图 同样,我们针对该电路也做了如下约束: force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst1/B \ …/PmcSysClkSel_Inst/Q1_reg/CK \ …/PmcSysClkSel_Inst/Q3_reg/CK" -skew_group 1 force plan clock $m -pin "…/PmcSysClkSel_Inst/AND_Inst2/B \ …/PmcSysClkSel_Inst/Q2_reg/CK \ …/PmcSysClkSel_Inst/Q4_reg/CK" -skew_group 2 第五章 总结 在本文中,我们介绍了一种SoC芯片架构,探讨了在0.18um CMOS工艺上以Magma Talus为主导EDA工具的物理实现中的3个难点问题:时序约束设计、布局规划以及时钟树约束设计。鉴于篇幅限制,其它在本SoC物理实现过程中涉及到的诸如信号完整性问题分析与避免、电源完整性分析与避免、与signoff工具间参数相关性的设置、ECO、模拟及数模混合模块建模及其在Magma Talus数字流程中的运用等方面在本文中未能涉及。 该SoC芯片包含41个时钟域,4种低功耗工作模式,2个相互隔离的1.8v内部电源域,约有65万个标准单元,94个宏模块,250个pad,合计约900万个逻辑等效门,3600万个晶体管,芯片面积10.5mmx10.5mm。 该芯片既有多个复杂的数字算法电路,也有多个定制的模拟/数模混合模块,宏模块众多,布局规划和电源规划较为复杂;在前仿真验证过程中方面,功能bug,性能不达标等问题,使RTL迟迟不能冻结,给后端留下的时间不多。我们借助Magma公司Talus软件在后端实现方面的强大能力,集中时间攻关,解决了复杂时序约束、大规模宏模块情况下布线拥塞的技术、多电压域下的电源规划技术以及复杂时钟树设计等难题,节省了大量的后端运行时间和手工工作,同时也实现了较好的时序、面积结果。 目前该芯片已成功流片,实测的性能及功耗指标均达到预期效果,高速总线时钟频率可达110M,normal功耗模式下算法模块全速工作时功耗小于380mW,sleep功耗模式下功耗11mW左右。 感谢Magma公司在物理实现方面持续的努力和进步,使得用户能够在设计中体会到革新所带来的便捷与快乐。在此,希望Magma今后能够不断革新,给用户带来更多的方便,分享更多的成功。 |

网友评论