基于FPGA的DDFS与DDWS两种实现方式

发布时间:2010-11-9 20:18

发布者:techshare

|

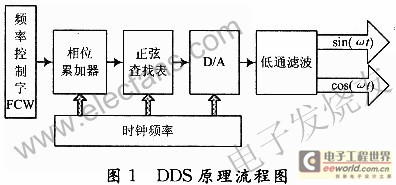

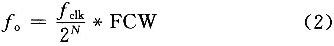

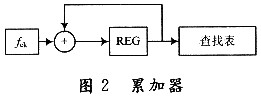

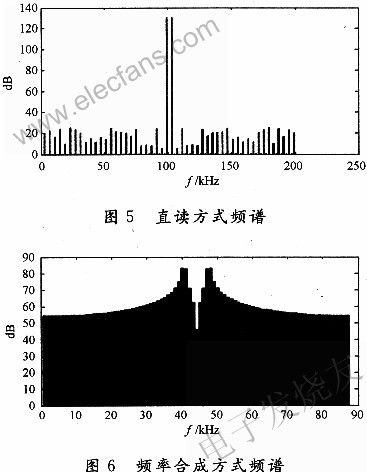

DDS(Direct Digital Freqiaency Synthesizers)广泛应用于雷达系统、数字通信、电子对抗、电子测量等民用军用设备中。它是随着半导体技术和数字技术的快速发展而发展起来的新型的频率合成技术,与传统的VCO+PLL的模拟方式产生所需频率相比,DDS技术具有频率分辨率高,相位噪声低,带宽较宽,频谱纯度好等优点。这些技术指标在一个系统中是至关重要的,决定着一个系统的成败。 1 DDS的基本原理 1.1 频率合成方式的基本原理 DDFS是根据余弦函数相位和幅值的对应关系,从相位出发,由不同的相位给出不同的电压幅值,再经过D/A变换和滤波最后得到一定频率和调频率的模拟信号。由此可见,DDS有很多功能模块组成,如图1所示。  若相位累加器有N位,时钟频率为fclk,频率控制字为FCW。N位的相位累加器可以对时钟频率进行2N分频,所以DDS的精度可以达到:  频率控制字是用来控制累加器的步进的,累加器的步进为  。假设初始的相位偏移△φ=0,则经过N个时钟周期后相位累加器的输出θ=2π*FCW*N*(1/2N)。在相位步进△0时,完成2π的相位变化即为完成一个输出周期,所以20/△θ*Tclk=T0,即:  可见调节FCW可以任意地按照要求改变输出频率,这就达到了频率合成的目的。 1.2 直读方式DDS的原理 直读法(DDWS)工作流程是,把所需要的DDS的波形,直接用Matlab抽样量化,然后把量化的数据直接存储到FPGA的BlockRAM中,再在时钟频率的控制下直接从BlockRAM中读取数据,D/A后输出原来波形。 2 数字实现 2.1 DDFS的数字实现 由于D/A之前都是数字部分,为了分析其原理数字控制的实现过程,参考如图2所示结构。  相位累加器是由一个加法器和一个寄存器构成,假设累加器位数N=6,那么000000代表0弧度,000001代表弧度,相应的000010代表(2π/64)*2弧度,111111代表(2π/64)*63弧度。若频率控制字FCW=000011,并且累加器中的初始相位为O,则经过N=21个时钟周期后形成的二进制序列为000000,000011,…,111111,对应的相位分别为O,(2π/64)*3,…,(2π/64)*63。当第22个时钟周期到来时,加法器溢出,所有位数重置为0,另一个循环周期开始。查找表可以用FPGA中BlockRAM做成,前面的二进制序列作为地址,相位对应的幅度值作为地址对应的值存储起来,这样在时钟频率的控制下通过二进制序列可从BlockRAM中读取相应的幅值,经过D/A后就为所需要的模拟波形。图3为FPGA综合后的RTL级电路图。  2.2 DDWS的数字买现 DDWS的数字实现较为简单,把通过Matlab抽样量化后的数据直接保存为.BAT数据格式,然后在FPGA中用IP核的BlockRAM生成一个ROM,把数据存储进去,这样就可以根据时钟要求输出需要的数据了。 图4为FPGA仿真后的RTL级电路图。  3 DDS的性能指标 3.1 频率分辨率 对于频率合成方式的DDS,只要是累加器的位数足够多,理论上可以达到任意无限高的频率分辨率。由式(1),若N=39,fclk=1,分辨率可达到0.000 18 Hz。但是对于直读方式,分辨率是受到硬件D/A速度限制的,一般如果用四倍的频率速度采集和恢复,分辨率只能达到O.25 Hz。 3.2 SFDR 最常用的评价DDS工作性能的参数是带外抑制比(SFdR),它是指有效信号的频谱幅度与噪声频谱幅度的最大值之差。实际的频谱合成方式的DDS在累加器的输出和查找表之间还有个相位折断的过程。若累加器的输出A为N位,查找表的输入B为M位,一般情况下N>M,这是为了节约查找表的空间。正是由于这种相位折断才降低了SFDR,使得DDS的性能变坏。以上参数都是可以根据实际的要求估算出来的,例如要产生一个4 MHz、分辨率为O.4 Hz、带外抑制比为60 dB的正弦信号,时钟频率为100 MHz。那么根据式(2),可以得到N=11;根据实际经验,查找表的每位可以产生6 dB的抑制比,所M=60/6=10 b。由于直接读取法DDS不存在相位折断的问题,所以往往能得到比较好的SFDR。 3.3 信噪比 由于SFDR只与最大噪声的频谱幅度有关,所以相同的SFDR可能有不同的频谱纯度,为此引入了另外一个DDS的性能指标——信噪比(SNR )。信噪比是指信号功率和噪声功率之比,由于涉及到所有的噪声,所以跟频谱纯度息息相关,对于频率分辨率高的DDS,噪声的能量较低,信噪比较大,频谱纯度好。 4 Matlab仿真结果 根据两种DDS的FPGA的仿真数据,可以通过Matlab仿真输出波形,如图5,图6所示。  可以根据图很明显地看出以上三个性能参数的比较情况,直读DDS的SFDR要大得多,而且频谱纯度也好,合成方式的频率分辨率高。 5 结语 从以上比较可以发现直读方式是实际应用中非常好的选择,但是对于这种方式,只能输出有限的预先设定好的频率和调频率,不具有通用性适合用在特定的场合。而频率合成的DDS能合成任意频率和调频率,也能通过一定的措施达到所需指标,所以这种原理是一种通用的原理,被科研工作者和DDS制造商广泛采用。在雷达系统(比如高度计、散射计)中,往往只需要某一种或者几种特定的调频率、带宽、频率的DDS,所以可以较多地采用直读方式。 |

网友评论