基于FPGA的绝对式编码器通信接口设计

发布时间:2010-11-9 11:58

发布者:techshare

|

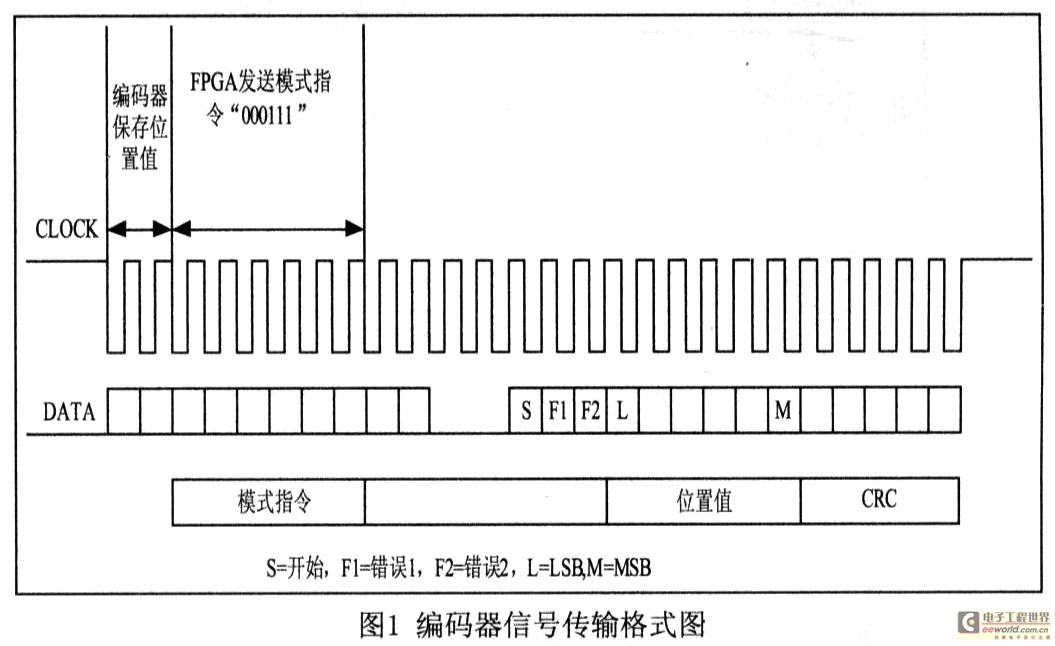

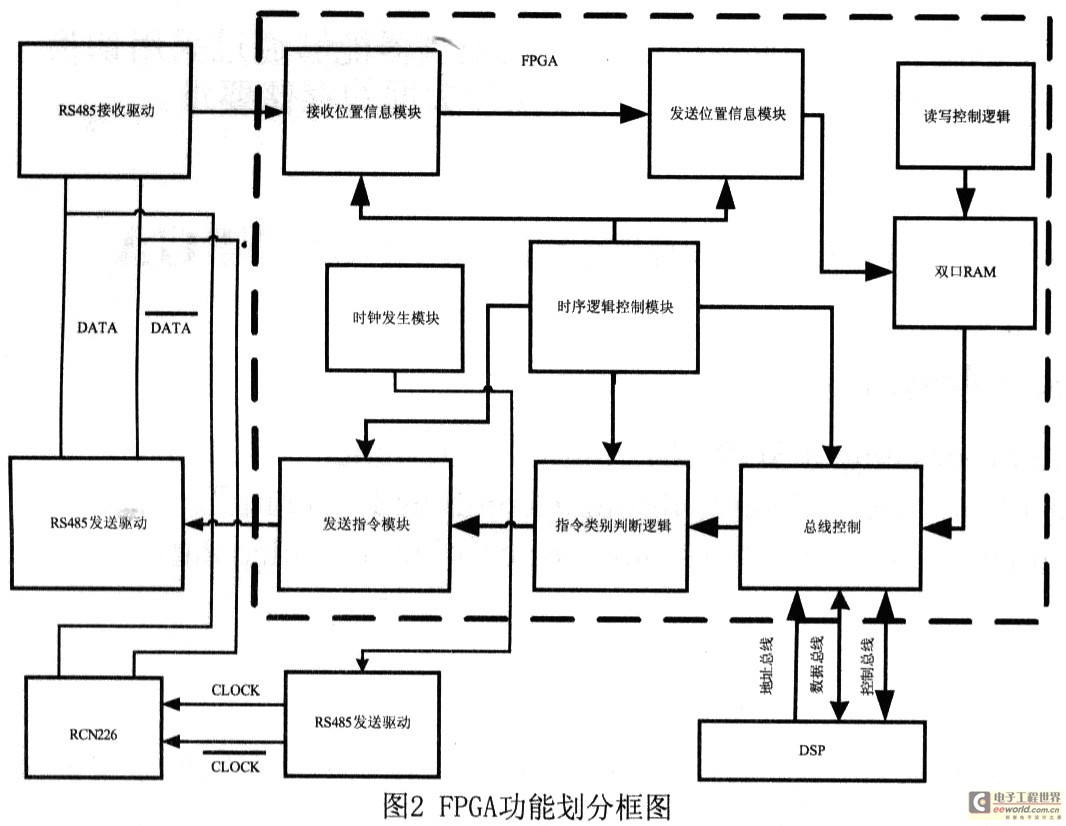

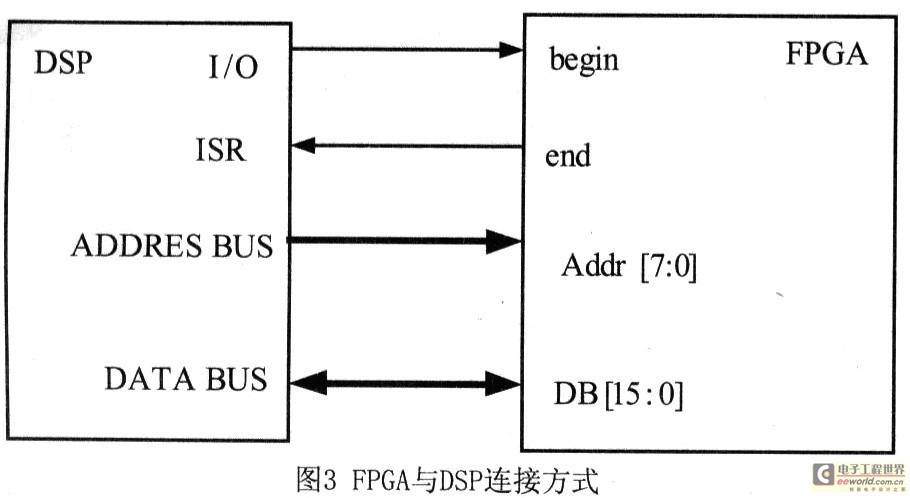

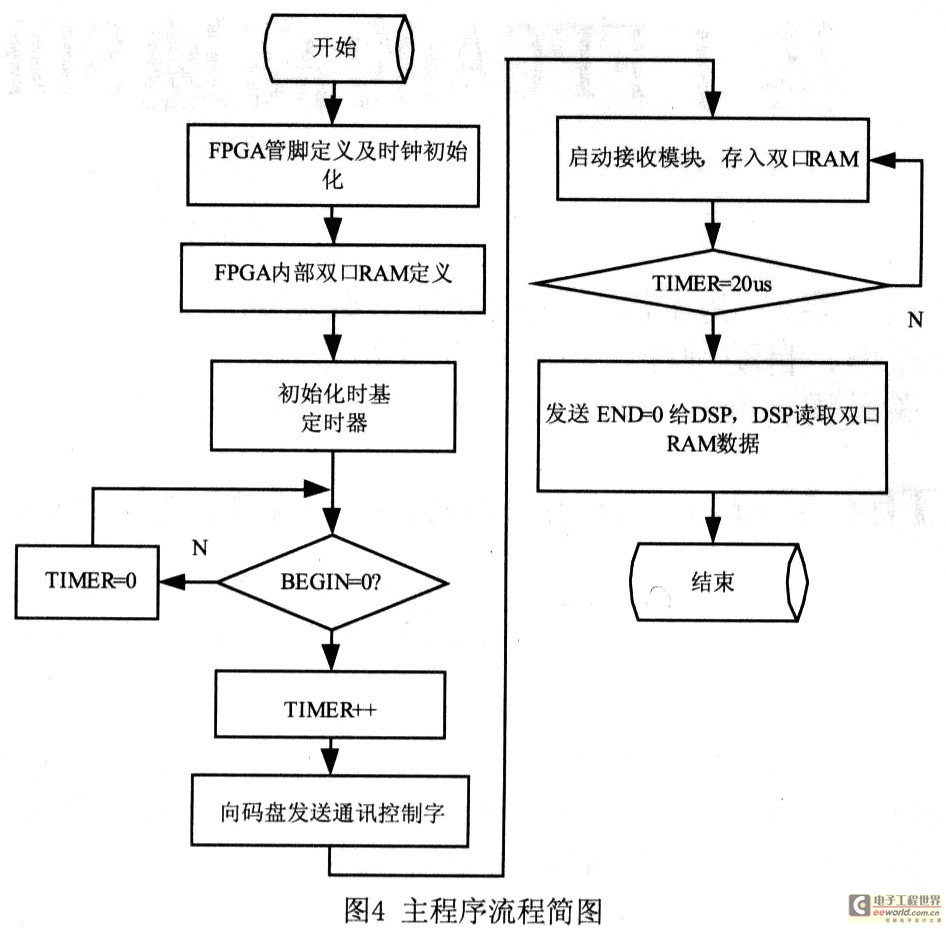

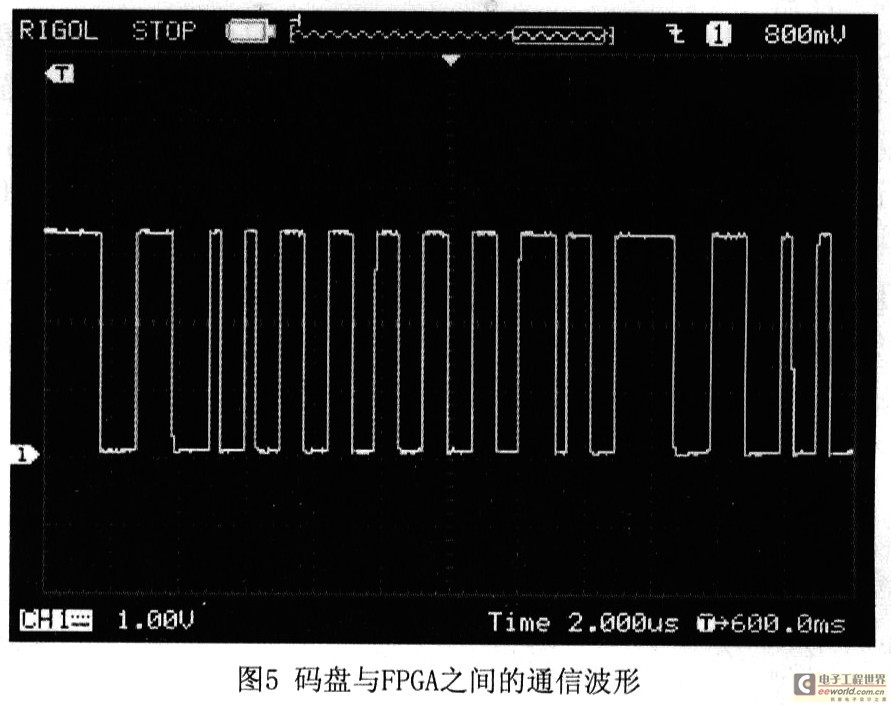

光电码盘是一种基本的位置、速度检测反馈单元,非常广泛地应用于变频器、直流伺服、交流伺服等系统的闭环控制中。为了减小体积,绝对式编码器一般采用串行通信方式输出绝对编码,针对伺服电机控制等高端场合,为了满足快速的电流环、速度环、位置环的控制需要,编码输出的速度又应该非常快,这些不利因素都对绝对式编码的接收增加了难度。 绝对式编码器厂家大多为其编码器配套了接收芯片,实现串行编码到并行编码的转换,便于控制器的读取操作。但是此类芯片通常价格比较昂贵,大约占绝对式编码器价格的四分之一。目前国内外高端交流伺服系统中普遍采用FPGA+DSP结构。DSP用来实现矢量变换和其它算法流程;FPGA用以实现译码、A、B、 Z信号输出、I/O扩展等功能,FPGA中尚有很多资源没有得到充分利用。本文研制了一种用于交流伺服系统中的基于FPGA的绝对式编码器智能接口,实现与绝对式编码器的双工通信,接收高速数据流,同时在FPGA内部开辟RAM空间,将收到的编码器数据存入RAM中,DSP可以以访问内存的方式读取数据,提高了工作速度。同时,该接口还具有奇偶校验等纠错功能,完全可以替代厂家提供的接收芯片,大幅度降低了产品成本。 1 RCN226型绝对式编码器 国内外绝对式编码器生产厂商很多,如日本的多摩川精机、德国的海德汉、国产的长春三峰等。其中海德汉的RCN226型绝对式编码器采用的是海德汉公司专用的EnDat2.2一位置编码器双向数字接口,它传输的数据类型分为位置值、位置值及附加信息或参数。发送的信息类型由模式指令选择。模式指令决定被发送信息的内容。每个模式指令包括三个位。为确保可靠发送信息,每个位均采用冗余发送(反相或两次)。其发送位置值的模式指令为"000111"。信号传输格式如图1所示。  数据包发送与数据传输同步。传输周期从第一个时钟下降沿开始。编码器保存测量值并计算位置值。两个时钟周期后,后续电子设备发送模式指令。编码器发送位置值后,从起始位开始由编码器向后续电子设备传输数据。后续"错误位"-"错误1"和"错误2"是检测类信号,用于监测故障。这两个信号相互独立地生成,它表示编码器发生可导致不正确位置值的故障。发生故障的确切原因保存在"工作状态"存储器中,并可被详细地查询。然后编码器从最低有效位(LSB)开始发送绝对位置值。其长度取决于所用的编码器,RCN226的绝对位置值为26位。位置值的数据发送以循环冗余校验(CRC)结束。在数据字结尾处,必须将时钟信号置为高电平。10至30 μ s后或1.25至3.75 μ s后(系统时钟大于1MHz时)数据线返回低电平。然后,时钟信号启动另一次数据发送。 2 绝对式编码器接口的实现 全数字化交流伺服系统中采用TMS320X2812作为控制器,用以实现位置环、速度环和电流环以及SVPWM、电压和电流采样等功能。此外,采用Altera公司的型号为FP1C6的"Cyclone系列FPGA,用以实现与绝对式码盘接口、译码逻辑等功能。同时,在FPGA内部实现了256字节的双口RAM,用来与DSP之间通过总线实现数据传输。FPGA部分的功能框图如图2P所示。  码盘接口部分分为发送模块、接收模块、双口RAM模块、主程序模块四部分。由于每次通信时间是严格固定的,设系统时钟为2MHz。FPGA为主叫,向编码器发送"请求数据"控制字共6位,需时3 μs,编码器向FPGA共发送1个起始位、两个"错误位"、26位位置值和5位CRC校验位,共34位的数据共需时17 μs,所以每次通信需要20 μs的时间,并且每个时刻具体需要传递哪一位数据也是严格确定的。因此采用基于时基的设计方法。 FPGA内部设计了一个时基为20ns的计数器,每20ns加1,作为整个电路的时基,根据这个时基来确定每一时刻收到的数据具体属于哪个位。在FPGA 内部实现了256bytes的双口RAM空问,A口具有8位数据线,8位地址线,用于与编码器通信,B口具有16位数据线,8位地址线,用于与DSP通信,因为TMS320X2812为16位DSP,所以与FPGA中RAM的数据传递极为方便。 DSP在每个电流环周期发送一个有效的"begin"信号,20μs之后,码盘信号接收模块将接收到的数据存入FPGA内部双口RAM的A口中,并按顺序排列成16位数据的形式,然后向DSP发送end信号,表示一次通信结束,DSP接收到中断之后从FPGA的双口RAM的B口中读取数据,完成一次通信, DSP的连接如图3所示。  在本接口的研发过程中,对FPGA的开发采用Altera公司的Quartus II 5.1集成环境,硬件描述语言为VHDL语言。图4为主程序流程图。  图5为码盘与FPGA之间的通信波形,从位置信号可以看出该接口工作正常。  3 结束语 本文设计了一种基于FPGA的绝对式码盘智能接口,用以进行绝对式编码器和伺服驱动器DSP处理器之间的通信。并且具CRC校验等纠错功能。该接口基本可以替代价格昂贵的专用接口芯片,降低产品的成本,促进伺服电机驱动器的国产化进程。 |

网友评论