FPGA与PCB板焊接连接的实时失效检测

发布时间:2010-11-8 11:29

发布者:eetech

|

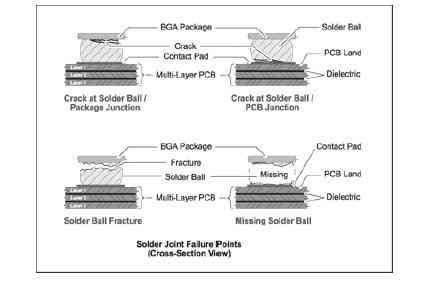

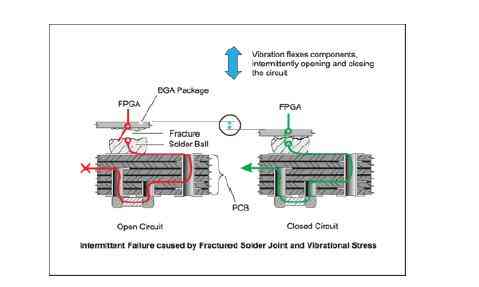

问题描述: 81%的电子系统中在使用FPGA,包括很多商用产品和国防产品,并且多数FPGA使用的是BGA封装形式。BGA封装形式的特点是焊接球小和焊接球的直径小。当FGPA被焊在PCB板上时,容易造成焊接连接失效。焊接连接失效可以“致命“一词来形容。当焊接球将封装有FPGA的器件连接到PCB上时,如果没有早期检测,由焊接失效引起的电性异常可能会导致关键设备的灾难性故障。为了防止关键设备由于焊接问题引起的灾难性故障,美国锐拓集团公司(Ridgetop-Group)开发了SJ-BIST解决方案。作为一系列的故障预测产品中的一员,SJ-BIST对工作中的FPGA的焊接失效提供了实时检测手段。 焊接点故障失效经常发生在FGPA,在所有类型的商业和国防产品中.当FPGA被封装在BGA封装件中后,FPGA很容易受焊接连接失效的影响。焊接失效的原因不能被孤立出来,早期检测发现是非常困难的,间歇性的故障会随着时间的升级直到设备提供不可靠的性能或无法操作。不过,正如经常发生的情况,这个问题也是可以解决的,它就是Ridgetop-GroupSJ-BIST. 有哪些因素可造成焊接连接失效呢? 常见失效原因: 1)应力相关的失效 -- 针对工作中的器件 对工作中的器件,造成焊接连接失效的主要因素是热-机械应力和震动应力。无论是震动,扭矩转力,热循环,材料膨胀,或环境中的其他应力,其不可避免的结果是由累积损伤造成的机械故障。在焊接连接中,损伤表现为器件与PCB连接处的裂缝。 现行的预测焊接连接失效的方法是统计退化模型。但是,由于统计在大量样品存在时才具有实际意义,基于统计的模型充其量也只能是一种权宜的解决办法。锐拓集团公司的SJ-BIST可以提供一个直接的,实时的衡量和预测焊接连接失效的手段。 2)与制造生产相关的故障 因为焊接点失效也发生在生产制造过程中.Ridegtop-GroupSJ-BIST可以监测到未安装好 的FPGA。这些与制造业相关的故障有它自己的一套检测的挑战。目视检查是目前所采用的确定在制造环境中的失效的方法。主要的缺点是无法进行测试和检查焊点。 目视检查仅限于FPGA的最外排的焊接点,而电路板尺寸和其他表面安装元件限制了更进一步的视野。随着BGA封装阵列密度的增加,焊接球的偏差变得更严格。在细间距的BGA封装中,有数以千计1.0毫米间距和0.60毫米球直径的焊接球。在这些条件下,焊盘的谐调和焊接的不充分成为焊盘的断开和部分断开的故障的主要成因。当焊接不浸湿焊盘时,即使百分之百的x射线的检查是不能保证找到焊点断裂.涉及焊球并粘贴毛细渗透到镀通孔的另一种缺陷是不容易识别,甚至还与X线成像。 作为一个内嵌式软核,Ridgetop-GroupSJ-BIST是在生产制造环境中真正适合PCB-FPGA监测。 BGA封装连接失效(用于热循环)的定义: 业界关于BGA封装连接失效的定义是: 1.大于300欧姆的峰值电阻持续200纳秒或更长时间。 2.第一个失效事件发生后在10%的时间内发生10个或更多个失效事件。 焊接失效的类型: 1)焊接球裂缝  随着时间的推移,焊接部位会因为累积应力的损伤而产生裂缝。裂缝常见于器件与PCB焊接的边缘。裂缝会造成焊接球与BGA封装器件或PCB板的部分分开。一种典型的裂缝位置在BGA封装和焊接球之间,另一种典型的裂缝在PCB和焊接球之间.对已有裂缝的焊接球的继续损伤就会导致另一种类型的失效-焊接球断裂。 2)焊接球断裂 一旦有了裂缝,后继的应力会导致焊接球断裂。断裂造成焊接球和PCB完全分开,从而导致较长时间的开路状态,断裂面的污染和被氧化。最终造成从退化的连接到短时间间歇性的开路一直到较长时间开路。  3)缺少焊接球 导致裂缝,最终形成断裂的后续机械应力还有可能导致断裂的焊接球的错位。缺失的焊接球不仅使该引脚的连接永久失效,而且错位的焊接球可能会停留在另一个位置而导致另一个电路的不可想像的短路。  焊接球失效的电信号表现 焊接球断裂处定期的开开合合会导致间歇性电信号故障。震动,移动,温度变化,或其他应力可以使断裂的焊接球开开合合,从而导致电信号的间歇性故障。PCB厂使用的易弯曲的材料使这种间歇性信号也成为可能,例如震动应力造成的断裂开开合合,难以预测的开开合合的焊接球电路导致间歇性信号,这种间歇性故障很难被诊断。另外,FPGA周围的I/O缓冲电路使测量焊接网络的电阻值几乎不可能。在工作的FPGA中出现故障的器件可能会在测试床上没有任何故障发现(NTF)就通过测试,因为焊接处暂时连接上了。很多用户发现FPGA工作不正常,用手按一P下,FPGA就工作正常了,也是因为这个原因.  解决方案:SJ-BIST实时检测焊接状态 在美国锐拓集团公司(Ridgetop-Group)的创新发明之前,没有很好的,已知的办法检测工作中的FPGA的应力失效。目前生产制造中使用的目检,光学,X-光和可靠性测试等技术很难奏效,因为反映为电信号失效的故障在器件没有加电源的情况下基本上是看不到的。通过对将要发生的失效的早期检测,SJ-BIST支持基于条件(condition-based)的设备维护并能减少间歇性失效。其卓越的灵敏度和精确度使SJ-BIST可以在两个时钟周期内发现和报告低至100欧姆的高电阻失效而且没有误报警。作为一个可缩放的解决方案,它可以附加在用户的现存的测试中枢,不会额外增加资源。 锐拓集团公司的SJ-BIST是一个可以授权使用的知识产权内核。它的安装不需要工具和设备。它是一个Verilog软内核可以集成在用户的FPGA中,只需在PCB上增加一个小电容以及在现有的测试程序中增加一小段代码。在某些情况下,甚至电容也是不需要的。SJ-BIST会占用现有FPGA的门,250FPGA门就足够了。  SJ-BIST是汽车,工业控制和航空航天市场的理想解决方案并且已经被戴姆勒-克莱斯勒公司和美国雷神导弹系统,NASA,NAVAIR等使用。医疗器械也是一个合适的应用对象,包括起搏器,神经刺激器和其他靠近心,脑,脊髓等可靠性要求高的设备。锐拓集团公司的电子故障预测方案可以在故障出现之前就对器件进行安全更换,提前采取措施,避免重大事故发生。 |

网友评论