基于FPGA的串行Flash扩展实现

发布时间:2010-11-7 20:15

发布者:techshare

|

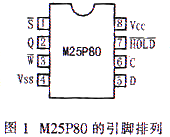

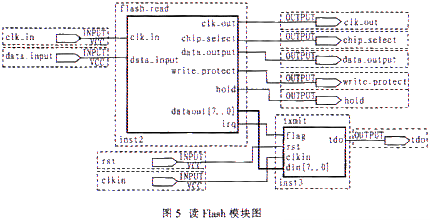

1 引言 FPGA凭借其方便灵活、可重复编程等优点而日益被广泛应用;闪速存储器(Flash Memory)以其集成度高、成本低、使用方便等优点,在众多领域中也获得了广泛应用。在现代数字电路设计中。经常需要保存大量数据,而Flash存储速度快、体积小、功耗低且价格低廉,可在线电擦写,信息在掉电后不会丢失,因此成为设计人员的首选。 2 M25P80的介绍 Flash是一种具有电可擦除的可编程ROM,可以分为两大类:并行Flash和串行Flash。并行Flash存储量大,速度快;而串行Flash存储量相对较小,但体积小,连线简单,可减小电路面积,节约成本,二者各有其优缺点,可依据实际需要选取。本文开发的系统对速度的要求不是很高,而对电路板的面积要求则较为苛刻,因此系统设计选用了串行FlashM25P80。 M25P80是意法半导体推出的一款高速8 Mbit串行Flash,共由16部分组成,每一部分有256页,每页有256个字节。M25P80具有先进的写保护机制,读取数据的最大时钟速率为40 MHz。M25P80的工作电压范围为2.7 V~3.6 V,具有整体擦除和扇区擦除、灵活的页编程指令和写保护功能,数据保存至少20年,每个扇区可承受100 000次擦写循环。并行Flash封装通常需要28个以上的引脚,因此,额外支出大,而M25P80采用SO8封装,需要的引脚数较少,从而节省了电路板空间,功率、系统噪声和整体成本等都会大幅度降低,既经济又实用。 图1为M25P80的引脚排列,其中Vcc和Vss分别为电源和地,其他6个引脚均可直接与FPGA的I/O引脚相连;写保护引脚W和HOLD挂起引脚,用于数据保护和空闲模式的低功耗运行,若不用可将其置为高电平;S为片选信号,为低电平时表示器件被选中,否则工作在待机状态;Q为串行数据输出,数据在时钟的下降沿输出Flash器件;D为串行数据输入,包括传输指令、地址和输人数据,输入信号在时钟的上升沿锁存Flash器件中。C为串行时钟,由FPGA提供时钟。由于时钟信号速率较高,所以在PCB布线时要特别注意减少干扰,最好采用地线屏蔽。  3 M25P80的指令操作 M25P80共有12条操作指令,所有指令都是8位,操作时先将片选信号(S)拉低选中器件,然后输入8位操作指令字节,串行数据在片选信号S拉低后的第一个时钟的上升沿被采样,M25P80启动内部控制逻辑,自行完成相应操作。指令后有时需输入地址字节,必要时还要加入哑读字节,最后操作完毕后再将片选信号拉高。下面简单介绍几条最常用的指令操作。 3.1 写使能指令 页面编程时,在写寄存器或者擦除之前,必须先使用写使能指令设置寄存器的写使能位。在上电或写使能无效指令操作,以及页面编程、写寄存器及擦除指令完成时,该写使能位复位。写使能指令的时序比较简单,指令0000 0110(06h)在片选信号拉低后的第一个时钟的上升沿送入Flash,先输入高位,指令输入完成后立即拉高片选信号,否则Flash的保护机制则认为是干扰信号而不执行该指令。写无效指令与写使能指令类似,只是输入的指令代码为0000 0100(04h)。 3.2 读/写状态寄存器 状态寄存器在任何时候都可读,即使在页面编程、擦除或者写寄存器时也可读取寄存器,可被连续读取状态寄存器。片选信号拉低后立即送人8位的读寄存器指令,接下来Flash将内部寄存器的数值串行输出,8位寄存器内容反复输出。 写状态寄存器的操作步骤:写使能指令输入完成后,拉高片选信号,Flash执行读使能指令设置寄存器。然后拉低片选信号,输入写寄存器指令和数据,随后必须马上拉高片选信号。 3.3 读数据指令 片选信号拉低后,首先输入8位读数据指令,再输入所要读取内容的24位首地址,地址指向的数据在时钟的下降沿输出。数据输出后,地址自动递增,并指向下一个地址。传输下一个地址指向的数据,当地址达到最高位后自动转向首地址000000h,如此循环,读出Flash中的全部内容,直到片选信号拉高。读数据指令时序如图2所示。  3.4 页面编程指令 在页面编程之前,首先要输入写使能指令,Flash完成寄存器设置后片选信号拉低,输入页面编程指令,紧接着输入编程地址和输入数据。一次最多可输入256字节数据,如果超出则只保留最后输入的256字节。如果输入的地址低8位不全为零,则从输入的地址开始编程,编程至该页最后,再从该页的起始位置开始编写。数据输人完毕后片选信号必须置高。否则不执行页面编程指令。页面编程指令时序图如图3所示。  3.5 擦除指令 擦除指令将Flash中的0置为1,分为部分擦除和整体擦除两种指令。整体擦除指令和写使能指令类似。只是输入的指令代码不同,而部分擦除指令只需要在指令代码后输入需要擦除的地址即可,一次可擦除一块。执行这两条指令之前,需要先执行写使能指令。 4 硬件实现 Flash正常工作时必须严格按照Flash的时序控制信号。首次使用Flash时一定要先进行擦除操作,编程指令可以将1变为0。往Flash中写入数据时,先将数据写入FPGA的ROM中,然后在FPGA内部根据Flash的页面编程时序将数据写入Flash中。选用Altera公司的FPGA,所需的ROM模块可以直接调用QuartusII中的宏功能模块,编写一个控制模块控制读取ROM的时间及地址,并将数据按照Flash的时序送入Flash中.页面编程的模块图如图4所示。选用的Flash容量较大,一般FPGA没有这么大的存储空间,所以数据可分多次写入。FPGA的ROM中的数据保存在.mif文件中,.mif由Matlab直接生成.mif文件,也可在QuartusII软件中生成。  Flash中的数据只要按照读时序要求就可以顺利读入FPGA中进行运算。在调试中,为了验证程序的正确性,可将从Flash中读出的数据通过串口送到计算机,模块图如图5所示。图中的txmit为串口的发送端模块图,它负责将接收到的数据按照RS232C的时序格式输出至计算机。flash_read模块按照Flash的读数据格式发出控制信号,并将从Flash读出的数据按照字节打包送到txmit模块。读时序验证无误后,去除txmit模块,将由Flash读出的数据送到其他模块参与运算。  需要注意的是,一些指令在操作完成后,需要留出一段时间Flash进行数据处理,如写寄存器周期(tw)为5 ms~15 ms,页面编程周期(tpp)为1.4 ms~5 ms,部分擦除周期(tse)为1 s~3 s,而整体擦除周期(tBE)为10 s~20 s。这些指令输入结束后拉高片选信号足够长的时间,也可以在执行这些指令操作的同时读取内部寄存器值,以监控上述周期是否结束。一旦检测到指令执行完毕则执行后续操作,这样可节省时间。如果忽略了Flash的处理时间则会发生错误,导致Flash无法正确执行指令。 5 结束语 数字电路设计中经常需要使用大容量存储器,串行Flash体积小、占用系统资源少、连线简单。随着微电子技术的迅猛发展,FPGA在数字电路设计中所发挥的作用越来越大,广泛应用于系统实现及功能验证。利用FPGA直接控制flash接口时序,不仅节约了专用编程器的开支,而且方便灵活、便于移植。使用硬件描述语言编写的接口时序,可重复利用,可移植性强。FPGA的灵活性和串行Flash的体积小的特点相结合,具有设计灵活、成本低廉、实用性强等优势,并具有重要的参考价值。 |

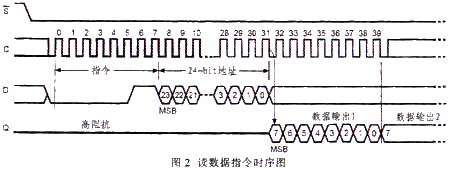

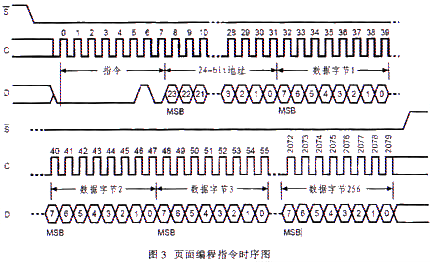

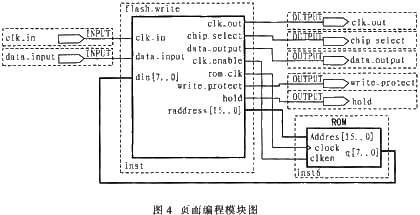

网友评论