вЛжжгУCPLDЪЕЯжЕФЖЬжЁНЛжЏЦїЩшМЦ

ЗЂВМЪБМфЃК2010-11-7 20:02

ЗЂВМепЃКtechshare

|

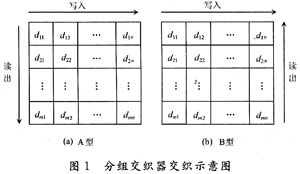

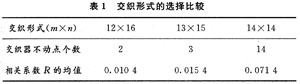

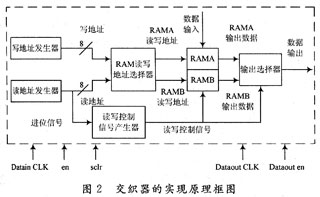

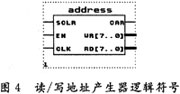

1 в§ бд ЭЈаХММЪѕЕФЗЂеЙЃЌЖдгкЯЕЭГПЩППадЕФвЊЧѓВЛЖЯЬсИпЃЌЬиБ№дквЦЖЏЭЈаХСьгђЃЌЪ§зжаХКХЕФДЋЪфЙ§ГЬГЃЛсАщЫцгаИїРрЕФИЩШХдДЃЌДгЖјЪЙЕУаХКХВњЩњЪЇецЃЌгАЯьЭЈаХжЪСПЁЃОРДэБрТыММЪѕПЩвдОРе§аХЕРжаЕФЫцЛњИЩШХВњЩњЕФЪ§зжаХЯЂађСаЕФЫцЛњДэЮѓЁЃЕЋЪЧЃЌНіРћгУОРДэБрТыММЪѕЃЌЖдгкДЋЪфЙ§ГЬжаЕФЭЛЗЂадИЩШХЃЌашвЊНшжњгкКмГЄЕФТызжЃЌетбљЛсдіМгБрвыТыЦїЕФИДдгадЃЌЭЌЪБвВЛсВњЩњНЯДѓЕФЪБбгЁЃ НЛжЏММЪѕзїЮЊвЛЯюИФЩЦЭЈаХЯЕЭГадФмЕФЗНЪНЃЌНЋЪ§ОнАДеевЛЖЈЕФЙцдђДђТвЃЌАбдЯШОлМЏГЩЦЌЕФЮѓТыЗжЩЂЃЌЪЙЕУЭЛЗЂадДэЮѓзЊЛЏЮЊЫцЛњадДэЮѓЃЌетбљЃЌОРДэКѓЕФЮѓТыИіЪ§дђдкОРДэТыЕФОРДэЗЖЮЇФкЃЌНгЪеЖЫОЭПЩвдгУНЯЖЬЕФТызжНјааОРДэЁЃ 2 НЛжЏЦїЕФадФмЗжЮі 2.1 НЛжЏЦїРраЭЕФбЁдёддђ ГЃгУЕФНЛжЏЦїжївЊга3жжЃКОиеѓЗжзщЪНЁЂЮБЫцЛњЪНКЭАыЮБЫцЛњЪНЁЃ ОиеѓЗжзщЪННЛжЏЦїЃЌгЩгкађСаНЯЖЬЕФЮБЫцЛњЪ§жЎМфЕФЯрЙиЬиадНЯДѓЃЌЖдгкЪЕЪБадвЊЧѓИпЁЂаХЯЂжЁНЯЖЬЕФЭЈаХЯЕЭГЃЌадФмгХгкЮБЫцЛњКЭАыЮБЫцЛњЪННЛжЏЦїЁЃ ЫцзХаХЯЂжЁГЄЖШЕФдіМгЃЌНЛжЏГЄЖШвВЯргІдіГЄЃЌДЫЪБШєВЩгУОиеѓЗжзщНЛжЏЦїЃЌНЛжЏЧАКѓаХЯЂађСаЕФВЛЖЏЕудіЖрЃЌЮБЫцЛњЪ§ВњЩњИќМгОљдШЃЌНЛжЏЧАКѓЕФађСаЯрЙиадМѕаЁЃЌЫљвдЖдгквыТыОЋЖШвЊЧѓНЯИпЕФЭЈаХЯЕЭГЃЌгІВЩгУЫцЛњНЛжЏЦїЁЃ АыЮБЫцЛњНЛжЏЗНЪНдђЮЊелждЕФЗНАИЁЃ 2.2 ОиеѓЗжзщНЛжЏдРэ ЗжзщНЛжЏЦїЕФНсЙЙНЯЮЊМђЕЅЃЌЫћЪЧвЛИіmЁСnЕФОиеѓЁЃЫћАДааЕФЫГађаДШыДцДЂЦїЃЌдйАДСаЕФЫГађЖСГіЁЃИљОнЖСГіЗНЪНЕФВЛЭЌЃЌЗжзщНЛжЏЦїПЩЗжЮЊСНжжВЛЭЌЕФРраЭЃКAаЭЗжзщНЛжЏЦїКЭBаЭЗжзщНЛжЏЦїЁЃАДаааДШыЃЌАДСаЕФЯШКѓЫГађж№СаЖСГіЃЌГЦЮЊAаЭНЛжЏЦїЃЛАДаааДШыЃЌАДСаЕФЕЙађЖСГіЃЌМДДгзюКѓвЛСаЯђЕквЛСаЖСГіЃЌЖјЖдгкУПвЛСадђЪЧАДееДгзюКѓвЛааЯђЕквЛааЕФЫГађЖСГіЃЌГЦЮЊBаЭНЛжЏЦїЁЃ ШчЭМ1ЫљЪОЃЌМйЩшаХЯЂБШЬиЕФЪфШыЫГађЪЧЃКd11,d12ЃЌЁЃЌd1nЃЌd21ЃЌd22ЃЌЁЃЌd2nЃЌЁЃЌdm1ЃЌdm2ЃЌЁЃЌdmnЁЃЖдгкAаЭЗжзщНЛжЏЦїЃЌЖСГіЫГађЮЊЃКd11ЃЌd21ЃЌЁЃЌdm1,d12ЃЌd22,ЁЃЌdm2ЃЌЁЃЌd1nЃЌd2nЃЌЁЃЌdmnЃЛЖдгкBаЭЗжзщНЛжЏЦїЃЌЖСГіЫГађЮЊЃКdmnЃЌЁЃЌd2nЃЌd1n,ЁЃЌdm2ЃЌЁЃЌd22ЃЌd12ЃЌdm1ЃЌЁЃЌd2lЃЌd11ЁЃ ЖдгкШЮКЮГЄЖШlЁмmЕФЭЛЗЂДэЮѓОНЛжЏКѓГЩЮЊжСЩйБЛn-1ЮЛИєПЊЕФвЛаЉЕЅИіЖРСЂВюДэЁЃ 3 НЛжЏЦїЕФЩшМЦ БОНкеыЖдCDMA2000ЕФЛАвєБъзМЫйТЪЮЊ9.6 kbЃЏsЃЌЯргІУПжЁЪ§ОнГЄЖШЮЊ192 bЁЃИјГіСЫгУПЩБрГЬТпМЦїМўРДЪЕЯжAаЭЗжзщБШЬиНЛжЏЦїЁЃВЩгУЕФШэМўПЊЗЂЛЗОГЪЧMax+PlusЂђЃЌВЩгУздЖЅЯђЯТ(Top-Down)ЕФЩшМЦЗНЗЈЁЃ  3.1 НЛжЏаЮЪНЕФбЁдё НЛжЏаЮЪНЕФбЁдёгІБЃжЄДЋЪфЕФЪ§зжађСадкНЛжЏЧАКѓВЛЖЏЕузюЩйЃЌВЂЧвЯрЙиадзюаЁЁЃCDMA2000жаУПжЁЕФЪ§ОнГЄЖШЗжБ№ЮЊ192 bЃЌУПжЁДѓдМЮЊ20 msЁЃФЧУДПЩбЁгУЕФНЛжЏГЄЖШжЛФмгыДЫДѓжТЯрЕБЁЃЮФЯзМЦЫуБШНЯСЫ12ЁС16ЃЌ13ЁС15ЃЌ14ЁС14Ш§жжНЛжЏаЭЪНЃЌШчБэ1ЫљЪОЁЃЗжЮіПЩжЊЃЌЮвУЧЕФЩшМЦгІВЩгУ12зщТызжНјааНЛжЏЃЌУПзщ16 bТыГЄЃЌНЛжЏГЄЖШЮЊ192 bЁЃ  3.2 ећЬхЩшМЦ БОЩшМЦвдRAMПщзїЮЊжїЬхФЃПщЃЌНЛжЏЦїЕФЪЕЯжжївЊгЩ3ВПЗжзщГЩЃКЕижЗВњЩњФЃПщЁЂПижЦФЃПщКЭзїЮЊНЛжЏЪ§ОнДцДЂЕФНЛжЏМФДцЦїФЃПщЁЃ ЮЊСЫБЃжЄЖдгкДЋЪфЪ§ОнађСаНЛжЏЕФСЌајадЃЌбЁШЁСЫ2ЦЌRAMПщгУРДНјааНЛжЏДцДЂЁЃВЩгУЦЙХвЕФЙЄзїЗНЪНЃЌШчДЫЗДИДбЛЗЃЌдкБЃжЄДЋЪфЪЕЪБадЕФЬѕМўЯТЃЌОЭЭъГЩСЫЪ§ОнЕФНЛжЏЁЃ ЭМ2ЪОГіСЫОпЬхЕФНЛжЏЦїЕФЪЕЯждРэПђЭМЁЃИУЯЕЭГга6ИіЪфШыаХКХЃЌЗжБ№ЮЊЪфШыЪ§ОнЪБжгаХКХ(DatainCLK)ЃЌЯЕЭГЙЄзїдЪаэаХКХ(en)ЃЌЯЕЭГЧхСуаХКХ(sclr)ЃЌЪфГіЪ§ОнЪБжгаХКХ(Dataout CLK)ЃЌЪфГіЪ§ОндЪаэаХКХ(Dataout en)КЭД§НЛжЏаХЯЂађСаЁЃИУЯЕЭГгавЛИіЪфГіаХКХЃЌЮЊНЛжЏКѓЕФаХЯЂађСаЁЃ  3.3 ЖСаДЕижЗВњЩњФЃПщ ЭМ3ИјГіСЫгІгУMax+PlusЂђШэМўЖдНЛжЏЦїЖСЃЏаДЕижЗВњЩњЦїНјааЩшМЦЕФОпЬхЕФЕчТЗСЌНгЭМЁЃ  ЭМ4ИјГіСЫбЁгУMax+PlusЂђШэМўВЫЕЅУќСюFileЃЏCreate Default SymbolЃЌЩњГЩЕФЖСЃЏаДЕижЗВњЩњЦїЕФТпМЗћКХЁЃетбљИУЖСЃЏаДЕижЗВњЩњЦїОЭПЩвдЯёЦфЫћТпМЗћКХвЛбљЃЌдкЭМаЮЩшМЦЮФМўжаШЮвтЕїгУЁЃИУТпМЗћКХЕФЪфГіГ§СЫ8ЮЛЖСЃЏаДЕижЗЭтЃЌЛЙгавЛИіНјЮЛаХКХCARЁЃИУНјЮЛаХКХЙЉПижЦФЃПщВњЩњПижЦаХКХЪЙгУЁЃ  3.4 НЛжЏЦїЕФећЬхЕчТЗ ЭМ5ИјГіСЫгІгУMax+PlusЂђШэМўЪЕЯжЕФНЛжЏЦїЩшМЦЕФећЬхТпМдРэЭМЁЃ 3ИіЖўбЁвЛЕФбЁдёЦїЁЃЦфжага2ИібЁдёЦїдкПижЦаХКХЕФзїгУЯТЗжБ№ЭъГЩЖд2ЦЌRAMЖСЃЏаДЕижЗЕФбЁдёЃЌвђЮЊ2ЦЌRAMЕФЖСаДЫГађе§КУЯрЗДЃЌЫљвдгІЖдПижЦаХКХНјааЯргІЕФШЁЗЧВйзїЁЃСэвЛИібЁдёЦїЭъГЩЖд2ЦЌRAMЪфГіЪ§ОнНјаабЁдёЃЌбЁдёЦїЕФзюжеЪфГіЪ§ОнзїЮЊНЛжЏКѓЕФЪ§ОнЁЃгЩгкЪ§ОндкДцШыКЭЖСГіRAMЪБв§ШыСЫвЛИіАыжмЦкЕФбгЪБЃЌЫљвдгІгУСЫ2ИіDДЅЗЂЦїdffc2РДЯћГ§ЪЙФмаХКХгыЪБжгжЎМфЕФбгЪБЁЃЪ§ОнЪфГіЖЫЕФDДЅЗЂЦїmdffЪЧЮЊСЫЯћГ§ЪфГіаХКХЕФУЋДЬЖјЩшМЦЕФЁЃ ИљОнЯЕЭГЕФЙЄзїдРэЃЌЩшМЦГіПижЦЪБађЃЌНјааЗТецЕФНсЙћШчЭМ6ЫљЪОЁЃ ЯЕЭГЗТецЪБЪфШыНЛжЏЦїЕФДЎааТызщЮЊ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ0ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1ЃЌ1НЛЬцађСаЃЌгЩAаЭЗжзщНЛжЏЦїЕФЙЄзїдРэПЩжЊЃЌЕУЕНЕФНЛжЏКѓЕФЪфГіЪ§ОнЮЊOЃЌ1НЛЬцЕФађСаЁЃИУВЈаЮЗТецНсЙћБэУїНЛжЏЦїе§ГЃЙЄзїЁЃДгЭМ6жаПЩвдПДГіЃЌИУНЛжЏЦїДгД§НЛжЏЪ§ОнЪфШыЕННЛжЏКѓЪфГіга7.79ІЬsЕФбгЪБДцдкЁЃЭМжадк7.79ІЬsвдЧАЃЌЪфГіЕФЪ§ОнЮЊ0ЪЧвђЮЊRAMПщжаЕФГѕЪМЪ§ОнЮЊOЁЃ  3.5 НтНЛжЏЦїЕФЩшМЦ НтНЛжЏЪЧНЛжЏЕФФцЙ§ГЬЃЌетОіЖЈСЫНтНЛжЏЦїКЭНЛжЏЦїЖдгкНЛжЏЪ§ОндкНЛжЏОиеѓжаЕФЖСЃЏаДЫГађе§КУЯрЗДЁЃдкНтНЛжЏЦїЕФЩшМЦжаЃЎИФЖЏЕФВПЗжжЛЪЧдк2ЦЌRAMЕФЖСЃЏаДбЁдёаХКХЧАЗжБ№МгСЫвЛИіЗЧУХЁЃДгЖјПЩвдЭъГЩНтНЛжЏЪ§ОнАДНЛжЏЕижЗаДШыЃЌАДЫГађЕижЗЖСГіЃЌНјЖјЭъГЩНтНЛжЏЙ§ГЬЃЌЛжИДГідЪМЪ§зжаХЯЂађСаЁЃ 4 Нс гя ЖЬжЁЪ§зжЭЈаХЯЕЭГЪЪКЯВЩгУОиеѓЪНЗжзщНЛжЏЃЌБОЮФвдCDMA2000гявєДЋЪфБъзМЯТЖЬжЁЮЊР§ЃЌИјГіСЫОпЬхЕФ12ЁС16ЕФAаЭЗжзщБШЬиНЛжЏЦїКЭНтНЛжЏЦїЁЃдкЪЕМЪжаЃЌИУЩшМЦЗНАИдкВЛдіМгЯЕЭГИДдгЖШЕФЧщПіЯТЃЌжЛашЖдЯргІЕФФЃПщНјаааоИФЃЌКмШнвзЪЕЯжНЛжЏЩюЖШКЭаЮЪНЕФИФЖЏЃЌОпгаживЊЕФВЮПММлжЕЁЃ |

ЭјгбЦРТл