直击100GbE险境: 基于FPGA硬件加速的BittWare StreamSleuth对抗100Gbps

发布时间:2017-5-12 14:36

发布者:eechina

|

作者:清风流云 在过去的三十年中,以太网已经发展成为所有行业的统一通信基础架构。每天都有超过三百万的以太网端口在部署,覆盖从FE到100GbE的所有速度。企业和运营商在部署时通常会使用盒式的交换设备和堆叠和高密度机箱式交换机的组合,来应对以太网的不断演进。然而,在过去的几年中,以太网发展态势正在持续改变。随着数据中心以太网部署和创新都在以最快的速度进行着,数据中心的以太网端口部署趋于一致,无论是10GbE、25GbE或50GbE,相同的以太网端口速度通过一个机架架顶(ToR)交换机被部署于每一个服务器上,然后聚集到多个CLOS层。最终目的是将尽可能多的以太网端口以最高的商用速度部署在以太网交换机上,并使其最经济和最节能。连接到ToR交换机的终端是服务器NIC(网络接口卡),它一般是市场上可用的最高速度(目前为10/25GbE,正在向25/50GbE方向发展)。 今天,25GbE交换机的128个接口正在部署中,在接下来的几年内会到达并超越64x 100GbE。但是,尽管数据中心正在向更高的端口密度、更高的端口速度和同质部署方向发展,但是更低的速度仍拥有广泛市场,比如10GbE继续被使用并仍具有经济效益。数据中心的创新带动更高密度和更高端口速度的发展,但很多细分市场仍需要具备较低端口速度和不同密度的解决方案。 BittWare最新开发的StreamSleuth: 正如BittWare提到,只有CPU而没有硬件加速是无法处理100Gbe的数据包交互的。而正式亮相于本次旧金山RSA大会的BittWare最新开发的StreamSleuth(流侦探),通过一个FPGA 助手,敏捷且迅速的将数据流分组了,此外,BittWare还表示,StreamSleuth使基于FPGA编程实现数据包处理机制时,没有任何FPGA编程的负担,也就是说,在编程的时候你并不需要精通Verilog或是VHDL这些硬件语言 ,就可以很方便的将FPGA的高性能应用到自己的应用中。

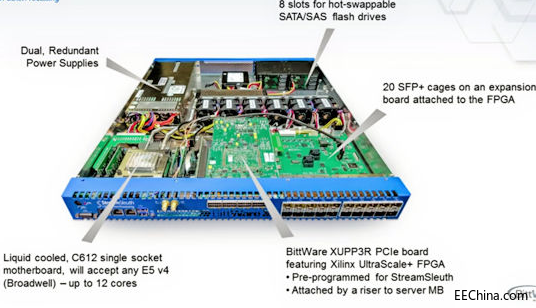

图1 StreamSleuth接口侧 正如BittWare的网络产品VP&GM发言人 Graig Lund解释,这并不是由一个随时可以重组的箱子组成的一个装置。用户往往需要或许也更想去量身定做它,比如说,在制作的时候,有的人想添加数据包过滤器,有的人想对数据交互的过程进行监视。用户在基于线速度是使用StreamSleuth做出任何想做的东西,而唯一不需要用户去做的,就是学习如何编程FPGA。尽管用户没有任何编程FPGA的经历,依然可以将FPGA的技术优势完美的应用的自己的应用中。也因此方便更多的网络或数据库工程师来使用BittWare的StreamSleuth。 正如Lund所说,相比以太网以前的低版本产品StreamSleuth是一个十分不同的创造物。一直以来,服务器都不可以直接处理100GbE的数据交互,而且此状态一直没有得到解决。而现在的网络管道却别服务器内部的I/O管道大得多,进入服务器的数据量成指数增长,同时也导致了CPU设计时不得不增加三级缓存来缓解数据堵塞。 或许我们听到过更糟糕的情况,对于一个服务器而言,如何减少网络阻塞,无疑是需要增加滤波器,很多滤波器,很多复杂的滤波器,比现在商品转化和防火墙器件更多的复杂滤波器。理论上说,需要用一种语言基于线速度快速完成标准的BPF/pcap滤波器的实现,类似一个基于高度并行FPGA的数据包发动机。 当然,以上这种做法对于减轻100Gbe的线路速率也是有作用的,但是目前的硬件并做不到,也没办法用软件来实现。最终的出路在于FPGA,所以BittWare的基于FPGA数据处理的StreamSleuth成功的实现了用户想要达到的效果。 以软件实现的防御并不可以抵挡100Gbe线路速率的DoS,但是基于FPGA加速实现的数据包处理器可以。所以我们也明白了StreamSleuth内部的FPGA到底做了什么工作,它重配置了数据包滤波器,使得加载和路由变得平衡。同时,应用BPF/pcap语言为自己的需求编程,并通过GUI或APIs烧录到StreamSleuth 100Gbe数据包处理器中,就可以实现自己的需求。而此数据处理器中集成的是一款Xilinx Virtex UltraScale+ VU9P FPGA 板卡。 下图就是BittWare的StreamSleuth的板卡内部结构:

总结: 无论是视频流处理还是数据流处理,现如今,只要需要用到加速器来实现的应用已经越来越多的通过基于FPGA来进行硬件加速,不仅可以真正意义上的并行,加快运行速度,也可以降低CPU执行软件的压力。可见,基于FPGA来硬件加速将会是加速器未来的发展方向。 |

网友评论