45nm及更小节点可制造性探索

发布时间:2010-11-3 10:26

发布者:李宽

|

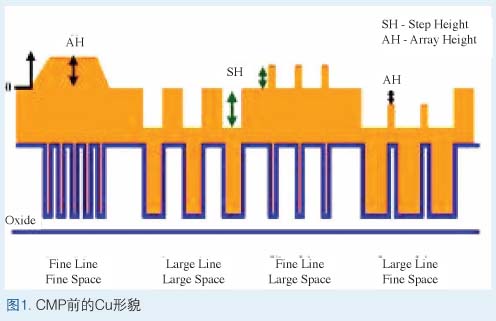

DFM是Design for Manufacturability(可制造性设计)的简称,主要研究产品本身的物理设计与制造系统各部分之间的相互关系,并把它用于产品设计中以便将整个制造系统融合在一起进行总体优化。DFM可以降低产品的开发周期和成本,使之能更顺利地投入生产。 在半导体垂直分工细致化的今天,晶圆代工厂与IC设计厂商彼此间的领域相当分明,许多的设计参数不如IDM的关系紧密,更需要透过DFM提升IC设计厂商投片以后的生产良率,以降低成本、缩短产品上市时间。因此,半导体界也戏称DFM是“Design for Money”,意思就是要把设计转化成获利。 设计、材料与制程三者间的相互作用,是导致良率问题加剧的主要原因。过去所须考虑的制程缺陷多半是导孔(Via)或颗粒(Particle)所造成的问题,晶圆厂尚能处理。然而,至65与45nm后,除上述问题外,更增添许多新缺陷,尤其又以光刻与化学机械研磨(CMP)过程所造成的影响较大。这些因为制程变异所带来问题,就必须藉由DFM的技术加以改善。 易变性对45nm及更小节点的影响 大马士革工艺的平坦化步骤使得金属互连及通孔的多层堆叠成为可能。互连层数越多,互连节距就越严密,每一步非平面性的容差就越小,因为平面性是一个累计度量。为了平均待刻蚀材料的密度和均匀性,在每一层的光空间中若没有附加的“虚拟填充”,单独用CMP是达不到要求的。基于规则的填充图形是采用通过插入填充光空间的重复图形。这对铝合金和Cu弛豫规则很有效。当互连节距规则更紧密时,通过沟槽的Cu籽晶用电镀工艺淀积的Cu导致了淀积后的更不均匀性(图1)。

这样,基于规则的填充完成此工作就不适当了,需要仿真推动的基于模型的规则。基于模型的填充没有同一重复图形,而是按仿真需要插入,以达到使金属和ILD厚度的峰-峰变化局部最小化的目的。 基于模型的化学机械抛光(CMP)已成为65nm及更小技术的关键,因为其影响的重要性已超越良率和可靠性对技术节点本身可制造性要素的影响。而且,随着每一新节点金属节距更为紧密,CMP对互连提取精度、时序和信号完整性的影响需要精心建模和评估。 本文论及从基于规则的CMP到基于模型的CMP,以及其对可制造性、可靠性、互连、时序和信号完整性的重大影响。 可制造性 从设计到实现功能和产出的序列,首先需要可制造。方程式(1)和(2)(瑞利方程)表明分辨率R和焦深 DOF同时为照明波长λ和投影镜数值孔径NA的函数。k1与k2是与系统相关的特定因子,在0.4至0.65范围内。对DOF简单计算表明,它只有几十纳米。这实际上是所有互连层上ILD中累计非平面性允许范围的上限。超过它就完全没有可刻印性。这说明了在形成仿真推动基于模型的填充中需要做出额外努力,以使ILD厚度局部峰-峰波动最小。 R = k1*λ/NA (1) DOF = (K2*λ)/NA2 (2)

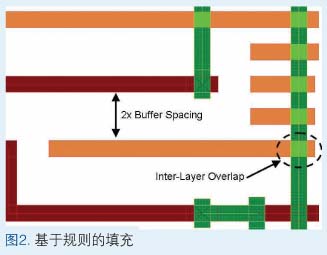

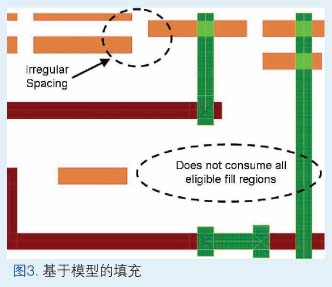

图2对基于规则的填充作了说明。这是离实际连线特定间隔处在标准的重复剥离中做的,作为缓冲间隔。对比之下,图3说明了仿真推动基于模型的填充。没有规律性,一般说来,为了在ILD易变性中获得较好的峰-峰控制所需的填充密度较低。很明显,这对电容和延迟有附加的影响,下一节将予以说明。

时序和互连 不断缩小的IC特征尺寸使RC互连延迟呈现增加的趋势。单个芯片的处理能力越强,就越需在较小的空间内集成并互连更多的逻辑门。这将加大布局和布线的复杂度,使得线路更加拥挤。为了容纳下所有这些连线,金属互连的宽度必须不断减少,同时金属层数却不断增加。由于金属阻抗与其宽度成反比,人们开始采用改变金属连线横截面长宽比的方法来控制阻抗(从而将RC互连延迟限定在合理范围内)。 由于线宽减小了,导线由短粗变为细长以控制阻抗。长宽比的改变又加剧了相邻连线间电气特性的相互影响,这要用邻线间的耦合电容进行建模。另外,由于IC金属互连层数不断增加,较高金属层到基底层的距离也在不断减小,从而减小了对地的电容量。 大多数情况下,金属填充是与路由器结合进行的,填充程序镶嵌在路由算法中。无论填充是基于规则或是基于金属,对于填充物有一些通用参数,其中最重要的是填充和有效信号间的最小间距。此最小间距可作为缓冲器间距,这里,1×代表最小的节距间隔等等。而且,填充可以是浮动的或接地的,一般是浮动的填充。评估金属填充对电容负载(即对延迟)的影响是相当繁冗的,大多数静态时序引擎不能很好地处理。可是,精确测定这一影响是极其重要的,因为它能大大改变性能。

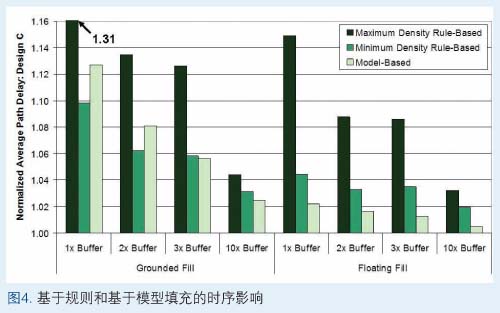

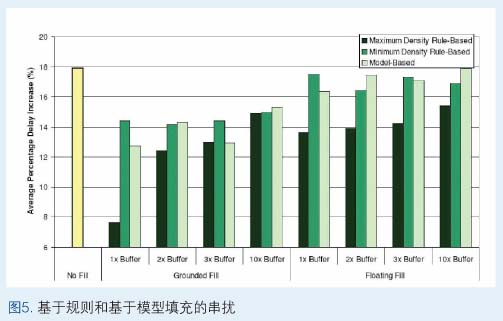

采用主流供应商的EDA工具对CMP建模和仿真,并准确的提取寄生参数,我们将有金属填充的关键路径延迟对没有任何填充的同一值归一化。对1×、 2×、3×和10×缓冲间距及浮动填充和接地填充二种情况进行了归一化工作。对基于规则的填充,研究了在代工厂设计规则中规定的层密度最大和最小二种极端情况。图4示出了所有这些情况的归一化关键路径延迟。用它作为评价互连值(它们是密切跟随的)的近似替代参数也是可靠的。 结果证实了关于缓冲间距以及接地/浮动这一问题的直觉想法。最坏情况对应高密度填充、接地和1×缓冲间距处是合理的。实际上图4表明最坏情况的影响有31%。当缓冲间距增加时,此影响在3×缓冲间距处降低至约5%也是合理的(根据耦合电容是距离的函数)。再大就没有什么好处了。基础分析说明,将填充接地会有较高的耦合电容,因而延迟增加,但仍有少数人选择填充接地,因为与浮动接地比较,它有非常好的可预测性。这些实验非常有用,因为它确立了3×缓冲间距作为用于缓冲的合理选择,它量化了其对时序(和寄生参量)的影响为约5%。有一点必须注意,金属填充一般会改变关键路径的次序。这是可以预期的,因为对何种信号在填充附近结束及何种信号不在填充附近结束不易控制。 可靠性和信号完整性 处理金属填充的信号完整性是互连寄生参量提取的直接结果。我们用延迟作为代理参数量化金属填充耦合引起的净电容增加(虽然要进行琐细的数据提取工作)。用具有动静对标准总线结构的HSpice评估串扰延迟和畸变对动静对的影响。采用与上节同样的缓冲、密度、接地和基于规则/基于模型填充的安排。结果见图5,每一项再次归一化并与没填充情况作了比较。结果又一次符合图5与图4中的趋势正好相反的直觉想法,就 1×缓冲来说,由于电容耦合严重而得到了最差的延迟效应。同等的电容耦合产生的串扰最小等等。

结论 瑞利方程为任一技术节点确立了最大的焦深允许范围,DOF随每一新节点持续变小。因此,仿真推动的基于模型填充是使ILD内局部峰-峰变化最小的途径,允许我们在DOF范围内运作,这是对可制造性和良率至关重要的事情。金属填充对性能和信号完整性的影响是什么,什么样的缓冲间距是最佳的。结论是:在保证可制造性、可靠性和很好良率的同时,3×缓冲间距处基于模型的填充产生比较稳定的时序,且最坏情况下对时序预计的影响为5%。 DFM的概念已被整合至设计实践中,未来IC设计业者将拥有一个虚拟制造的设计环境,透过EDA工具的协助,进行问题侦测、修正及预防,进一步提高整体IC制造良率。 感谢 特别感谢Rice University 攻读博士学位的Arthur Nieuwoudt进行的全部仿真工作和有关的深入研讨及创意,也特别感谢他的导师Rice University的 Dr. Yehia Massoud 的有益讨论和建议。 可制造性设计 半导体制程技术的演进大致依循摩尔定律(Moore's Law):每两年进步一代,布局规则(Layout Rule)持续需较前代原始设计微缩70%,使集成电路(IC)单位面积内含晶体管的数量增加一倍。集成电路制程技术不断的微缩,在稳定性的控制上日渐艰难,许多制程上的衍生效应于先前设计时并未被充分考虑,使得IC的Margin及良率提升的速度在开始受到明显的影响。因此一些可制造性设计 (Design For Manufacturability,以下简称DFM)的解决方案,在近年来开始成为重要的主题。 DFM或相似DFY(Design for Yield,良率导向设计),简而言之即由制程人员将IC由设计完到制造过程所可能发生的各种效应(Effects)及变化(Variation),以及更重要的对IC功能的影响加以仔细的分析检测,而设计者在设计流程中即将这些信息考虑含入,使所设计的IC对制程变化有更好的容忍度 (tolerance),以及更容易有较高的良率。DFM衍生出许多新而复杂的课题需要芯片设计者及制程提供者携手合作,也有别于传统的设计 - 制程分工模式。

设计业者需有适当可用的自动化设计软件工具(EDA Tool),使设计业者在设计之初,就可以利用这些工具所模拟的结果来修正设计,以确保所设计与制造的结果相近。所以DFM 解决方案的最后目标需实现于EDA 工具上。所以设计者、EDA 工具业者及制程提供者是完整方案的铁三角。 在联电在 90nm制造所提出的可制造性设计方案支持流程(DFM Support Flow)如图所示。其中包括可制造性设计建议的IP及Library;在设计阶段亦提供客户DFT(Design-For-Test)及 DFD(Design-For-Diagnosis)两种服务;在出光掩膜之前及之后提供客户LRC/OPC等服务(Pre/Post Tape/Out LRC/OPC Service)。 可制造性设计的整套方案都必须要设计业者的配合,才能为产品良率共同创造双赢。在此同时,也要设计业者不断的提供意见给芯片制造商来共同提升整个可制造性设计方案。 |

网友评论