利用Cadence设计COMS低噪声放大器

发布时间:2010-10-30 18:08

发布者:conniede

|

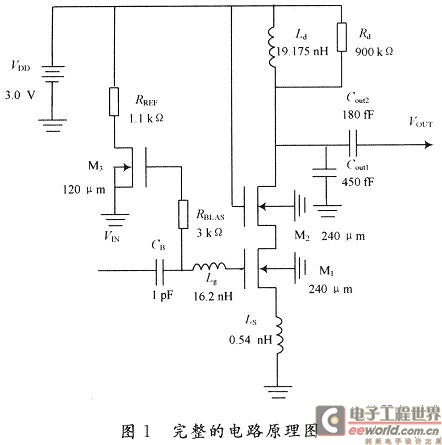

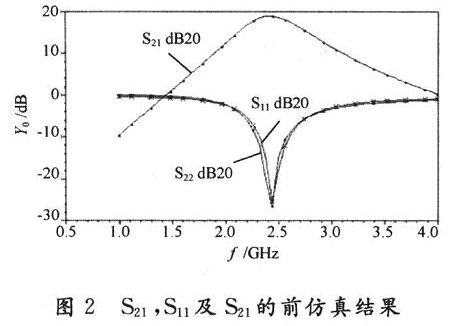

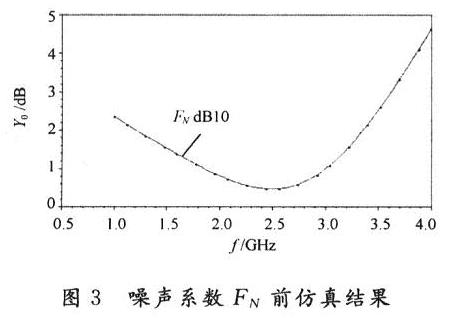

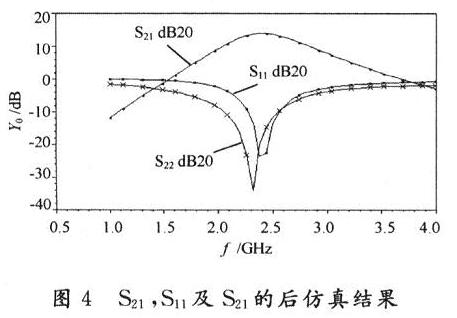

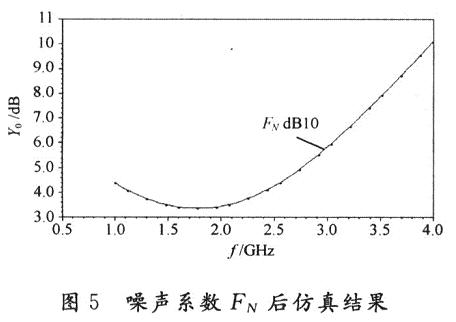

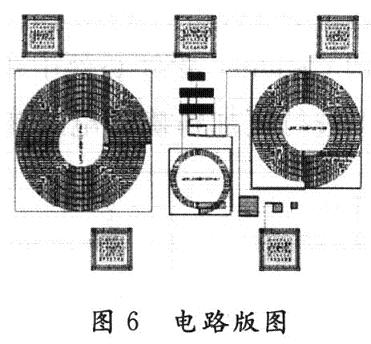

1 引 言 Cadence Design Systems Inc.是全球最大的电子设计技术、程序方案服务和设计服务供应商。它的解决方案旨在提升和监控半导体、计算机系统、网络工程和电信设备、消费电子产品以及其他各类型电子产品的设计。Cadence公司的电子设计自动化产品涵盖了电子设计的整个流程,包括系统级设计、功能验证、IC综合及布局布线、模拟和混合信号及射频IC设计、全定制集成电路设计、IC物理验证、PCB设计和硬件仿真建模等。Cadence软件支持自顶向下(Top-down)的芯片设计,是业界广泛采用的设计工具。该软件通过Li-brary CelI View三级目录辅助芯片设计: (1)设计者为自己要完成的系统任务建立新的Li-brary; (2)分析系统及其指标来确定系统的各个模块,每个模块对应于Library中的一个Cell; (3)每个模块的设计包括电路(Schematic)设计和版图(Layout)设计,两者密不可分,电路图与版图都是模块中的View。 同时,Cadence公司还提供设计方法教学服务,帮助客户优化其设计流程;提供设计外包服务,协助客户进入新的市场领域。垂直解决方案是Cadence 为帮助IC设计公司迅速建立设计架构,并获得更短、可预测性更高的设计周期而推出的独具特色的整套解决方案,其目标是为了推动不同领域产品的开发步伐,设计锦囊(Process Design Kit,PDK)是其重要组成部分。“锦囊”通过将验证方式和流程与IP相结合的方式,更好地应对无线、网络和消费电子等不同领域在设计方面的挑战。通过采用“锦囊”,用户可将其宝贵的资源投入在差异化设计而不是基础设计方面。 2 低噪声放大器电路设计 (1)电路结构。图1是此次实验中所用电路的完整电路原理图。图中共源管M1作为主放大管,给电路提供足够的增益;共栅管 M2用来减小M1的Cgd1引起的密勒效应以及增强整个电路的反向隔离性能;M3,Rref,Rbias构成偏置电路,以实现M1所需的直流偏置。对于输入/输出匹配电路,可以利用Smith圆图完成初步设计;然后利用Cadence软件套件中用于集成电路仿真的组件IC 5.1进行更加精确的电路参数调试。  (2)电路设计。设计中采用新加坡特许(CHRT)的0.35μm RF CMOS工艺。电路工作在2.4 GHz,信号源电阻为50 Ω,M1的偏置电流取为5 mA。根据文献,通过计算可得CHRT 0.35 μm COMS工艺Cox的值约为4.6mF/m2,根据文献[4,5]可以得到最优栅宽公式:Wopt△1/3ωLCoxRs,计算得M1的最优宽度约为 240μm。根据公式RS=ωtLS,可得LS的值约为O.54 nH。根据公式CRS=(2/3)WoptLCox,得到CgS的值约为150 fF。将LS和CgS的值代入公式 为输入信号角频率),可以得到Lg的值约为16.2 nH。偏置电路中M3的尺寸和电流选为M1的1/2。 3 仿真与调试 (1)电路原理图仿真。IC 5.1.41中用到的原理图编辑器是Virtuoso Schematic Editor。首先,在编辑器中输入图1所示的低噪声放大器完整的电路原理图。接着,为了完成电路仿真,得到所需的电路参数,还需要在模拟环境 (Analog Design Environment)进行必要的设置,比如电路中用到的各个变量取值、S参数仿真(SP仿真)或者直流(DC)仿真的参数等。这些在软件的用户手册 (Cdsdoc)以及一些相关的使用教程里面都有详细的说明,在此不再重复。 在必要的软件设置都完成之后,便可以顺利地将电路原理图转换成网表并仿真(Netlist and Run),从而得到感兴趣的电路参数,软件默认启动的仿真器是spec-tre。在此次的低噪声放大器设计过程中,主要关注电路的S参数、噪声系数FN。 为了将输出阻抗匹配到50 Ω,首先可以利用Smith圆图来完成输出匹配的初步设计。通过计算,本次设计需要在负载电路端并联一个电容Cout1,然后串联一个电容Cout2。通过调试,确定Cout1和Cout2的值分别约为180 fF和450 fF。 (2)电路版图设计。版图是集成电路设计中十分重要的一环,它对射频电路的性能有很大的影响。由于工作频率很高,寄生效应和衬底耦合效应很明显,因此要整体考虑其布局布线,尽量减小寄生参数的影响。首先,布局要合理,要注意信号线的走线长度,无源器件,特别是电感和其他部分要保持适当的间距;信号线要尽量宽些,这样可以降低串联电感和寄生电阻; 要尽可能的多用地线,电源线与地线尽量平行,以形成去耦电容,达到去除电源的高频耦合分量的目的; 电源线尽量采用底层金属,RF信号线尽量采用顶层金属,而在版图空白处尽量多布地线,尽可能地降低走线过程中的衬底损耗和串扰。 结合CHRT 0.35μm RF CMOS工艺的PDK,可以很方便地生成电路的元器件版图输出,接着完成必要的电路连线,便可以得到电路的版图结果。 电路实现版图设计之后还需要完成物理验证。 此次采用的验证工具是IC 5.1中自带的DIVA。除此之外,也可以采用Cadence公司的ASSura,或者Mentor Grahphics公司的Calibre。物理验证的过程包括设计规则检查(DRC)、版图原理图对比(LVS)以及寄生参数提取(Extract)三个步骤。 在版图编辑器(Layout XL Edit)的Verify菜单当中,可以找到DRC,LVS,Extract对应的选项;在完成了必要的参数设置之后,便可以完成电路的物理验证。在做完寄生参数提取之后,便可以利用包含寄生参数的电路完成电路后仿真(Post-layout simulation),从而得到与实际电路性能更为接近的各项仿真结果。 (3)实验结果。在完成最终电路的调试后,得到了各项仿真结果。 图2、图3分别是用电路原理图仿真(即前仿)得到的S参数以及噪声系数FN的实验结果。   图4、图5是完成版图之后,考虑寄生参数的电路后仿真结果。图4是S参数的后仿真结果。由S11,S22的曲线可知,在2.4 GHz的中心频率附近,S11,S22<-10 dB。可见,输入、输出电路均有比较好的匹配。图5是噪声系数FN的后仿真结果。图6为电路版图。    与电路的前仿结果相比,后仿真的噪声系数有一定的上升,这说明电路中的寄生参数会使电路的噪声性能恶化。 4 结 语 结合一个具体的低噪声放大器(LNA)设计实例,采用CHRT的0.35μm RFCMOS工艺,在EDA软件IC 5.1设计环境中设计了一个2.4 GHz的低噪声放大器。设计过程中完成了电路原理图仿真、版图设计以及后仿真。实验结果表明该低噪声放大器具有较好的电路性能。结合设计过程,还介绍了如何运用Cadence软件对CMOS低噪声放大器进行电路设计和仿真。 |

网友评论