CMOSНјПсҙ«ёРЖчIBIS5-B-1300өДЗэ¶ҜКұРтЙијЖ

·ўІјКұјдЈә2010-10-28 15:50

·ўІјХЯЈәtechshare

|

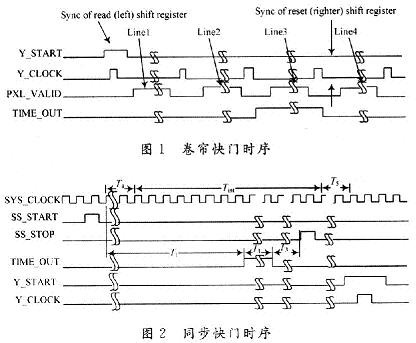

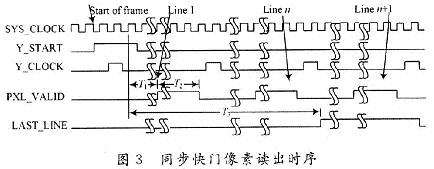

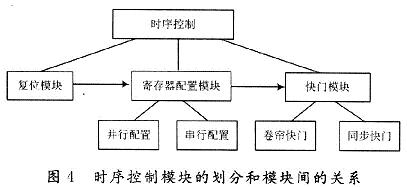

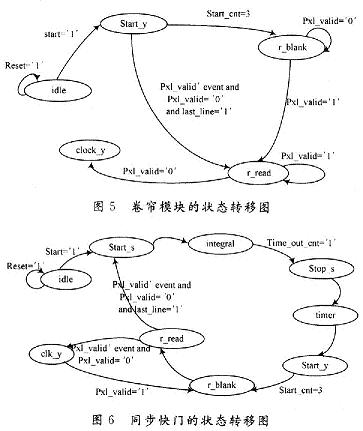

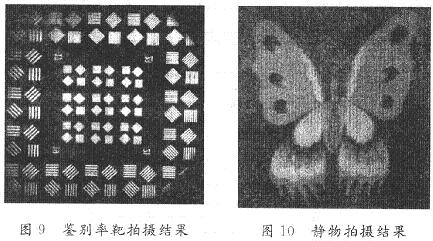

CMOSНјПсҙ«ёРЖчІъЙъУЪ20КАјН80ДкҙъЈ¬УЙУЪөұКұCMOS№ӨТХөДЦЖФмјјКхІ»ёЯЈ¬ТФЦБУЪҙ«ёРЖчФЪУҰУГЦРөДФУС¶ҪПҙуЈ¬ЙМЖ·»ҜөДҪшіМТ»ЦұәЬВэЎЈЦБҪсЈ¬ЛжЧЕ№ӨТХөДІ»¶ПМбёЯЈ¬CMOSНјПсҙ«ёРЖчөДУҰУГ·¶О§ТІІ»¶ПА©ҙуЈ¬Йжј°өҪКэВлІъЖ·ЎўНЁС¶Ўў№ӨТөЈ¬ТҪБЖөИёчБмУтЎЈУлCCDПаұИЈ¬CMOSНјПсҙ«ёРЖчҫЯУРМе»эРЎЈ¬№ҰәДөНЈ¬іЙұҫөНөИМШөгЎЈCypress№«ЛҫөДCMOSНјПсҙ«ёРЖчIBIS5-B-1300КЗТ»ҝоёЯРФДЬЎўҙу¶ҜМ¬·¶О§өДНјПсҙ«ёРЖчЎЈНјПсҙ«ёРЖчөДХэіЈ№ӨЧчРиТӘУРХэИ·өДЗэ¶ҜКұРтРЕәЕЈ¬ұҫОДҫННјПсҙ«ёРЖчIBIS5-B-1300Ј¬ёшіцІЙУГVHDLУпСФЙијЖөДЗэ¶ҜКұРтәН·ВХжҪб№ыЎЈ 1 IBIS5-B-1300НјПсҙ«ёРЖч 1Ј®1 РҫЖ¬јтҪй Cypress№«ЛҫөДIBIS5-B-1300Ҫ«ДЈДвНјПс»сИЎЎўКэЧЦ»ҜәНКэЧЦРЕәЕҙҰАнөД№ҰДЬјҜіЙФЪөҘТ»РҫЖ¬ЦРЈ¬КЗТ»ҝоёЯРФДЬөДCMOSНјПсҙ«ёРЖчЎЈХвҝо130НтПсЛШ(1 280ЎБ1 024)өДНјПсҙ«ёРЖчҝЙТФІЙУГSXGA»тVGAёсКҪКдіцЈ¬ЦЎЖөҝЙҙп27Ј®5 fЈҜs(1 280ЎБ1 024)»т106 fЈҜs(640ЎБ480)ЎЈ ЖдЦчТӘМШөгИзПВЈә (1)6Ј®7ҰМmөДёЯМоідТтЧУПсЛШөҘФӘЎЈЛьҝЙК№ЖчјюөДБйГф¶ИҪПёЯЈ¬ФлЙщҪПРЎЎЈ (2)ёЯөД¶ҜМ¬·¶О§(өҘРұВК»э·ЦПВОӘ64 dB)ЎЈөұІЙУГЛ«РұВК»э·Ц»т¶аРұВК»э·ЦКұЈ¬¶ҜМ¬·¶О§ҝЙҪшТ»ІҪМбёЯЎЈ (3)Ж¬ФШҝЙөчХыФцТжәНЖ«ЦГөДКдіц·ЕҙуЖчЎЈЛьДЬК№РЕәЕөД¶¶¶ҜПЮЦЖФЪЖ¬ФШ10 b ADCөДКдИл·¶О§Ц®ДЪЎЈ (4)Ж¬ФШ40 MHzөД10 b ADCЎЈЛьҝЙЦұҪУ¶ФКдіцДЈДвРЕәЕҪшРРДЈЈҜКэЧӘ»»Ј¬ёГADCФЪөзЖшЙПУлНјПсҙ«ёРЖч·ЦАлЈ¬Из№ыРиТӘЈ¬ҝЙСЎФсІ»ҫӯДЈЈҜКэЧӘ»»¶шЦұҪУКдіцДЈДвРЕәЕЎЈ (5)Лж»ъҝӘҙ°ДЈКҪәНСЗІЙСщДЈКҪЎЈЛж»ъҝӘҙ°ДЈКҪҝЙТФЦ»¶ФёРРЛИӨөДЗшУтҪшРР¶БіцЈ»СЗІЙСщДЈКҪҝЙТФәЬәГөШВъЧгНјПсС№ЛхөДРиТӘЎЈ (6)Ж¬ФШКұРтУлҝШЦЖВЯјӯРтБР·ўЙъЖчЎўДЪІҝјДҙжЖчЎЈЛьҝЙК№өГЙијЖХЯУГҪПЙЩөДРЕәЕАҙҝШЦЖҙ«ёРЖчөД№ӨЧчЎЈ 1Ј®2 №ӨЧчФӯАн IBIS5-B-1300ДЪІҝУР12ёцјДҙжЖчЈ¬Мṩҙ«ёРЖч№ӨЧчЛщРиөДІОКэј°№ӨЧч·ҪКҪЎЈ¶ФјДҙжЖчРҙИлөДКэҫЭҫц¶ЁБЛҙ«ёРЖчөД№ӨЧчЧҙМ¬ЎЈјДҙжЖчөДКэҫЭРҙИлҪУҝЪУР3ЦЦЈәІўРРҪУҝЪЎўҙ®РРИэПЯҪУҝЪЎўҙ®РРБҪПЯҪУҝЪЎЈҝЙНЁ№эРҫЖ¬өДIF_MODEәНSER_MODE№ЬҪЕҪУІ»Н¬өДЦөАҙСЎФсІ»Н¬өДКэҫЭҪУҝЪДЈКҪ(Изұн1ЛщКҫ)ЎЈ  ІўРРҪУҝЪК№УГ16 bІўРРКдИлАҙФШИлРВөДјДҙжЖчЦөЎЈҙ®РР3ПЯҪУҝЪ(»тҙ®ЧӘІўҪУҝЪ)К№УГҙ®РРҪУҝЪҪ«КэҫЭТЖИлјДҙжЖч»әіеЖчЈ¬өұНкХыөДКэҫЭЧЦТЖИлјДҙжЖч»әіеЖчКұЈ¬КэҫЭЧЦІЕұ»ФШИлөұЗ°ХэФЪұаВлөДјДҙжЖчЎЈҙ®РР2ПЯКЗТ»ёцөҘПтөДҪУҝЪЈ¬ұҫОДФЭІ»Чц·ЦОцЎЈ IBIS5-B-1300ҫЯУРБҪЦЦҝмГЕ·ҪКҪЈәҫнБұҝмГЕәНН¬ІҪҝмГЕЈ¬УГјДҙжЖч(0000)өДbitOҪшРРЙи¶ЁЈ¬Ў°1ЎұОӘҫнБұҝмГЕЈ¬Ў°0ЎұОӘН¬ІҪҝмГЕЎЈКұРтИзНј1Ј¬Нј2ЛщКҫЎЈ  ФЪҫнБұҝмГЕДЈКҪПВЈ¬ЦЎЖөFrame period=(NrЈ®LinesЎБ(RBT+Pixel Period*NrЈ®Pixels))ЎЈ ФЪН¬ІҪҝмГЕДЈКҪПВЈ¬ЦЎЖөFrame period="Tint"+Tread out="Tint"+(NrЈ®LinesЎБ(RBT+Pixel PeriodЎБNrЈ®Pixels))ЎЈЖдЦРЈ¬TintОӘ»э·Ц(ЖШ№в)КұјдЈ»NrЈ®LinesОӘГҝЦЎ¶БіцөДРРКэЈ»NrЈ®PixelsОӘГҝРР¶БіцөДПсЛШКэЈ»RBTОӘРРҝХ°ЧКұјд(өдРНЦөОӘ3Ј®5 ms)Ј»Pixel PeriodОӘ1ЈҜ40 MHz="25" nsЎЈ ҫнБұҝмГЕЦРУРБҪёцy·ҪПтөДТЖО»јДҙжЖчЈ¬Т»ёцЦёПтХэФЪұ»¶БіцөДРРЈ¬БнТ»ёцЦёПтХэФЪұ»ёҙО»өДРРЈ¬БҪёцЦёХлУЙН¬Т»КұЦУy_clock(РРКұЦУ)Зэ¶ҜЈ¬ЛьГЗЦ®јдөДІоЦөҙъұнБЛ№в»э·ЦКұјдЎЈФЪҫнБұҝмГЕДЈКҪПВЈ¬ПсЛШөД¶БіцәНёҙО»Н¬КұҪшРРЈ¬ГҝРРПсЛШөДёҙО»әН¶БіцКЗЛіРтҪшРРөД(јыНј3)ЎЈПсЛШөД»э·ЦКұјдҝЙТФНЁ№эјДҙжЖчINT_TIMEАҙРЮёДЎЈФЪХвЦЦДЈКҪПВЈ¬ПсЛШФЪІ»Н¬өДКұҝМёР№вЈ¬Тт¶шФЪІЙјҜ¶ҜМ¬НјПсКұ»бІъЙъДЈәэЎЈ  ФЪН¬ІҪҝмГЕДЈКҪПВЈ¬ЛщУРПсЛШөД№в»э·ЦФЪН¬Т»КұҝМҪшРРөДЎЈЛщУРПсЛШН¬Кұұ»ёҙО»Ј¬ФЪҫӯ№э№в»э·ЦәуЈ¬ПсЛШөДЦөұ»ҙжҙўФЪГҝёцПсЛШөДҙжҙўҪЪөгЙПЈ¬И»әуЦрРРТАҙО¶БіцЎЈПсЛШөД№в»э·ЦәН¶БіцКЗҙ®РРөДЈ¬ФЪПсЛШ¶БіцКұЈ¬»э·Цұ»ҪыЦ№Ј¬Тт¶шҝЙТФұЬГвҫнБұҝмГЕЛщІъЙъөД¶ҜМ¬НјПсДЈәэөДОКМвЎЈҙЛНвЈ¬Н¬ІҪҝмГЕЦ§іЦ¶аРұВК»э·ЦЈ¬ҝЙ»сөГұИҫнБұҝмГЕёьёЯөД¶ҜМ¬·¶О§ЎЈ ЧЫЙП·ЦОцЈ¬ФЪК№УГХвҝоіЙПсЖчРҫЖ¬КұЈ¬¶ФҝмГЕ·ҪКҪТӘёщҫЭУҰУГөДіЎәПҪшРРСЎФсЈ¬ФЪ¶ФҝмЛЩФЛ¶ҜөДОпМеҪшРРІ¶»с»тТӘЗуУРёЯөД¶ҜМ¬·¶О§КұУҰСЎФсН¬ІҪҝмГЕЈ»¶шФЪ¶ФНјПсөДЦЎЛЩВКТӘЗуҪПёЯ»тТӘ¶ФНјПсҪшРРБ¬РшІЙјҜКұУҰСЎФсҫнБұҝмГЕЎЈ 2 »щУЪFPGAөДCMOSҝШЦЖКұРтөДЙијЖ 2Ј®1 ПЦіЎҝЙұаіМГЕХуБРFPGA ЛжЧЕјҜіЙөзВ·өД·ўХ№Ј¬ҙу№жДЈҝЙұаіМВЯјӯЖчјю№г·әУГУЪөзВ·ЙијЖБмУтЈ¬ЛьҫЯУР№ҰәДөНЈ¬ҝЙҝҝРФёЯөДМШөгЈ¬Н¬КұҙуҙујхРЎБЛөзВ·°еөДіЯҙзЎЈFPGAөДДЪІҝҪб№№ҫц¶ЁБЛFPGAФЪКұРтЙијЖ·ҪГжөДУЕФҪРФЎЈёГЙијЖСЎУГXilinx№«ЛҫөДSpartan3ПөБРFPGAРҫЖ¬XC3$50ЧчОӘУІјюЙијЖЖҪМЁЎЈSpar-tan3»щУЪVirtexўтFPGAјЬ№№Ј¬ІЙУГ90 nmјјКхЈ¬8ІгҪрКф№ӨТХЈ¬ДЪЗ¶УІәЛіЛ·ЁЖчәНКэЧЦКұЦУ№ЬАнДЈҝйЎЈҙУҪб№№ЙПҝҙЈ¬ЛьҪ«ВЯјӯЎўҙжҙўЖчЎўКэЧЦФЛЛгЎўКэЧЦҙҰАнЖчЎўIЈҜOТФј°ПөНі№ЬАнЧКФҙНкГАөШҪбәПФЪТ»ЖрЈ¬К№Ц®ҫЯУРёьёЯІгҙОЎўёь№г·әөДУҰУГЎЈ 2Ј®2 ҝШЦЖКұРтөДЙијЖ ёГЙијЖІЙУГVHDLУІјюГиКцУпСФЈ¬ёщҫЭЧФ¶ҘПтПВөДЙијЖ·Ҫ·ЁЈ¬Ҫ«КұРтҝШЦЖІҝ·Ц·ЦОӘИэёцДЈҝйЈәёҙО»ДЈҝйЎўјДҙжЖчЕдЦГДЈҝйәНҝмГЕДЈҝйЎЈУЙУЪјДҙжЖчУРБҪЦЦЕдЦГ·ҪКҪЈ¬ҝмГЕДЈКҪТІУРБҪЦЦЈ¬Тт¶шәуБҪІҝ·Ц¶јҝЙТФФЩПё·ЦОӘБҪёцРЎДЈҝйЎЈИэёцҙуөДДЈҝйУРСПёсөДПИәу№ШПөЈ¬ұШРлФЪЗ°Т»ДЈҝйТСНкіЙәуЈ¬ІЕҝЙҝӘКјәуТ»ДЈҝйЎЈНј4ПФКҫДЈҝйөД»®·Цј°Жд№ШПөЎЈ  ёҙО»ДЈҝйКЗУГАҙІъЙъНјПсҙ«ёРЖчЛщРиөДSYS_RE_SETРЕәЕЈ¬К№ҙ«ёРЖчХэіЈёҙО»Ј¬ДЪІҝјДҙжЖчЗеБгЈ¬ОӘјДҙжЖчөДЕдЦГЧцәГЧјұёЎЈ јДҙжЖчЕдЦГДЈҝйКЗУГАҙЕдЦГНјПсҙ«ёРЖчДЪІҝөД12ёцјДҙжЖчЈ¬Мṩҙ«ёРЖч№ӨЧчЛщРиөДІОКэәН·ҪКҪЎЈЖдЦРЈ¬ІОКэУР»э·ЦКұјдЎў»э·Ц·ҪКҪ(өҘРұВК»т¶аРұВК)ЎўXРтБР·ўЙъЖчөДКұЦУјдёфЎўSSРтБР·ўЙъЖчөДКұЦУјдёфЎўСЗІЙСщ·ҪКҪЎўҝӘҙ°О»ЦГј°ҙуРЎөИЎЈ ҝмГЕДЈҝйУГУЪІъЙъҙ«ёРЖч№ӨЧчЛщРиөДТ»Р©ҝШЦЖРЕәЕЈ¬Хл¶ФҝмГЕ·ҪКҪөДІ»Н¬ёшіцЛщРиөДКұРтҝШЦЖРЕәЕЎЈФЪН¬ІҪҝмГЕөДЙијЖЦРЈ¬ёГЙијЖІЙУГөҘРұВК»э·ЦЈ¬ФЪҙЛЙијЖ»щҙЎЙП¶аРұВК»э·ЦИЭТЧКөПЦЎЈ ёГЙијЖІЙУГVHDL¶ФёчДЈҝйКұРтҪшРРұаіМЎЈЖдЦРЈ¬ҝмГЕДЈҝйК№УГЧҙМ¬»ъАҙКөПЦёчЧҙМ¬Ц®јдөДЧӘ»»(Нј5ПФКҫБЛҫнБұДЈҝйөДЧҙМ¬ЧӘТЖНјЈ¬Нј6ПФКҫБЛН¬ІҪҝмГЕөДЧҙМ¬ЧӘТЖНј)ЎЈИ«ҫЦКұЦУәНADCКұЦУІЙУГDCMјҙКэЧЦКұЦУ№ЬАнөҘФӘАҙКөПЦЎЈ  3 КөСйҪб№ы 3Ј®1 ·ВХжҪб№ы КұРтҝШЦЖөзВ·ЙијЖНкұПәуЈ¬РиТӘ¶ФёчІҝ·ЦҪшРР№ҰДЬ·ВХжЎўВЯјӯЧЫәПТФј°ЧЫәПәу·ВХжЈ¬Чоәу¶ФХыёцПөНіҪшРРЧЫәПЎўІјҫЦІјПЯЈ¬НкіЙКұРт·ВХжЎЈ¶ФёчДЈҝйұаіМІў·ВХжНЁ№эәуЈ¬Ҫ«ёчДЈҝйјУФШөҪЦчәҜКэtopЦРЈ¬ІЙУГІўРРөДјДҙжЖчЕдЦГ·ҪКҪЈ¬¶ФҫнБұәНН¬ІҪБҪЦЦҝмГЕ·ҪКҪҪшРР·ВХжЈ¬ФЪModelsimЦРөД·ВХжҪб№ыИзНј7Ј¬Нј8ЛщКҫЎЈ  3Ј®2 іЙПсҪб№ы Ҫ«ҙЛЗэ¶ҜКұРтУҰУГУЪПа»ъПөНіЈ¬ФЪИ«ЦЎКдіцДЈКҪ(1 280ЎБ1 024)ПВЈ¬¶ФјшұрВК°РәНҫІОпҪшРРЕДЙгЈ¬КөСйҪб№ыИзНј9Ј¬Нј10ЛщКҫЎЈУЙЛщЕДЙгҪб№ыҝЙТФҝҙіцЈ¬НјПсЗеОъОИ¶ЁЈ¬ОЮГчПФұдРОЈ¬CMOSНјПсҙ«ёРЖчВъЧгБЛіЙПсөДРиЗуЎЈ  4 ҪбУп НјПсҙ«ёРЖчЗэ¶ҜКұРтөДХэИ·Ул·с¶ФЖдДЬ·сХэіЈ№ӨЧчЖрЧЕҫц¶ЁРФөДЧчУГЎЈұҫОДФЪ·ЦОцCMOSНјПсҙ«ёРЖчIBIS5-B-1300№ӨЧчКұРтөД»щҙЎЙПЈ¬ЙијЖБЛБҪЦЦјДҙжЖчЕдЦГ·Ҫ°ёәНБҪЦЦҝмГЕ·ҪКҪЈ¬ІўУГFPGAДЪЗ¶өДКэЧЦКұЦУ№ЬАнөҘФӘ(DCM)НкіЙБЛПөНіКұЦУәНACDКұЦУөДЙијЖЎЈКөСйҪб№ыұнГчЈ¬ЛщЙијЖөДЗэ¶ҜКұРтҝЙТФВъЧгёГНјПсҙ«ёРЖчөДЗэ¶ҜТӘЗуЎЈ |

НшУСЖАВЫ