高效率低谐波失真E类射频功率放大器的设计

发布时间:2010-10-26 10:22

发布者:analog_tech

|

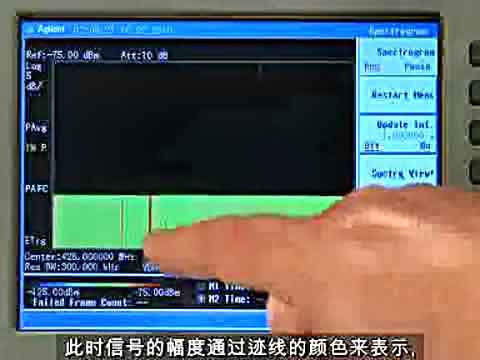

近年来,随着无线通讯的飞速发展,无线通信里的核心部分——无线收发器越来越要求更低的功耗、更高的效率以及更小的体积,而作为收发器中的最后一级,功率放大器所消耗的功率在收发器中已占到了60%~90%,严重影响了系统的性能。所以,设计一种高效低谐波失真的功率放大器对于提高收发器效率,降低电源损耗,提高系统性能都有十分重大的意义。 笔者采用了SiGe BiCMOS工艺实现了集成E类功率放大器,其工作频率为1.8GHz,工作电压为1.5V,输出功率为26dBm,并具有高效率和低谐波失真的特点,适用于FM/FSK等恒包络调制信号的功率放大。为了达到设计目标,该功率放大器采用了一些特殊的方法,包括采用两级放大结构,差分和互补型交叉耦合反馈结构。 E类功率放大器 E类功放工作原理 E类功率放大器的特点是将晶体管作开关管,相对于传统的将晶体管用作电流源的A、B、AB类功率放大器,具有更高的附加功率效率(PAE,power added efficiency)。 图1所示为理想E类功率放大器的原理图。其中,C为场效应管结电容和外接电容之和,ron为场效应管处于线性区时的漏源电阻。  图1 E类功放原理图 当输入电压大于阈值电压时,场效应管工作在线性区,相当于开关闭合,由于漏源间电阻ron很小,因此VD近似为0;而当输入电压小于阈值电压时,场效应管截止,相当于开关断开,ID为0。此时,C开始充电,引起VD增加,调谐网络从VD中滤出基波,传输到负载电阻上。当开关再次闭合时,有VD=0和dVD/dt =0,从而使得场效应管上的电压和电流不同时出现,消除了由于充放电带来的(1/2)CV2的损耗,晶体管理想效率达到100%。 除了高效率,E类功放还有一个优点就是功率可调节性,即在保证输出效率的同时能较大范围的调节输出功率。因为场效应管相当于开关,所以输入电压的幅值不会影响输出功率的大小。同样的,当场效应管处于三极管区时,漏源间的电阻ron上会有功率消耗PLOSS,这是E类功放的最主要功率损耗。由于PLOSS与VD2成正比,我们可以将漏极效率表示为:  (1) (1)其中,C为常数。这样,通过调节电压保证一定的输出功率,E类功放就能保持较高效率。 存在问题 E类功放同样也具有不少的局限性。例如,因为VD比VDD大上三倍左右,所以在设计的时候就必须考虑到击穿电压的影响,这样会使得输出的功率范围有很大的局限性。此外,为了减少ron带来的损耗,必须尽可能地增大宽长比,但是晶体管的面积越大,就会造成栅极的电容越大,使得在输入端需要更小的电感来进行耦合,这会对输入端信号提出更高的要求,很难通过BiCMOS工艺精确实现。而且大的栅漏电容会引起输出端到输入端的强反馈,这导致了输入和输出之间的耦合。最后,单端输出电路每个周期都要向地或者硅衬底泄放一次大的电流,这可能会引起衬底耦合电流的频率和输入、输出信号的频率相同,从而在输出端产生了错误的信号。 电路设计与改进 图2所示为两级差分结构的功率放大器,其中M5、M8为第一级差分结构功率放大器,负责对第二级功率放大器提供大的驱动电压;M1和M2组成第二级差分功率放大器,而M6、M7和M3、M4分别构成了一、二级的交叉耦合正反馈结构。  图2 两级差分耦合功率放大器 差分结构 图2所示的全差分结构能够解决衬底耦合的影响。由于在差分结构中,双端输出每个周期会向地泄放两次电流,由此使耦合电流的频率成为信号电流的两倍,这就消除了衬底耦合对信号的干扰。另外,在相同的电源电压下,当提供相同的输出功率时,全差分结构中流过每个开关管的电流要比单端输出小得多,所以在不增加开关损耗的前提下,可以使用尺寸更小的晶体管,从而减小对输入信号的要求。 LC振荡器 为了减小ron带来的损耗,并且提高开关速度,通常M1和M2的宽长比都会做得比较大,这样一来就会对输入端信号有更高的要求。 图2所示的功率放大器采用了模式锁定技术,即LC振荡器结构,不仅进一步降低了开关管的尺寸,而且加快了开关的转换速度。由M3、M4构成的振荡器中的交叉耦合部分,提供负阻来补偿电感L1、L2所引起的损耗,并对输入开关管引入正反馈。这样当LC振荡器工作在功率放大器的输入频率时,由于其输出端在M1和M2的漏极,会帮助输入开关管在尽可能短的时间完成“开”和“关”状态的变化,从而可以进一步减小输入开关管的尺寸。通过调节LC振荡器参数,使得输出端以输入频率发生振荡,从而加快开关管的开启和关闭速度,达到减小开关管宽长比的目的。 此外,相对于采用单端口输出结构的功率放大器,图2所示的交叉耦合结构的功率放大器,在实际应用中会得到更低的总谐波失真(THD)。因为采用了全差分结构,在输出端口会大幅度的削弱偶次谐波,所以在输出谐波中奇次谐波占主要地位。 仿真结果与分析 本电路采用0.35μm SiGe BiCMOS的工艺进行仿真,因为SiGe晶体管具有较高的截止频率,符合工作频率在1.8GHz的要求。此外,它与CMOS工艺有很好的兼容性,可以实现高集成度的芯片。 在Cadence上通过SpectreRF工具仿真后,得到输出功率和附加功率效率(PAE)随频率变化曲线(如图3所示)。当电源电压为1.5V,在1.8GHz时,PAE达到最大值45.4%,漏极效率也达到最大值的66.2%,此时的输出功率为26dBm。  图3 PAE和输出功率随频率变化曲线 由图4还可看出,偶次谐波在输出端中并不占主导地位,它被大大的削弱了,相比单端口功率放大器,该器件在谐波失真方面有较大的改善。当输入频率为1.8GHz,电源的输出电流如图5所示,通过计算可以得到电源的输出功率为595.5mW。图6所示为漏极电压VD经过调谐网络后保留下的基次波部分波形,由此可以计算得到负载(50Ω)上的功率为394mW。  图4 输出端谐波  图5 电源电流  图6 输出电压波形 |

网友评论