无功与谐波补偿装置信号采集及分析计算方案

发布时间:2010-10-25 18:47

发布者:analog_tech

|

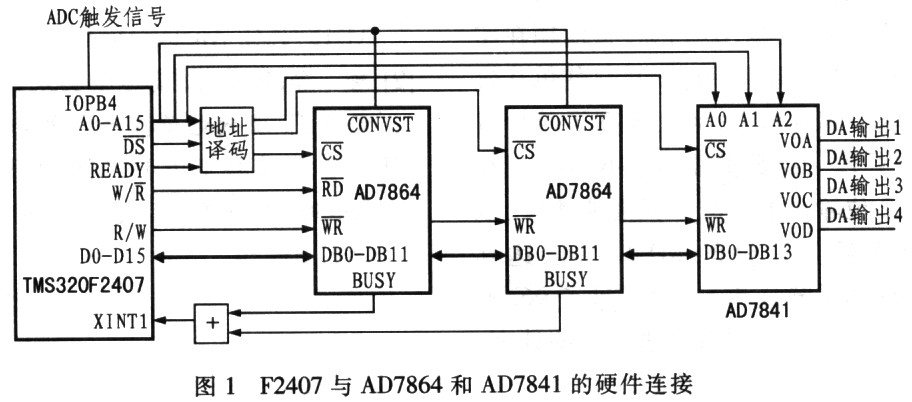

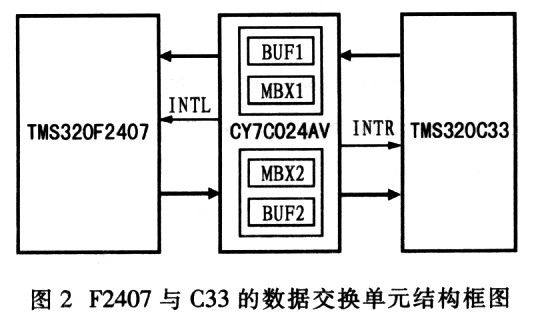

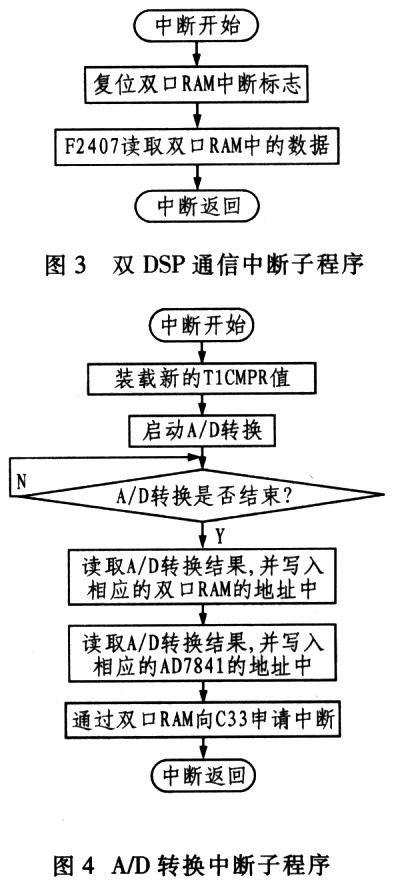

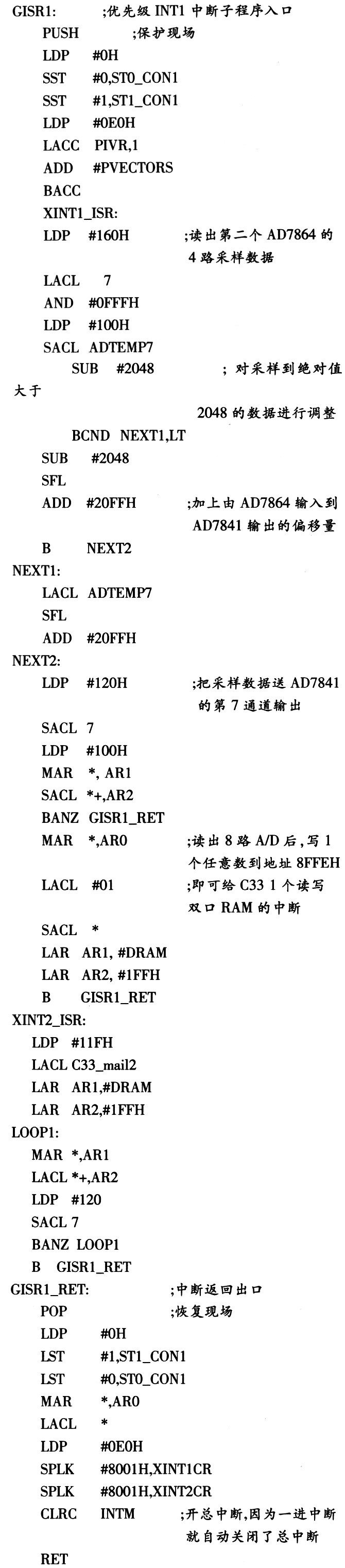

1 引言 随着电力电子装置的广泛应用,电网中的谐波污染日益严重。许多电力电子装置的功率因数很低,给电网带来额外负担并影响供电质量。因而,消除谐波污染和提高功率因数成为电力电子技术中的重要研究课题。现在可行的方案是设置无功与谐波补偿装置。在无功与谐波补偿装置中,需要对系统的三相电源电压、电流信号和负载电流信号进行实时检测、分析和计算;需要根据采集的电压、电流信号算出主电路的开关状态;需要对主电路进行实时控制以达到补偿的效果。笔者设计了一种信号采集及分析计算的方案,它由8通道A/D、D/A转换电路和分别用一个DSP来进行运算和控制的双DSP硬件电路、辅以相应的采样、A/D、D/A转换和数据交换程序来实现。 2 硬件电路组成及其工作原理 设计方案的硬件电路由AD7864型模,数转换器、AD7841型数/模转换器、CY7C024型双口RAM、TMS320F2407型和TMS320C33型(以下分别简称为F2407和C33)DSP组成。电路的总体工作过程为:A/D采样电路实时采集系统的三相电源电压、电流和负载电流信号,F2407根据软件计算出的时间间隔启动AD7864对所采集的信号进行模,数转换;然后,F2407通过双口RAM把转换后的数据传给C33,C33对接收到的数据进行运算并把计算出的补偿装置主电路的开关模式传给F2407,F2407根据接收到的开关模式控制主电路的开关状态。本文把电路的总体工作过程分为以下三部分进行详细的介绍。 2.1 AD7864对采集数据进行模/数转换 有源滤波器通过实时采集三相电源电压、电流和负载电流计算出指令电流。由于采用全数字化控制,算法比较复杂,而且对实时性、快速性和精确性有很高的要求,为了避免电流和电压采样时间不一致引起有功或无功测量误差,选用了2个AD7864对各相电压和电流同时采样。 AD7864是一款高速、低功耗、单电源、4路模拟输入同步采样、12位模,数转换器。它具有1个1.65μs的逐次逼近式A/D转换器、4路跟踪,保持放大器、2.5V参考电平、片上时钟振荡器、信号调整电路及1个高速并行接口。 AD7864可对4个通道的模拟输入信号同步采样,并将4个通道的采样信息保存下来。AD7864的转化启动信号从引脚CONVST输入,上升沿触发。当其有效时,跟踪,保持器被置为“保持”,同时按增序转换被选择的通道(通过软件或硬件选择)。EQC信号表明单个通道转换的结束,而BUSY信号表明被选择的所有通道转换的结束,二者都是低电平有效。 AD7864具有高速12位数据总线,能直接与16位DSP相连。AD7864与F2407的接口电路如图1所示。其工作过程是首先由F2407对电源电压频率实现数字锁相,产生ADC触发信号同时启动2个AD7864,然后AD7864分别对4个通道进行转换,完成后BUSY信号由高电平变为低电平,而后F2407产生中断并读取经AD7864转换的数据。  由于使用了2个AD7864,所以将2个BUSY信号通过1个或门接到F2407的外部中断口。当2个AD7864的8个通道都完成转换后,向F2407发出中断信号。F2407响应中断,先选中其中1个ADC,再连续执行4次读ADC操作,就可得到各个通道的采样值;然后对另1个ADC执行同样的操作,即可得到8个通道的同步采样数据。 2.2 AD7841对中间变量进行数/模转换 由于控制算法均由控制软件完成,各中间变量无法用示波器直接观测,而F2407内部没有DAC,因此选用AD7841作为系统的D/A输出单元,将中间变量转换为模拟信号输出,便于系统的调试和监控。 AD7841是Analog Devies公司生产的14位数据并行输入,4路模拟输出的D/A转换器。采用双电源15V供电,参考电压范围为-5V"十5V,输出电压范围为-10V"+10V。 按照分配给AD7841的I/O地址空间,通过A0、Al、A2选择数据寄存器输入数据,即可在相应的DAC通路上得到模拟输出。 2.3 F2407与C33通过双口RAM进行通信 本文所述的无功与谐波补偿装置的主控电路采用由F2407和C33构成的双DSP控制电路。C33的运算能力很强,但片内资源和对外I/O端口较少,逻辑处理能力也较弱,主要用于浮点计算和数据处理;而F2407正好相反,其片外接口资源丰富,I/O端口使用方便,但其精度和速度有一定限制,所以用于数据采集和过程控制。2个DSP通过双端口RAM完成数据交换。通过这2个DSP的互补结合,可充分发挥各自的优点,使控制系统达到最佳。 应用双DSP控制电路涉及双。DSP之间进行数据交换的问题,双DSP间的数据交换由双口RAM实现,图2为数据交换单元的结构框图。CY7C024具备的电路特点和存储特性简化了数据交换单元的电路设计及数据交换协议的实现。在系统设计中,对数据流向做了合理的安排,相应地在双口RAM中开辟了2个缓冲区BUFl和BUF2,其中BUF1作为F2407向C33传递数据的通道,BUF2作为C33向F2407传递数据的通道。  当F2407的数据需要向C33传递时,F2407将数据写入BUF2,然后向特定地址的信箱MBX2(对F2407,地址为Ox8FFE)写1个任意数,此时由CY7C024内部电路产生、1个中断信号INTL给C33;C33在检测到INTL信号时响应中断,从BUF2读出数据并访问MBX2清除中断信号。当C33处理完数据并需将结果传送给F2407时,将数据存入BUF1,然后再向信箱MBX1(对F2407,地址为0x8FFF)写1个任意数,此时产生中断信号INTR,引起F2407中断;F2407在检测到INTR信号时响应中断,从BUF1读出数据并访问MBX1,清除中断信号。 3 程序设计 与本设计方案的硬件电路对应的软件程序包括主程序、信号采集及A/D转换中断子程序、D/A转换中断子程序和双DSP通信中断子程序4部分。 双DSP通信中断子程序和数据采集及A/D转换中断子程序的软件流程如图3和图4所示。  A/D转换中断子程序如下:  4 结束语 理论分析与实验结果表明,本文介绍的数据采集及分析计算方案能够对三相电源电压、电流和负载电流进行实时准确的检测、分析和计算,从而为无功与谐波自动补偿装置主电路中的四象限变流器提供实时准确的开关信号,保证无功与谐波自动补偿装置的正常工作。 |

网友评论