ispPAC30在系统可编程模拟器件及其应用

发布时间:2010-10-20 23:46

发布者:conniede

|

1 引言 1992年美国Lattice 公司发明了在系统可编程技术(In-System Programmability), 彻底改变了传统数字电子系统的设计和实现方法,开创了数字系统设计的里程碑。1999 年Lat tice 公司又推出在系统可编程模拟电路(Programmability Pro gram ma ble Analog Circuits),翻开了模拟电路设计方法的新篇章,为电子设计自动化(EDA)技术的应用开拓了更广阔的前景。 与数字的在系统可编程大规模集成电路(ispLSI)一样,在系统可编程模拟器件 允许设计者使用开发软件在计算机中设计、 修改模拟电路,进行电路特性模拟, 最后通过编程电缆将设计方案下载至芯片中。当时仅推出了 ispPAC10、ispPAC20 两种器件,随后于2001年又推出了ispPAC80。2002年年初Lattice 公司又推出了两种新器件ispPAC30和ispPAC81,极大地丰富了在系统可编程器件的种类。本文仅就 ispPAC30的特点及应用作一介绍。 支持ispPAC30 的开发软件为 PAC Designer1.3,对计算机的软、硬件配置要求为:Win dows 95/98/ NT,16MB RAM,10MB硬盘,Pentium CPU。软件支持原理图输入方式,可模拟观测电路的幅频和相频特性。 2 器件的基本组成 ispPAC30主要由4个输入仪表放大器、2个输出放大器、2个可调的衰减D/A转换器(MDAC)、I/O布线池、求和布线池、配置存储器、2.5V参考电压和自校准等几部分组成,见图1。它有24脚 SOIC和28脚PDIP两种封装形式,有关引脚说明见表1。   3 器件的特点 ispPAC30 提供可编程、 多个单端或差分输入 方式,能设置精确的增益,具有补偿调整、滤 波和比较功能。除了E2CMOS或E2配置存储器外,它最主要的特性是能够通过SPI对器件进行实时动态重构。设计者可以无数次改变和重构ispPAC30, 用于放大器增益控制或其他需要动态改变电路参数的场合。 3.1 输入单元 任何输入引脚都可联接至四个输入仪表放大器(IA)、两个二选一选择器、MDAC或者联接到它们的组合。 输出放大器可以联接至所有输入单元。 因此, ispPAC30具有很大的灵活性,能方便地构成信号求和、级联增益块、复杂反馈电路等。直接接至输入引脚的输入信号范围为 0~2.8V。 当输入信号为TTL电平时可采用图2 所示的连接。 使 用差分输入时,信号可以是任意极性,只要最终 输出放大器的输出不低于0V。采用单端输入时, 把引脚Vin接地,IspPAC30的这种差分结构有利于消除共模干扰。四个输入放大器中的两个前端带有二选一选择器 。IA1,IA4的输入通道分别由外部 引脚 MSEL1和MSEL2 来控制。  3.2 内部参考电压 器件中含有两个独立的参考电压V REF1和VREF2,用以向四个输入仪表放大器和两个MDAC 提供固定的参考电压。每个VREF有7种不同的电平,并可独立编程。表2列出当VREF加至MDAC 的输入时,二进制加权值对应于最低有效位(LSB) 的关系。  3.3 MDAC 器件中有两个8 位的MDAC, 它接受参考输入信号:外部信号、内部信号、固定的直流电压(如内部的VREF)。MDAC 的功能是用一个值乘以(实际上是衰减)输入信号,这个值对应于DAC设置的码,使输出为输入信号的100%降至1LSB。它可提供分数增益、精确增益设置能力,与内部的 VREF 组合起来能提供精密的直流源。例如,输入信 号加至输入仪表放大器IA和MDAC,并组合成求和联接。于是输入仪表放大器的1至10的增益加上 MDAC 的分数增益就可形成 -11 至 +11 的任何增益,分解度大于0.01,总共可形成2500个增益值。 在实际应用时,可利用两个参考电压 VREF1、VREF2和 MDAC来提高分辨能力。图3例子中,VREF1 和MDAC1提供19.5mV的分辨能力(0~2.5V),V REF2和MDAC2提供0.5mV的分辨能力(+/-64mV),最终可达到0.5mV的分辨能力(0~2.56V)。  3.4 输出放大器 ispPAC30 有两个输出放大器(OA)。放大器的输出范围从0~5V。 输出放大器的输出端已在器件内部联接至输出引脚。 输出可以联接至任意一个输入仪表放大器 IA 或 MDAC 的输入。 每个OA都可配置成全带宽放大器、 低通滤波器、积分电路或者比较器。 3.5 断电模式 可通过将置为低电平,ispPAC30工作在断电模式。此时电流消耗仅有几微安,其模拟部分处于关闭状态,逻辑部分处于激活状态,模拟输出为高阻状态。除了整个器件可置为断电模式外,两个输出放大器可分别单独置为断电模式。 4 开发环境及应用 Lattice公司提供的PAC-Designer1.3软件,支持器件ispPAC30。其设计界面十分友好,用户可在用户图形界面GUI的原理图上进行设计输入,易学易用,还可在仿真窗口进行模拟仿真,设计者可同时查看最多4个输入输出组合的幅频、相频特性,并可用十字光标直接读取相应的增益和相位,使设计者可以确认设计是否符合设计要求。一旦设计被确认后,便可通过一条连结在PC机并行口与ispPAC30串行编程口之间的下载电缆将设计结果下载到器件中。连结接口符合IEEE1149.JTAG标准。 ispPAC30器件的上述特点,决定了它的广泛应用范围:精确的增益可编程放大器;可编程模拟信号控制环;A/D转换器模拟前端;可配置自适应信号控制。图4是ispPAC30的一个应用举例,它可获得微控制器所需的数字信号,并可实现闭环控制。 5 ispPAC系列器件比较 到目前为止,Lattice公司共推出了isp- PAC10、ispPAC20、ispPAC30、ispPAC80和ispPAC81五种在系统可编程模拟器件。ispPAC10 的差分输入输出结构及高增益性能,使它非常适合仪器、仪表测量;ispPAC20比ispPAC10少了两个PAC块,增加了一个8位DAC和两个差分可编程比较器,所以,它的增益可调范围比ispPAC10 小,但它可接收8位数字信号并将其转换为模拟信号;ispPAC80器件可使滤波器工作在很小的容差范围内,可用于实现五阶、连续时间、低通模拟滤波器。与ispPAC80器件极为相似的ispPAC81器件可实现更低频率(10~75kHz)的滤波器。 模拟电路的在系统可编程技术允许设计者使用开发软件在计算机中设计、修改模拟电路,并可通过编程电缆将设计方案下载到可编程模拟器件中,从而可加快设计进程,提高设计的准确性。 |

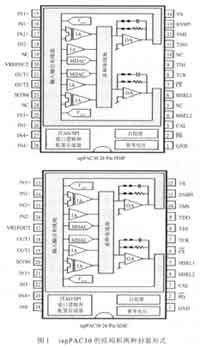

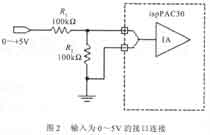

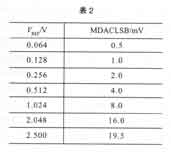

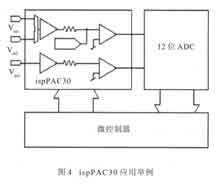

网友评论