一种减少VDMOS寄生电容的新结构

发布时间:2010-10-12 19:37

发布者:techshare

|

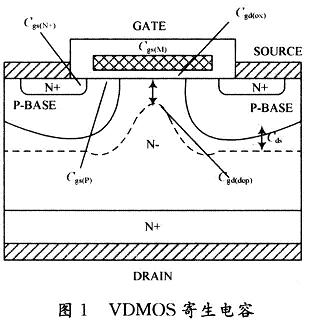

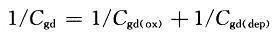

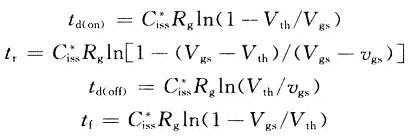

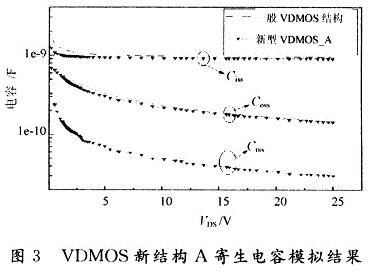

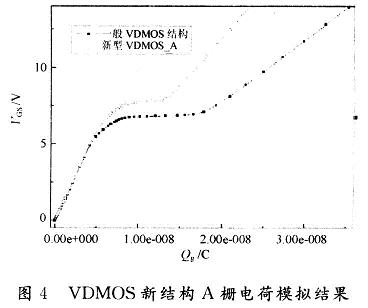

VDMOS与双极晶体管相比,它的开关速度快,开关损耗小,输入电阻高,驱动电流小,频率特性好,跨导高度线性等优点。特别值得指出的是,它具有负温度系数,没有双极功率管的二次击穿问题,安全工作区大。因此,不论是开关应用还是线性应用,VDMOS都是理想的功率器件。VDMOS的开关速度是在高频应用时的一个重要的参数,因此提出一种减小寄生电容的新型VDMOS结构。 1 基本原理 功率VDMOS的开关特性是由其本征电容和寄生电容来决定的。VDMOS的电容主要由三个部分栅源电容Cgs栅漏电容Cgd以及源漏电容Cds组成,如图1所示。电容的充放电是限制其开关速度的主要因素。栅源之间的电容是由三个部分组成,即: Cgs=Cgs(N+)+Cgs(P)+Cgs(M) Cgs(N+)是栅源交叠电容;Cgs(M)是栅与源金属间的电容;Cgs(P)是栅与P-base之间的电容。这三个电容的大小都是由VDMOS本身设计上的参数决定的,最主要取决于介质层的厚度。  栅漏之间的电容Cgd是两个电容的串联:  当栅压未达到阈值电压时,漂移区与P-base形成的耗尽层结合在一起,形成面积很大的耗尽层电容,栅下漂移区空间电荷耗尽区电容Cgd(dep)只是其中一部分,此时耗尽层宽度最大,耗尽电容最小。当栅压达到阈值电压后,器件开启时,漏区电势降低,耗尽层宽度减小,Cgd(dep)迅速增大。 漏源之间的电容Cds是一个PN结电容,它的大小是由器件在源漏之间所加的电压VDS所决定的。 一般VDMOS都包含了Cgs,Cgd和Cds,但是功率VDMOS都不是采用这三个电容作参考,而是采用Ciss,Coss和Crss作为评估VDMOS器件的电容性能,Ciss,Coss和Crss参数分别定义为:输入电容:Ciss=Cgs+Cgd输出电容:Coss=Cds+Cgd;反馈电容:Crss=Cgd。实际中采用Ciss,Coss和Crss作为衡量VDMOS器件频率特性的参数,它们并不是定值,而是随着其外部施加给器件本身的电压变化的。 VDMOS的开启延迟时间td(on)、上升时间tr、关断延迟时间td(off)、下降时间tf的关系式可分别表达为:  式中:Rg为开关测试电路中器件外接栅电阻;Vth为阈值电压;Vgs是外加栅源电压;vgs是使器件漏源电压下降到外加值10%时的栅源电压;Ciss*是器件的输入电容;在td(on)和td(off)式中:Ciss*=Cgs+Cgd;在tr和tf式中:Ciss*=Cgs+(1+k)Cgd(考虑密勒效应)。由上述关系式可见,Cgd直接影响器件的输入电容和开关时间,Cgd通过密勒效应使输入电容增大,从而使器件上升时间tr和下降tf时间变大,因此减小栅漏电容Cgd尤为重要。 2 新结构的提出 根据上面对VDMOS电容的分析,提出一种新的结构以减少器件的寄生电容。由分析可得出,栅下耗尽层的形状对VDMOS电容有较大影响,最主要影响Cgd。 图2中给出了新的VDMOS单元A,在VDMOSneck区域断开多晶硅条,同时在断开处注入一定的P型区,改变VDMOS栅下耗尽区的形状。这种新结构,在一定程度上加大耗尽区的宽度,从而减小Cgd。如图2结构中Pody下P-区注入区域为neck区中间3μm,注入能量是40 keV,注入剂量是1e13—3 cm,传统结构多晶硅栅完全覆盖P-body岛间漂移区,正是由多晶硅栅和漂移区的交叠形成的栅漏电容在充电时需大量电荷,导致器件开关损耗很大,新结构将多晶栅和漂移区的交叠部分移除,可以大大降低栅电荷,提高器件的动态性能。  3 新结构的模拟结果 图3给出了新型结构A的寄生电容模拟结果,从模拟结果来看,新型结构A增大了栅下耗尽区宽度,改变了栅下耗尽区的形状,减小了栅漏电容Cgd对输入电容、输出电容没有较大影响,在一定程度上减小了反馈电容。  栅电荷是比输入电容更有用的参数,从电路设计的角度,由Qg=Igt可得到使器件在理想开启时间内所需的栅电流值。栅电荷Qg是功率MOSFET两个最重要的参数之一(另一参数为Ron)。使用非零的Vds提供Qg-Vgs曲线已经成为一种工业标准。在曲线里包含五种信息:共源输入电容Ciss;共源反向传输电容Crss;使器件开启必须加在栅上的电荷量;得到器件理想开关速度所需的栅电荷;器件在开关期间所损耗的能量。 电源电路设计工程师使用这些信息设计驱动电路,并估汁器件性能。采用TCAD(ISE)对新型结构A进行了模拟,模拟结果如图4所示。  可以明显看出新型结构A的栅电荷明显比一般结构的栅电荷小很多,Qg定义为Vgs=12 V时栅上所存贮的电荷,新型结构A和一般VDMOS结构栅电荷分别为20.25 nC和30.57 nC,减小了33.67%。 4 结 语 本文提出一种减小VDMOS寄生电容,提高其动态特性的新结构。并用TCAD(ISE)软件对其模拟。从模拟分析结果可看出,新型结构A与传统VDMOS相比,能有效减小反馈电容及栅电荷,提高VDMOS器件的开关速度,提高器件的动态性能。 |

网友评论