ЛљгкSOPCЕФEDSL ModemЕФбажЦ

ЗЂВМЪБМфЃК2010-10-12 12:09

ЗЂВМепЃКeetech

|

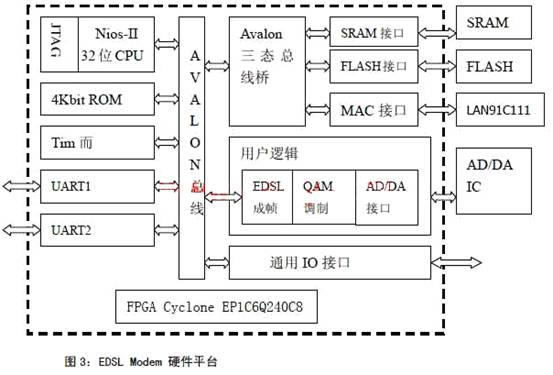

1 в§бд ФПЧАЃЌxDSLПэДјНгШыММЪѕГфЗжРћгУЯжгаЫЋНЪЯпзЪдДЃЌЮЊгУЛЇЬсЙЉЗЧЖдГЦИпЫйЭЈЕРЃЌгШЦфЪЧADSLММЪѕвбБЛШЫУЧЙуЮЊНгЪмЖјГЩЮЊПэДјНгШыММЪѕЕФжїСїЁЃШЛЖјЫцзХ IPНЛЛЛММЪѕЕФГЩЪьгыЗЂеЙЃЌжїИЩЭјжаНЛЛЛЗНЪННЋгЩ ATMж№ВНЯђIPНЛЛЛЗНЪНзЊЛЛЃЌвђДЫЛљгк ATMЕФADSLММЪѕвВШевцБэЯжГіЦфБОЩэЕФОжЯоадЁЃЛљгкДЫЃЌжаЙњаХЯЂВњвЕВПгы2003Фъ1дТЬсГіСЫЛљгкIPНЛЛЛЭјЕФEDSLММЪѕЃЌШЋГЦЮЊЛљгкЪБЗжЫЋЙЄЕФвдЬЋЪ§зжгУЛЇЯпЯЕЭГЃЈTDD based Ethernet Digital Subscriber Line SystemЃЈTDD-EDSLЃЉЃЉ,ЫќНсКЯСЫФПЧАЙуЮЊгІгУЕФСНДѓЭЈаХММЪѕ xDSLКЭEthernet ЕФОЋЛЊЃЌЪзДЮдкНгШыЭјЗЖГыФкЪЕЯжСЫIPАќЕФжБНгДЋЫЭ,жаМфЮоATMаХСюзЊЛЛЃЛВЩгУЪ§ОнЭЛЗЂММЪѕЃЌгІгУвдЬЋЭјХізВМьВтЛњжЦЃЌДјПэЖЏЬЌЗжХф,ЫйТЪИпДя 10Mbit/sЃЌЕкЖўДњEDSLММЪѕФмЪЕЯжжЧФмЦЕЦзЙмРэЃЌзюИпЫйТЪПЩДя100Mbit/sЃЛTDD-EDSLЪЕЯжIPЖЫЕНЖЫДЋЫЭЃЌДЋЪфОрРыГЄЃЌБъзМОрРыПЩЕН8kmЃЌЛЗТЗжЪСПНЯКУЪБПЩЕН 9kmЃЛДЋЪфаЇТЪИпЃЌЙІКФЕЭЃЛЭъЩЦЕФЭјЙмЯЕЭГЁЂСїСППижЦКЭЗўЮёжЪСППижЦЃЛЭъШЋЗћКЯ IEEE802.3 EthernetЁЂYD/T1254-2003 вдМАANSI TI 417 ЦЕЦзЙмРэБъзМЃЛАВзАМђБуЃЌгУЛЇЖЫМДВхМДгУЃЌЪЙгУ10/100/1000Mbit/sвдЬЋЭјНгПкЁЃ ЖРЬиЕФжЧФмЦЕЦзЙмРэММЪѕКЭЪБЗжЫЋЙЄФЃЪНЃЌДѓДѓМђЛЏСЫЯЕЭГНсЙЙЃЌЭЌЪБвВЫГгІСЫжїИЩЭјIPЛЏЕФЧїЪЦЁЃгыДЋЭГ xDSLММЪѕБШНЯЃЌЫќВЛНіПЫЗўСЫ xDSLММЪѕЕФаэЖрОжЯоадЃЈШчЖдЯпТЗЕФЬєЁЂДЎШХЕШЃЉЃЌВЂЧвдіДѓСЫДЋЪфОрРыЃЌЬсИпСЫДЋЪфаЇТЪЃЌEDSLЯЕЭГНсЙЙгыADSLРрЫЦЃЌЦфКЫаФВПЗжЪЧEDSL Modem. дкEDSLЪЕЯжжаЃЌБОЮФЬсГіСЫПЩАўЖсЪЕЪБФкКЫЕФЪЕЪБВйзїЯЕЭГІЬC/OS-IIКЭ32ЮЛОЋМђжИСюМЏШэКЫДІРэЦї NiosКЫЯрНсКЯЕФЗНЗЈ,ЙЙГЩвЛжжЛљгкПЩХфжУЕФШэКЫДІРэЦїЕФЧЖШыЪНПЊЗЂЦНЬЈЁЃИУЦНЬЈШэЁЂгВМўОљПЩАДеегУЛЇашЧѓНјааМєВУХфжУЃЌзюДѓГЬЖШЕиЬсЙЉСЫЯЕЭГЩшМЦЕФСщЛюадЃЌОпгаживЊЕФгІгУМлжЕЃЌБОЮФжиЕуНВЪіЛљгкSOPCЕФEDSL ModemЕФЪЕЯжЁЃ 2 EDSLЯЕЭГНсЙЙКЭавщеЛ EDSL ЕФжївЊММЪѕЬиЕуЃК(1)IPЖЫЕНЖЫЭјТчЃЛ(2)ВЩгУЪБЗжИДгУММЪѕЃЌЫЋЯђДјПэЖЏЬЌЗжХфЃЛ(3)ПЭЛЇЗўЮёЦїФЃЪНЃЌI P АќЮоХізВЛњжЦЃЛ(4)Ъ§ОнЭЛЗЂММЪѕЁЃе§ЪЧгЩгквдЩЯММЪѕЕФВЩгУЃЌЪЙЕУEDSLММЪѕВЛНіПЫЗўСЫxDSLММЪѕЕФаэЖрОжЯоадЃЌВЂЧвдіДѓСЫДЋЪфОрРыЃЌЬсИпСЫДЋЪфаЇТЪЁЃEDSLЕФЯЕЭГНсЙЙгыADSLРрЫЦЃЌгЩЮЛгкгУЛЇЖЫЕФEDSL Modem КЭ ОжЖЫЕФИпУмЖШНгШыИДгУЩшБИDSLAM(DSL Access Multiplexer)ЙЙГЩЃЌЦфНсЙЙ ШчЭМ1ЁЃ  EDSL ММЪѕЪЧЛљгк IPНЛЛЛЕФаТаЭПэДјНгШыММЪѕЃЌЫќНсКЯСЫвдЬЋЭјММЪѕКЭ xDSLММЪѕЕФгХЕуЃЌЮЊСЫГфЗжНЕЕЭгУЛЇЖЫЩшБИЕФИДдгадЃЌЪЙЯЕЭГвзгкЭГвЛЙмРэЃЌИУЯЕЭГВЩгУСЫПЭЛЇЗўЮёЦїФЃЪНЃЌМДгУЛЇЖЫЙЄзїдкПЭЛЇЖЫФЃЪНЃЌОжЖЫЩшБИДІгкЗўЮёЦїФЃЪНЃЌгЩОжЖЫЩшБИНјааЯпТЗЕФЦЕЦзЙмРэвдМАЫйТЪздЪЪгІЕїЪдЃЌЕУЕНЫЋНЪЯпжаЕБЧАЫљФмГаЪмЕФзюДѓЫйТЪвдМАзюМбЕїжЦЦЕТЪЕШВЮЪ§ЃЌЕБгУЛЇЖЫЕУ EDSLЩшБИНгЪеЕНАќКЌДЫРраХЯЂЕФаХЯЂжЁЪБЃЌИљОнНгЪеЕНЕФВЮЪ§ИќИФздЩэЕФВЮЪ§ЃЌДгЖјДяЕНзюМбЙЄзїзДЬЌЁЃетжжФЃЪНЯТЮоашгУЛЇНјааЩшжУМДПЩЗНБуЪЙгУЃЌДгЖјДѓДѓдіЧПСЫгУЛЇЕФвзгУадЁЃ гыЛљгкATMЕФADSLММЪѕЯрБШЃЌEDSLММЪѕгЕгаИќЮЊМђЕЅЕФавщНсЙЙ ЁЃШчЭМ2ЁЃ 3 гВМўЦНЬЈЕФЩшМЦ EDSL ModemгВМўЦНЬЈЕФДюНЈжївЊЪЙгУСЫ AlteraЙЋЫОЕФ FPGA Cyclone EP1C6Q240C8аОЦЌЃЌЫќгЕгаГфзуЕФПЩБрГЬТпМзЪдДФкЧЖ32ЮЛNios-IIШэКЫДІРэЦїРДЪЕЯжећИіПЩБрГЬЧЖШыЪНЯЕЭГЁЃЯЕЭГЕФжївЊЙІФмгЩFPGAЪЕЯжЃЌгВМўЕчТЗГ§ FPGAЭтжЛашМгЩЯДцДЂЦїМўЁЂвдЬЋЭјПижЦаОЦЌКЭЧАЖЫAD/DAзЊЛЛаОЦЌМДПЩЁЃБОЯЕЭГжївЊЪЙгУСЫвЛЦЌ 8M Byte Flash,вЛЦЌ16M Byte SDRAMЃЌвдМАвдЬЋЭјНгПкПижЦаОЦЌЕШзїЮЊFPGAЕФЭтЮЇЩшБИЃЌгВМўНсЙЙМђЕЅУїСЫЃЌМЋДѓЬсИпСЫЯЕЭГЕФПЩППадЁЃFPGAЯЕЭГдЫааЪБжгЮЊ50MHzЃЌГфЗжБЃжЄСЫЯЕЭГЕФдЫааЫйЖШЁЃ дкгВМўЦНЬЈЕФДюНЈжажївЊгУЕНСЫAlteraЙЋЫОЕФQuartus-IIгыSOPC BuilderШэМўЃЌЦфжа Quartus-IIФмНјааЯЕЭГМАИїТпМВПМўЕФЩшМЦЪфШыЁЂБрвыЁЂЗТецЁЂзлКЯЁЂВМОжВМЯпЃЌВЂНјааЮЛСїЮФМўЕФЯТдиКЭХфжУЮФМўЕФЩеТМЃЌвдМАЪЙгУЦЌФкТпМЗжЮівЧНјааЗжЮіКЭбщжЄЁЃ SOPC BuilderЧЖШыдкQuartus-IIПЊЗЂЯЕЭГФк,ЪЧвЛИіздЖЏЯЕЭГПЊЗЂЙЄОп,ФмЙЛздЖЏНјааЯЕЭГЖЈвх,ЭъГЩ SOPCПЊЗЂЕФМЏГЩЙ§ГЬЁЃдкSOPC Builder жабЁШЁЯЕЭГЫљашВПМў,ВЂздЖЏЩњГЩУПИіВПМўЕФЯЕЭГМЖHDLЮФМўвдМАжЇГжВПМўЫљашЕФШэМў,ШчЧ§ЖЏГЬађЁЂПтЮФМўКЭвЛаЉЪЕгУЕФгІгУГЬађЕШ,вдЙЉШэМўПЊЗЂдаЭгУЁЃ ЭЈЙ§SOPC BuilderШэМўАќПЩвдЖЈжЦ32ЮЛ Nios-IIШэКЫДІРэЦїКЭЛљБОЕФNios-IIЭтЩшФЃПщЃЌШч UARTПижЦЦїЃЌЖЈЪБЦїЃЌFLASHПижЦЦїЃЌ SDRAMжЦЦїЕШЁЃБОЮФЩшМЦЕФгВМўЦНЬЈНсЙЙШчЭМ3ЫљЪОЁЃ  ЭМ 3ЫљЪОащЯпПђФкгВМўВПЗжОљЪЧдк FPGAФкЪЕЯж ИУЯЕЭГЕФЧЖШыЪНДІРэЦї Nios-IIЪЧ Altera ЙЋЫОЭЦГіЕФвЛИігУЛЇПЩХфжУЕФ16 ЮЛЛђ32 ЮЛОЋМђжИСюМЏШэКЫДІРэЦїЁЃNios-IIДІРэЦїПЩвдХфжУГЩзюЖржЇГж 64ИіжаЖЯЃЌАќРЈЭтВПгВМўжаЖЯЁЂФкВПжаЖЯвдМА TRAP(ЕїЪджаЖЯ)ЁЃNios-II ДІРэЦїПЩвдХфжУЪЙгУ 32ЮЛФкВПЖЈЪБЦїЃЌЭЈЙ§ШэМўПижЦаДШыПижЦМФДцЦїЕФФкШнРДЛёЕУЖЈЪБЙЄзїЃЌгывЛАуЕФЖЈЪБЦїЙЄзїдРэЯрЭЌЃЌПЩвдВњЩњЖЈЪБжаЖЯЁЃ Nio-IIЧЖШыЪНЯЕЭГжаВЩгУ AvalonНЛЛЛЪНзмЯпдкДІРэЦїЁЂЭтЮЇЩшБИКЭНгПкЕчТЗжЎМфЪЕЯжЭјТчСЌНгЃЌВЂЬсЙЉИпДјПэЪ§ОнТЗОЖЁЂЖрТЗКЭЪЕЪБДІРэФмСІЁЃ AvalonНЛЛЛЪНзмЯпПЩвдЭЈЙ§ЕїгУ SOPC BuilderЩшМЦШэМўздЖЏЩњГЩ ЁЃ EDSL ModemЕФКЫаФВПЗжМДжїЪеЗЂЦїРћгУ FPGAжаЕФТпМЕЅдЊБраДздЖЈвхгУЛЇФЃПщЃЌВЂЩњГЩздЖЈвх IPКЫЃЌЭЈЙ§ AvalonзмЯпНгПкгыЧЖШыЪНДІРэЦїЯрСЌЁЃИУжїЪеЗЂЦїЙВАќРЈСЫСНИіВПЗжЃКEDSLГЩжЁФЃПщКЭ QAMЕїжЦФЃПщЁЃ дк SOPCЯЕЭГжаЃЌГ§СЫвдЩЯВПМўЃЌЛЙгаЦЌЩЯ ROMЁЂФкВПЖЈЪБЦїЁЂ UARTДЎааПкЁЂ SRAMЁЂ FlashЁЂвдМАвдЬЋЭјПижЦЦї LAN91c111НгПкЕШЯЕЭГВПМўНдгЩ SOPC builerздЖЏЩњГЩЁЃ 4 ШэМўЯЕЭГЕФЩшМЦ ШэМўЦНЬЈЕФПЊЗЂЪЧдк AlteraЙЋЫОЮЊ Nios-II ЯЕЭГЖЈжЦЕФ Nios-II IDEЯЕЭГЩЯеЙПЊЕФЃЌ Nios-II IDEЪЧЛљгк Eclipse IDEЕФМЏГЩПЊЗЂЛЗОГЃЌгУЛЇПЩвддк Nios-II IDEжаЮЊ Nios II ЯЕЭГПЊЗЂФЃПщЧ§ЖЏГЬађЁЂАхМЖжЇГжАќЃЈ BSPЃЉЃЌвдМАгУЛЇгІгУГЬађЁЃПМТЧЕН EDSL Modem ЕФЯЕЭГПижЦКЭИпЫйЪ§ОнДЋЪфЃЌдкИУЧЖШыЪНЦНЬЈжаЧЖШыСЫЪЕЪБЧЖШыЪНЯЕЭГ uC/OS-IIЃЌећИіЯЕЭГЕФШэМўЬхЯЕНсЙЙШчЭМ4ЃК  ЦфжаЮЛгк Nios-IIгВМўЦНЬЈжЎЩЯЕФЪЧ EDSL ModemИїВПМўЕФЧ§ЖЏГЬађЁЃЦфЩЯЪЧгВМўГщЯѓВуЃЈHALЃЉЃЌЫќЪЧЮЛгкгІгУГЬађКЭЯЕЭГгВМўжЎМфЕФвЛИіЯЕЭГПтЃЈ System LibraryЃЉЃЌдкШэМўПЊЗЂЪБПЩвдЗЧГЃЗНБуЕиЪЙгУетаЉЯЕЭГПтРДгыЕзВугВМўЭЈаХЃЌЖјЮоаыЙиаФЕФЕзВугВМўЪЕЯжЯИНкЁЃетбљдкЩЯВугІгУГЬађКЭЕзВугВМўжЎМфОЭЙЙГЩСЫУїЯдЕФНчЯоЃЌЕзВуЧ§ЖЏЕФаоИФВЛЛсЖдгІгУГЬађдьГЩШЮКЮгАЯьЁЃHAL APIЃЈApplication Program InterfaceЃЌгІгУГЬађНгПкЃЉМЏГЩСЫ ANSIC ЕФБъзМПтЃЌЫќдЪаэгІгУГЬађЪЙгУРрЫЦ CПтКЏЪ§ЕФЗНЪНЗУЮЪгВМўКЭЮФМўЁЃ ЪЕЪБЧЖШыЪНВйзїЯЕЭГ uC/OS-II ФкКЫЙЄзїдк HALЕФЖЅВПЃЌгаСЫ HALетвЛВуЃЌЛљгк uC/OS-IIЕФГЬађОпгаИќКУЕФПЩвЦжВадЃЌЖјЧвВЛЪмЕзВугВМўИФБфЕФгАЯьЁЃ ДЫЭтЃЌEDSL ModemЕФвдЬЋЭјНгПкЭЈаХжаЃЌжївЊдк uC/OS-IIжаЧЖШыСЫ LwIPавщЃЌLwIPВЛНіжЇГжвЛАуЕФЭјТчавщЃЌБШШч UDPавщЁЂDHCPавщЁЂPPPавщЕШЃЌЖјЧвЛЙжЇГжЖрЭјТчНгПкЁЂIPv6КЭБъзМ APIЁЃ 5 НсЪјгя БОЮФНщЩмСЫЮвЙњгЕгазджїжЊЪЖВњШЈЕФПэДјНгШыММЪѕЁЊЁЊ TDD-EDSLЃЌВЂзХжиНщЩмСЫЛљгк SOPCЕФ EDSL ModemЕФШэгВМўЪЕЯжЁЃдкЩЬгУ ASICВЂВЛЭъЩЦЕФЧщПіЯТЃЌБОЮФЪЙгУСЫШэгВМўОљПЩБрГЬЕФ Nios-IIЧЖШыЪНЯЕЭГЃЌЫѕЖЬСЫбаЗЂжмЦкЃЌНЕЕЭСЫбаЗЂГЩБОЁЃЭЌЪБ SOPCвВДњБэСЫвдКѓВњЦЗЩшМЦЕФЗЂеЙЗНЯђЃЌОпгаЛ§МЋЕФНшМјвтвхЁЃБОЮФЫљЩшМЦЕФ EDSL ModemИїВПЗжвбЭЈЙ§СЫШэМўЗТецКЭЪЕбщЯфПЊЗЂЦНЬЈбщжЄЁЃ 6 ДДаТЕу НЋШэгВМўОљПЩБрГЬЕФ Nios-IIЧЖШыЪНЯЕЭГгІгУЕНПэДјСьгђЯрЙиВњЦЗЕФбаЗЂЃЌДѓДѓЫѕЖЬСЫВњЦЗЕФбаЗЂГЩБОгыбаЗЂжмЦкЃЌБмУтСЫбаЗЂЙ§ГЬжаЖдГЩЪь ASICЕФЙ§ЗжвРРЕЁЃ |

ЭјгбЦРТл