SoC设计中的片上通信体系结构研究

发布时间:2010-10-12 12:07

发布者:eetech

|

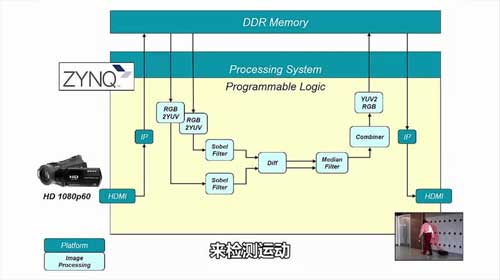

自20世纪70年代以来的大多数时间内,超大规模集成电路器件的特征尺寸以每三年70 9/6的速度缩小,从而使得数目越来越多的晶体管可以集成在同一颗半导体芯片上制造。由于具有速度、价格、面积、功耗和上市时间上的优势,基于IP核复用技术的SoC设计逐渐成为超大规模集成电路设计的一个重要领域,特别是SoC给无线通信、多媒体和消费类电子领域的设计提供了一个性价比更好的集成解决方案。而在SoC设计中,片上通信的研究是国内外SoC设计基础研究中的关键技术之一。 1 片上通信体系结构技术介绍 国内外片上通信体系结构的研究主要有五种:共享总线结构、片上网络结构、交叉开关、点到点通信和混合片上通信结构。 共享总线的互连方式可以分为:单总线、多总线和层次化总线。共享总线式的片上通信主要由公司开发并广泛应用于实际的SoC设计中,如IBM的CoreCon-nect总线互连框架、ARM公司的AMBA总线,以及其他一些公司的总线等,同时国内的高等院校也有对共享总线式的片上通信的研究,例如西安电子科技大学的科学基金项目“高性能SoC异步互连技术研究”,南京大学的科学基金项目“动态可重构SoC:中数据通信问题的研究”等。仲裁器是共享总线中的关键技术之一,现有的仲裁器的优先级策略包括静态优先级策略、时分多路优先级策略和基于随机数的彩票优先级策略的研究。尽管共享总线互连结构能够适合大量的应用并被采用,但是它也存在一些问题。首先SoC中具有各种各样的IP模块,每个模块都有各自的通信要求,而通常的单总线结构在同一时刻仅能授权一个发出请求的主设备占用共享总线,因此限制整个SoC的性能。同时,随着SoC的规模越来越大,总线结构的长互连问题、深亚微米技术下的串扰问题以及压降问题,都表现出来。 近几年,已有国内外学者提出采用计算机网络的互连通信技术进行SoC的片上网络设计与研究,这种片上网络结构能够极大提高多处理器SoC的性能。然而相当于共享总线结构来说,同时带来了较大的硬件和延迟开销。2002年Standford大学的De Micheli提出了采用将计算机网络互连技术使用到SoC设计中。他认为片上网络可以为SoC带来更高带宽的通信链路和易于扩展的节点,同时,采用该技术可以提高SoC的服务质量(QoS)。对于片上网络,现在的研究主要集中在片上网络(NOC)的结构、通信协议、高层次综合和设计自动化。近年来,多种基于报文交换网络的片上网络互连结构被提出,其中较多被研究的包括二维网格NoC、可扩展的可编程片上网络SPIN等。 基于交叉开关(Crossbar)的片上通信互连结构,包括单级交叉开关互连和多级交叉开关互连。文献[11]认为,在理论上对于多处理器的并行计算应用,采用交叉开关进行通信,其效率是最高的;然而,其实现的代价较大。对于一个具有N个节点的交叉开关,其实现复杂度和代价随着O(N2)增加。一个N×M的交叉开关网络,每个处理器可以读写不同的存储模块,所有处理器和存储模块可以并行通信。当两个或多个处理器请求访问同一模块是,仲裁机制会令一个处理器访问而其他处理器等待。近年来,随着集成电路制造的特征尺寸逐渐缩小,交叉开关互连结构在SoC中也得到了应用。 文献[12]中描述的NextJs SoC芯片,采用了一个具有16个端口的异步交叉开关互连方式,在130 nm工艺下,主频为1.35 GHz,等分封装带宽达780 Gb/s。点对点的片上通信互连结构是指各个IP核之间都有其专用的通信链路,相对于共享总线来说,具有独特的优点。例如点到点的通信容性负载相对较小,因此有较小的延迟。但是,由于每个IP核之间都有通信链路,其互连资源必然增多,造成布局布线的困难。每个IP核也需要更多的通信端口,增加了芯片的面积。文献[13]中,作者提出了一种基于功耗约束的点对点通信的综合算法。针对H.263应用的编码器,采用该算法进行综合,与传统共享现在的综合结果进行了比较,芯片上的面积开销虽然增大4%,但连线长度却减少了15%,芯片的功耗减小到原来的26%。 文献[14]提出了片上通信多样性概念,即采用不同片上通信结构的组合,把整个芯片分为几个孤岛,每个孤岛可能采用不同的电压和时钟频率,从而达到对系统具体参数优化的目的,如功耗、吞吐率。特别是近几年,片上通信网络的提出,使得片上通信网络的组合越来越丰富。利用上面提到的各种片上通信结构进行组合,可以充分发挥各种通信方式的优点,如总线方式的开销较小,且需要共享的数据传输性能高,而片上网络的方式可以增加数据传输的可靠性和并行性,具有高的通信带宽,因此,混合的片上通信结构为高性能的SoC设计提供了一种新的设计空间。 对片上通信的体系结构的研究,给SoC中性能优化的片上通信设计提供了一个探索空间。同时,片上通信系统的功耗、可靠性和带宽等具体性能参数的研究,对于片上通信的优化设计也具有重要意义。 2 一种新的片上通信体系结构 据市场预测,2010年全球市场SoC规模将超过IC总市场份额,因此作为SoC设计的关键技术之一的片上通信的研究与设计,具有重要意义。在国内外研究片上通信体系结构的基础上,提出一种将共享总线和片上网络相结合的混合片上通信结构。图1给出了一个2通道混合片上通信结构的示意图。该混合片上通信体系结构,传统的片上共享总线与片上网络相结合。这样,对于具有N个主从设备的IP核的SoC,经配置M个通道可以并行通信。 图1中的仲裁器用于对所有模块的通信申请和授权进行仲裁。这里提出了基于申请和授权的优先级模型。  仲裁序列:在SoC中存在N个主设备,记为M1,M2,…,Mi,…,MN(i=1,2,…,N),如果将第i次得到仲裁的主设备记为Xi,那么称序列{X1,X2,…,Xi,…}为仲裁序列。 仲裁周期序列段:如果仲裁周期为L(正整数),那么第i个仲裁周期序列段为:  Mi到Mj的授权转移:如果Xi为Mi,Xi+1为Mi,那么称{Xi,Xi+1}为Mi到Mj的授权转移。 授权模式:在第i个仲裁周期序列段{X(i-1)×L+1,X(i-1)×L+2,…,X(i-1)×L+L}(i=1,2,…)中,如果第j个主设备的授权次数记为nj(j=1,2,…,N),那么{n1,n2,…,nj,…,nN}称为第i个仲裁周期序列的授权模式。 由授权模式和仲裁周期的定义,可以得到:  通常,在某一运行时间段,SoC中的各个IP核的优先级将不同于另一个运行的时间段,因此,SoC中各个IP核优先级必然存在时间局域性。在此前提下,利用存储的第i个仲裁周期序列段中的授权模式,可以动态计算第i+1个仲裁周期序列段中的Xi×L+j=Mk(k=1,2,…,N)的机率和Mi~Mj的授权转移机率。 图1中,进行数据报文交换的是交叉开关。如果在SoC中仅有一个或两个DSP,该交叉开关可以有2M个端口;而如果存在一个处理器(DSP)阵列,则该交叉开关可以有2M+1个端口,以便于二维网格的扩展。图1中的MUX单元可以采用选通器,如图2所示。  目前已经完成对仲裁器、接口单元和片上交叉开关进行Verilog的RTL代码编写,在Cadence的仿真环境下进行了功能验证。下一步将针对TSMC的180 nm低功耗标准单元库进行逻辑综合,在Cadence的仿真环境下得到面积、功耗和主频等性能参数,并完成对上述片上通信结构后端的设计和评估。 3 结 语 经验证,该片上通信的优化体系结构既保留了片上共享总线的面积小的优点,又具有片上网络的并行通信的优点。目前,具有优化体系结构的片上通信IP核,已经应用于实际的SoC设计中。将来,该研究结果在我国已发展或将要发展的高清晰度数字电视处理器SoC芯片、3G无线移动终端基带SoC芯片和其他SoC芯片的设计中,都会具有重要的实际应用意义。 |

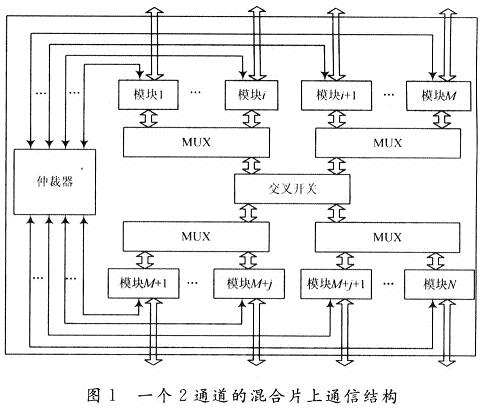

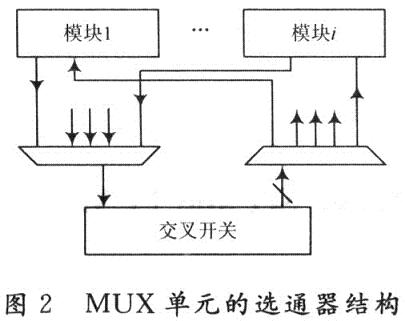

网友评论