FPGA I/O架构朝满足更高吞吐量要求的方向演进

发布时间:2010-10-9 10:15

发布者:eetech

|

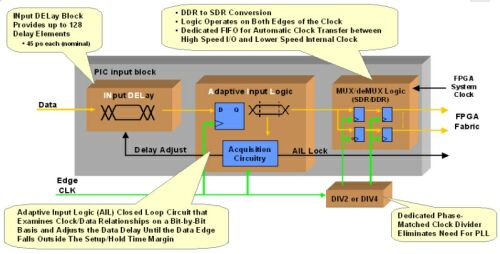

CPU 、ASIC和存储器的设计者为了使器件拥有尽可能高的通信带宽,他们在设计过程中充分利用I/O单元中的每一个晶体管来达到这个目标。这些器件常与FPGA相连接。因此,FPGA的设计者面临着一个不同以往的挑战:提供一个不仅能满足这些集成电路对互连带宽的要求,而且还能支持不同接口协议的可编程接口。 解决方案是可编程硬件I/O模块。这些可编程硬件模块位于FPGA的I/O路径内。硬件模块的传输单元将高速数据及相关的时序信号一起发送至接收器电路。这些模块中的接收单元拥有时序调整的功能,以便在很高的速度下能可靠地采集数据。此外,这些模块通过增加数据的宽度来减缓数据传输速率,从而使FPGA能够对这些数据进行处理。以下两个例子说明了FPGA的I/O结构的发展。 源同步接口 在源同步接口中,发送器芯片发送数据字和数据采样时钟至接收器。接收器芯片使用时钟来采集数据。从理论上说,源同步接口的速度是没有任何限制的。但是,随着数据速率的提高,由于数据相位偏移的差错,以及因工艺、电压和温度引起接收器内部延时的变化,导致数据采集出错。一些常见的源同步接口为SPI4.2、XGMII 、DDR SDRAM和串行LVDS ADC、DAC。 为了可靠地锁存输入至器件的数据,在FPGA内预先设计了源同步接口。针对中等性能的应用,可以通过匹配输入和数据路径做到。然而,对更高性能的接口,用算法弥补这些差错是很重要的。补偿这些差错有两个步骤。首先,器件在启动时,该算法补偿数据相位偏移和工艺的延时。其次,当开始正常的数据传输时,该算法监测和纠正由于电压和温度的变化而引起的时钟和数据相位关系的差错。而这些监测算法可以在FPGA内实现,以防止在高数据速率情况下数据采集出错,这些算法已经在FPGA 的I/O中很好地实现了。 LatticeSC FPGA的I/O引脚中使用了一个可编程的硬件模块(图1),实时地监测和纠正数据和时钟的关系。因此,LatticeSC FPGA可以实现可靠的源同步接口,运行的数据传输速率可达2Gbps。为了使输入的数据速率与FPGA的运行速度相匹配,I/O引脚还提供了一个变速功能,可将进入FPGA的数据速率降低8倍。设计人员可用软件来配置这个硬件模块,以满足系统的性能需求,然后专注于处理数据的算法。  图1:LatticeSC I/O引脚中的2Gbps源同步数据接口。 3.125Gbps SERDES (串化器/解串器)通道 SERDES是一种高速串行接口,它已用于许多标准,诸如PCI-Express、XAUI、Serial Rapid I/O、Gigabit Ethernet和JESD204。首先,发送器将时钟编入数据,然后通过一对线路传输合成的串行位流。接收器电路通过时钟数据恢复(CDR)电路从数据中提取时钟,并使用恢复的时钟对数据解串。然后用相应的物理层协议,对解串后的数据解码,并细分为字。在发送并行的数据至FPGA之前,接收器还应当通过弹性缓冲器处理,以补偿提取的时钟和FPGA时钟之间的频率差异。在接收器和发送器中的逻辑速度应足够的快,以便处理3.125Gbps速率的数据。 通过使用一个可编程的硬件模块(图2),LatticeECP2M低成本FPGA 能够满足各种协议标准要求。硬件模块的高速模拟SERDES部分能够实现均衡,时钟提取,对高达3.125Gbps速率的数据进行串化和解串化处理。为了进行字边界识别,用缓冲方式使物理层协议和时钟速率相匹配,硬件模块包括一个可编程的物理编码子层(PCS)功能块。PCS功能块可以配置成实现协议的特殊数据提取/格式。由于设计这些可编程硬件模块旨在满足性能要求,设计人员可以颇有信心地在FPGA中实现更高层的协议逻辑。  图2:LatticeECP2 FPGA的 SERDES功能块。 为增加芯片至芯片连接的通道带宽,LatticeSC FPGA已经在I/O路径中加入了可编程的硬件模块。这些模块很容易使设计人员在FPGA中实现逻辑功能。为支持更高的数据率, LatticeECP2M器件中的SERDES模块进一步在硬件中实现一些高速协议功能。而FPGA内的结构则用来实现更高层的数据处理功能。 |

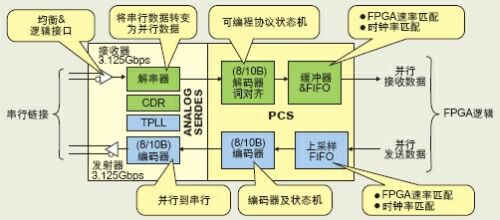

网友评论