ИпЫйЪ§зжЯЕЭГЕФДЎШХЮЪЬтЗжЮі

ЗЂВМЪБМфЃК2010-10-7 21:47

ЗЂВМепЃКeetech

|

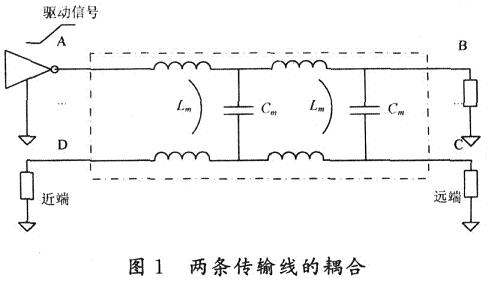

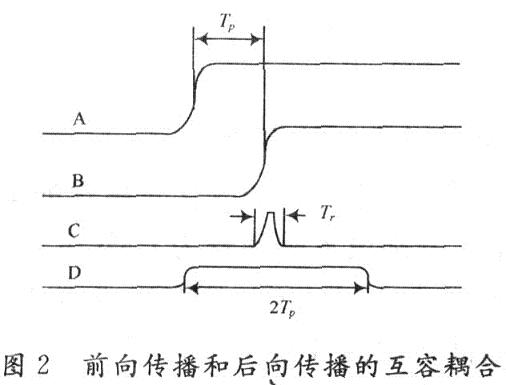

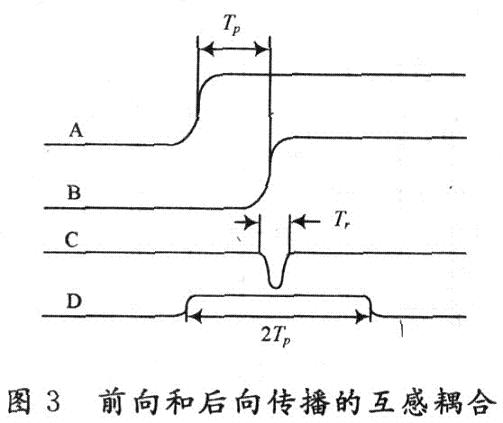

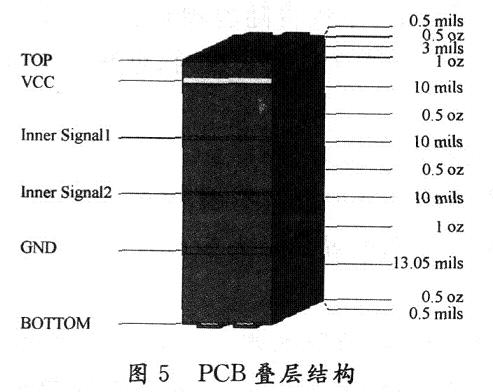

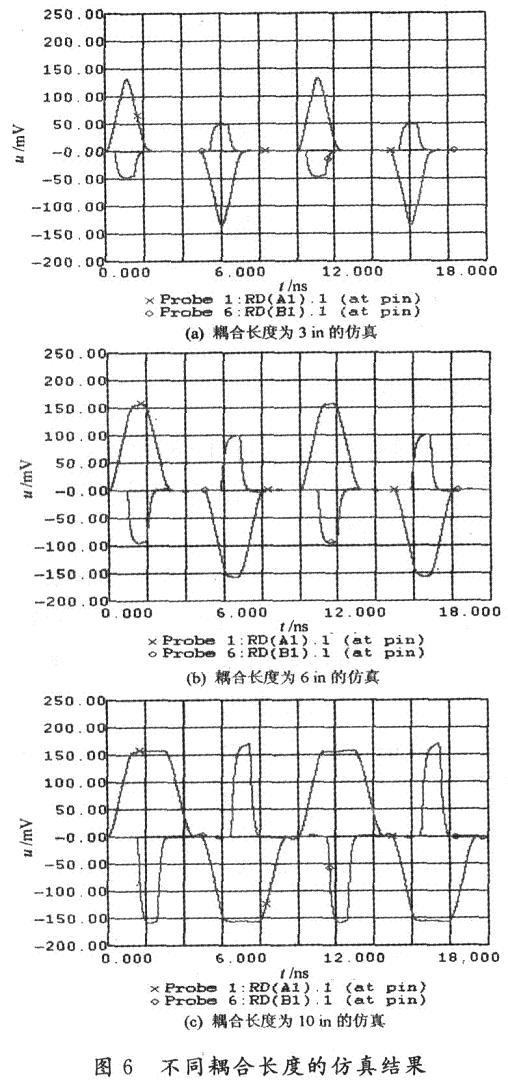

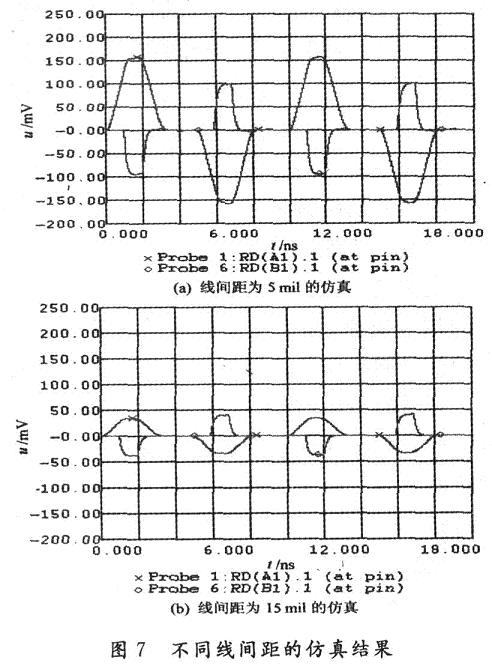

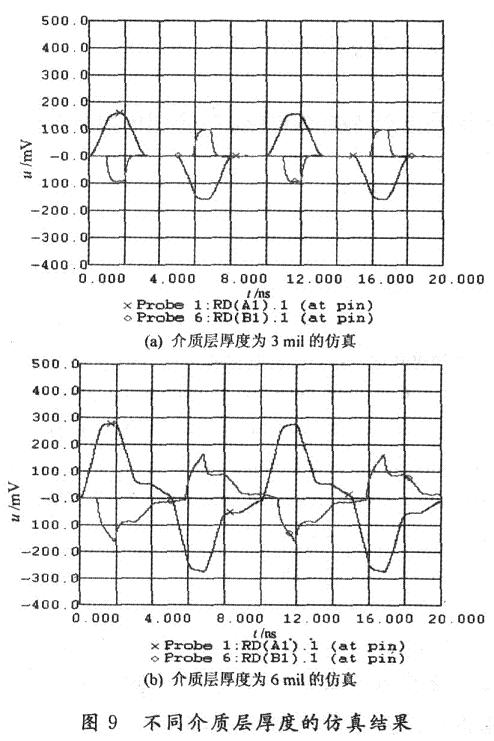

ЫцзХЕчзгММЪѕЕФВЛЖЯЗЂеЙЃЌдкИпЫйЕчТЗжааХКХЕФЦЕТЪЕФБфИпЁЂБпбиБфЖИЁЂЕчТЗАхЕФГпДчБфаЁЁЂВМЯпЕФУмЖШБфДѓЃЌетаЉвђЫиЪЙЕУдкИпЫйЪ§зжЕчТЗЕФЩшМЦжаЃЌаХКХЭъећадЮЪЬтдНРДдНЭЛГіЃЌЦфвбОГЩЮЊИпЫйЕчТЗЩшМЦЙЄГЬЪІВЛПЩБмУтЕФЮЪЬтЁЃДЎШХЪЧжИгаКІаХКХДгвЛИіЭјТчзЊвЦЕНСэвЛИіЭјТчЃЌЫќЪЧаХКХЭъећадЮЪЬтжавЛИіживЊЮЪЬтЃЌдкЪ§зжЩшМЦжаЦеБщДцдкЃЌгаПЩФмГіЯждкаОЦЌЁЂPCBАхЁЂСЌНгЦїЁЂаОЦЌЗтзАКЭСЌНгЦїЕчРТЕШЦїМўЩЯЁЃШчЙћДЎШХГЌЙ§вЛЖЈЕФЯоЖШОЭЛсв§Ц№ЕчТЗЕФЮѓДЅЗЂЃЌЕМжТЯЕЭГЮоЗЈе§ГЃЙЄзїЁЃвђДЫСЫНтДЎШХЮЪЬтВњЩњЕФЛњРэВЂеЦЮеНтОіДЎШХЕФЩшМЦЗНЗЈЃЌЖдгкЙЄГЬЪІРДЫЕЪЧЯрЕБживЊЕФЁЃ 1 ДЎШХЮЪЬтВњЩњЕФЛњРэ ДЎШХЪЧаХКХдкДЋЪфЯпЩЯДЋВЅЪБЃЌгЩгкЕчДХёюКЯЖјдкЯрСкЕФДЋЪфЯпЩЯВњЩњВЛЦкЭћЕФЕчбЙЛђЕчСїдыЩљИЩШХЃЌаХКХЯпЕФБпдЕГЁаЇгІЪЧЕМжТДЎШХВњЩњЕФИљБОдвђЁЃЮЊСЫБугкЗжЮіЃЌЯТУцНщЩмМИИігаЙиЕФИХФюЁЃШчЭМ1ЫљЪОЃЌМйЩшЮЛгкAЕуЕФЧ§ЖЏЦїЪЧИЩШХдДЃЌЖјЮЛгкDЕуЕФНгЪмЦїЮЊБЛИЩШХЖдЯѓЃЌФЧУДЧ§ЖЏЦїAЫљдкЕФДЋЪфЯпБЛГЦжЎЮЊИЩШХдДЭјТчЛђЧжКІЭјТч(Agreessor)ЃЌЯргІЕФНгЪеЦїDЫљдкЕФДЋЪфЯпЭјТчБЛГЦжЎЮЊОВЬЌЭјТчЛђЪмКІЭјТчЁЃОВЬЌЭјТчППНќИЩШХдДвЛЖЫЕФДЎШХГЦЮЊНќЖЫДЎШХ(вВГЦКѓЯђДЎШХ)ЃЌЖјдЖРыИЩШХдДвЛЖЫЕФДЎШХГЦЮЊдЖЖЫДЎШХ(ЛђГЦЧАЯђДЎШХ)ЁЃгЩгкВњЩњЕФдвђВЛЭЌНЋДЎШХПЩЗжЮЊШнадёюКЯДЎШХКЭИаадёюКЯДЎШХСНРрЁЃ  1ЃЎ1 ШнадёюКЯЛњжЦ ЕБИЩШХЯпЩЯгааХКХДЋЪфЪБЃЌгЩгкаХКХБпбиЕчбЙЕФБфЛЏЃЌдкаХКХБпбиИННќЕФЧјгђЃЌИЩШХЯпЩЯЕФЗжВМЕчШнЛсИагІГіЪББфЕФЕчГЁЃЌЖјЪмКІЯпДІгкетИіЕчГЁРяУцЃЌЫљвдБфЛЏЕФЕчГЁЛсдкЪмКІЯпЩЯВњЩњИагІЕчСїЁЃПЩвдАбаХКХЕФБпбиПДГЩЪЧбиИЩШХЯпвЦЖЏЕФЕчСїдДЃЌдкЫќвЦЖЏЕФЙ§ГЬжаЃЌЭЈЙ§ЕчШнёюКЯВЛЖЯЕидкЪмКІЯпЩЯВњЩњЕчСїдыЩљЁЃгЩгкдкЪмКІЯпЩЯУПИіЗНЯђЕФзшПЙЖМЪЧЯрЭЌЕФЃЌЫљвд50ЃЅЕФШнадёюКЯЕчСїСїЯђНќЖЫЖјСэ509ЃЏ6дђДЋЯђдЖЖЫЁЃДЫЭтЃЌШнадёюКЯЕчСїЕФСїЯђЖМЪЧДгаХКХТЗОЖЕНЗЕЛиТЗОЖЕФЃЌЫљвдЯђНќЖЫКЭдЖЖЫДЋВЅЕФёюКЯЕчСїЖМЪЧе§ЯђЕФЁЃЖдгкНќЖЫШнадёюКЯДЎШХЃЌЫцзХЧ§ЖЏЦїЪфГіаХКХГіЯжЩЯЩ§биТіГхЃЌСїЯђНќЖЫЕФЕчСїНЋДгСуПЊЪМбИЫйдіМгЃЌЕББпбиЪфШыСЫвЛИіБЅКЭГЄЖШвдКѓЃЌНќЖЫЕчСїНЋДяЕНвЛИіЙЬЖЈжЕЁЃСэЭтЃЌСїЯђНќЖЫЕФёюКЯЕчСїНЋвдКуЖЈЕФЫйЖШдДдДВЛЖЯЕиСїЯђНќЖЫЃЌЕБЩЯЩ§биЕНДяИЩШХЯпЕФНгЪеЖЫЃЌДЫЩЯЩ§биЛсБЛНгЪмЮќЪеЃЌВЛдйВњЩњёюКЯЕчСїаХКХЃЌЕЋЪЧЪмКІЯпЩЯЛЙгаКѓЯђЕчСїСїЯђЪмКІЯпЕФНќЖЫЃЌЫљвдНќЖЫЕФёюКЯЕчСїНЋГжајСНБЖЕФДЋЪфбгГйЁЃ ЖдгкдЖЖЫШнадёюКЯДЎШХЃЌгЩгкаХКХЕФБпбиПЩПДГЩЪЧвЦЖЏЕФЕчСїдДЃЌЫќНЋдкБпбиЕФИННќЧјгђВњЩњОЛЅШнСїНјЪмКІЯпЕФёюКЯЕчСїЃЌЖјВњЩњЕФёюКЯЕчСїНЋга50ЃЅгыИЩШХЯпЩЯЕФаХКХЭЌЯђЖјЧвЫйЖШЯрЭЌЕиСїШЫдЖЖЫЃЌвђДЫЫцзХИЩШХЯпЩЯаХКХЕФДЋЪфЃЌдкЪмКІЯпЩЯНЋВЛЖЯЕиВњЩњЕФЧАЯђёюКЯЕчСїЖјЧвКЭвбОДцдкЕФЧАЯђёюКЯЕчСїВЛЖЯЕиЕўМгЃЌВЂвЛЭЌДЋЯђдЖЖЫЁЃгЩгкДЎШХжЛдкаХКХЕФБпбиИННќЧјгђВњЩњЃЌСїЯђдЖЖЫЕФёюКЯЕчСїЕФГжајЪБМфЕШгкаХКХЕФдОБфЪБМфЁЃОпЬхЕФШнадёюКЯШчЭМ2ЫљЪОЁЃ  1ЃЎ2 ИаадёюКЯЛњжЦ ЕБаХКХдкгкШХЯпЩЯДЋВЅЪБЃЌгЩгкаХКХЕчСїЕФБфЛЏЃЌдкаХКХдОБфЕФИННќЧјгђЃЌЭЈЙ§ЗжВМЕчИаЕФзїгУНЋВњЩњЪББфЕФДХГЁЃЌБфЛЏЕФДХГЁдкЪмКІЯпЩЯНЋИагІГідыЩљЕчбЙЃЌНјЖјаЮГЩИаадЕФёюКЯЕчСїЃЌВЂЗжБ№ЯђНќЖЫКЭдЖЖЫДЋВЅЁЃгыШнадёюКЯЕчСїВЛвЛбљЕФЪЧЃЌИаадёюКЯЕчСїЕФЗНЯђгыИЩШХЯпЩЯаХКХДЋВЅЕФЗНЯђЪЧЗДЯђЕФЃЌЯђНќЖЫДЋЪфЪБЃЌЕчСїЛиТЗЪЧДгаХКХТЗОЖЕНЗЕЛиТЗОЖЃЌЖјЯђдЖЖЫДЋЪфЪБЃЌЕчСїЛиТЗдђЪЧДгЗЕЛиТЗОЖЕНаХКХТЗОЖЁЃ ЖдгкНќЖЫИаадёюКЯДЎШХЃЌЦфЬиеїгыНќЖЫШнадёюКЯДЎШХЗЧГЃЯрЫЦЃЌвВЪЧДгСуПЊЪМбИЫйдіМгЃЌЕБДЋЪфГЄЖШДѓгкЕШгкБЅКЭГЄЖШвдКѓЃЌНЋЮШЖЈдквЛИіЙЬЖЈжЕЃЌГжајЪБМфЪЧСНБЖЕФДЋЪфбгГйЁЃвђЮЊСїЯђНќЖЫЕФИаадёюКЯЕчСїгыШнадёюКЯЕчСїЭЌЯђЃЌЫљвдСНепНЋЕўМгдквЛЦ№ЁЃ ЖдгкдЖЖЫИаадёюКЯДЎШХЃЌИаадёюКЯдыЩљгыИЩШХЯпЩЯаХКХБпбиЕФДЋВЅЫйЖШЯрЭЌЃЌЖјЧвдкУПвЛВННЋЛсёюКЯГідНРДдНЖрЕФдыЩљЕчСїЃЌГжајЕФЪБМфЕШгкаХКХдОБфЕФЪБМфЁЃЕЋЪЧгЩгкЕчСїСїЯђгыдЖЖЫШнадёюКЯЕчСїЪЧЗДЯђЕФЃЌЫљвдЕНДяЪмКІЯпдЖЖЫНгЪеЦїЕФёюКЯЕчСїЪЧСНепжЎВюЁЃОпЬхЕФИаадёюКЯШчЭМ3ЫљЪОЁЃ  l.3 ЛЅИаКЭЛЅШнЕФЛьКЯаЇгІ вЛАуЕиЃЌдкЭъећЕФЕиЦНУцЩЯЃЌШнадКЭИаадЕФёюКЯВњЩњЕФДЎШХЕчбЙДѓаЁЯрЕШЃЌвђДЫдЖЖЫДЎШХЕФзмдыЩљгЩгкШнадКЭИаадёюКЯЕФМЋадВЛвЛбљЖјЯрЛЅЕжЯћЁЃдкДјзДЯпЕчТЗИќФмЙЛЯдЪОСНепжЎМфКмКУЕФЦНКтЃЌЦфдЖЖЫёюКЯЯЕЪ§МЋаЁЃЌЕЋЪЧЖдгкЮЂДјЯпТЗЃЌгЩгкгыДЎШХЯрЙиЕФЕчГЁДѓВПЗжДЉЙ§ЕФЪЧПеЦјЃЌЖјВЛЪЧЦфЫћЕФОјдЕВФСЯЃЌвђДЫШнадДЎШХБШИаадДЎШХаЁЃЌЕМжТЦфдЖЖЫДЎШХЯЕЪ§ЪЧвЛИіаЁЕФИКЪ§ЁЃ 2 ДЎШХЕФЗТецЗжЮі дкЪЕМЪЕФЩшМЦжаЃЌАхВуЬиад(ШчКёЖШЃЌНщжЪГЃЪ§ЕШ)вдМАЯпГЄЁЂЯпПэЁЂЯпОрЁЂаХКХЕФЩЯЩ§ЪБМфЕШЖМЛсЖдДЎШХгаЫљгАЯьЁЃЯТУцНсКЯЪЙгУMentor GraphieЙЋЫОЕФаХКХЭъећадЗТецШэМўHyperlynxЃЌЖдЩЯЪіЕФгАЯьДЎШХЕФвђЫиНјааЗжЮіЁЃЪзЯШдкHyperlynxжаНЈСЂСНЯпДЎШХЕФФЃаЭЃЌШчЭМ4ЫљЪОЃЌЩшСНЯпЕФЯпПэЮЊ5 milЃЌЯпГЄЮЊ6 inЃЌЯпОрЮЊ5 milЃЌСНЯпОљЮЊЖЅВуЮЂДјЯпЃЌЬиадзшПЙЮЊ49ЃЎ5ІИЃЌСНЯпЖМЖЫНг50ІИЕФЕчзшЃЌвдЯћГ§ЗДЩфЕФгАЯьЁЃИЩШХЯпЕФЧ§ЖЏЦїВЩгУCMOSЙЄвеЦїМўЕФIBISФЃаЭЃЌЕчбЙЮЊ3ЃЎ3 VЃЌЦЕТЪЮЊ100 MHzЁЃPCBЕФНщЕчГЃЪ§ЮЊ4ЃЎ3ЃЌСљВуАхЃЌЦфЕўВуНсЙЙШчЭМ5ЫљЪОЁЃ  2ЃЎ1 ёюКЯГЄЖШЖдДЎШХЕФгАЯь ИФБфСНЯпЕФёюКЯГЄЖШЃЌЗжБ№НЋёюКЯГЄЖШЩшжУЮЊ3 inЃЌ6 inЃЌ10 inЃЌЦфЫћЩшжУВЛБфЁЃ ЭМ6(a)ЪЧёюКЯГЄЖШЮЊ3 inЕФДЎШХВЈаЮЃЌЦфжаНќЖЫДЎШХЗхжЕЮЊ126ЃЎ34 mVЃЌдЖЖЫЮЊ43ЃЎ01 mVЃЛЭМ6(b)ЪЧёюКЯГЄЖШЮЊ6 inЕФДЎШХВЈаЮЃЌЦфНќЖЫДЎШХЗхжЕЮЊ153ЃЎ23 mVЃЌдЖЖЫЮЊ99ЃЎ46 mVЃЛЭМ6(c)ЪЧёюКЯГЄЖШЮЊ10 inЕФДЎШХВЈаЮЃЌЦфНќЖЫДЎШХЗхжЕЮЊ153ЃЎ23 mVЃЌдЖЖЫЮЊ163ЃЎ98 mVЁЃгЩДЫПЩМћЃЌЖдгкдЖЖЫДЎШХЗхжЕгыёюКЯГЄЖШГЩе§БШЃЌёюКЯГЄЖШдНГЄЃЌДЎШХдНДѓЃЛЖјЖдгкНќЖЫДЎШХЃЌЕБёюКЯГЄЖШаЁгкБЅКЭГЄЖШЪБЃЌДЎШХНЋЫцзХёюКЯГЄЖШЕФдіМгЖјдіМгЃЌЕЋЪЧЕБёюКЯГЄЖШДѓгкБЅКЭГЄЖШЪБЃЌНќЖЫДЎШХжЕНЋЮЊвЛИіЮШЖЈжЕЁЃ  2ЃЎ2 ЯпМфОрЖдДЎШХЕФгАЯь вдЯТЪЧБЃГжЦфЫћЩшжУВЛБфЃЌПМВьЯпМфОрЕФИФБфЖдДЎШХЕФгАЯьЁЃЗжБ№ЩшжУЯпОрЮЊ5 milЃЌ15 milЃЌЗТецВЈаЮШчЭМ7ЫљЪОЁЃ  гЩЭМ7ПЩжЊЃЌЕБЯпМфОрЮЊ5 milЪБЃЌНќЖЮДЎШХЗхжЕЮЊ153ЃЎ23 mVЃЌдЖЖЫЮЊ99ЃЎ46 mVЃЛЖјЯпМфОрЮЊ15 milЪБЃЌНќЖЫДЎШХЗхжЕЮЊ33ЃЎ40 mVЃЌдЖЖЫЮЊ40ЃЎ49 mVЁЃПЩМћЫцзХЯпМфОрЕФдіДѓЃЌЮоТлЪЧНќЖЫЛЙЪЧдЖЖЫДЎШХЖМНЋМѕаЁЃЌЕБЯпМфОрДѓгкЕШгкЯпПэЕФ3БЖЪБЃЌДЎШХвбОКмаЁЁЃ 2ЃЎ3 ЩЯЩ§ЪБМфЖдДЎШХЕФгАЯь ЯТУцПМВьЩЯЩ§биЪБМфЕФБфЛЏЖдДЎШХЕФгАЯьЃЌЦфЫћЩшжУБЃГжВЛБфЁЃЗжБ№ЩшжУЧ§ЖЏЦїЮЊCMOS 3ЃЎ3 V MEDIЁЊUMЃЛCMOS 3ЃЎ3 V FASTЃЛCMOS 3ЃЎ3 V ULTRAЁЊFASTЃЌЗТецВЈаЮШчЭМ8ЫљЪОЁЃ  ЭМ8(a)жаЕФНќЖЫДЎШХЗхжЕЮЊ153ЃЎ9 mVЃЌдЖЖЫДЎШХЮЊ46ЃЎ3 mVЃЛЭМ8(b)жаНќЖЫДЎШХЗхжЕЮЊ153ЃЎ2 mVЃЌдЖЖЫДЎШХЮЊ99ЃЎ5 mVЃЛЭМ8(c)жаНќЖЮДЎШХЗхжЕЮЊ153ЃЎ2 mVЃЌдЖЖЫДЎШХЮЊ349ЃЎ9 mVЁЃПЩМћЃЌЕБЩЯЩ§биЪБМфЫѕЖЬЪБЃЌдЖЖЫДЎШХдыЩљдНРДдНДѓЁЃЖдгкНќЖЫДЎШХРДЫЕЃЌШчЙћгыДЋЪфЯпЕФЪБбгЯрБШЃЌЩЯЩ§ЪБМфНЯЖЬЃЌдђНќЖЫДЎШХгыЩЯЩ§ЪБМфЮоЙиЃЛЖјШчЙћгыДЋЪфЯпЪБГйЯрБШЃЌЩЯЩ§ЪБМфНЯГЄЃЌдђНќЖЫДЎШХдыЩљгыЩЯЩ§ЪБМфгаЙи(ЫцзХЩЯЩ§биЪБМфЕФМѕаЁЃЌНќЖЫДЎШХБфДѓ)ЁЃ 2ЃЎ4 НщжЪВуКёЖШЖдДЎШХЕФгАЯь дкPCBЕФЕўВуБрМЦїжаНЋНщжЪВуКёЖШЗжБ№ЩшжУЮЊ3 milКЭ6 milЃЌЦфЫћЩшжУВЛБфЃЌЗТецВЈаЮШчЭМ9ЫљЪОЁЃ  ПМВьвдЩЯЕФЗТецВЈаЮПЩжЊЃЌЕБНщжЪВуКёЖШЮЊ3 milЪБЃЌНќЖЫДЎШХЗхжЕЮЊ153ЃЎ2 mVЃЌдЖЖЫДЎШХЮЊ99ЃЎ5 mVЃЛЕБНщжЪВуКёЖШЮЊ6 milЪБЃЌНќЖЫДЎШХЗхжЕЮЊ277ЃЎ3 mVЃЌдЖЖЫДЎШХЮЊ163ЃЎ9 mVЁЃПЩМћЃЌЫцзХНщжЪВуКёЖШЕФМѕаЁЃЌДЎШХвВНЋБфаЁЁЃ 3 НтОіДЎШХЕФЗНЗЈ ДЎШХдкЕчзгВњЦЗЕФЩшМЦжаЦеБщДцдкЃЌЭЈЙ§вдЩЯЕФЗжЮігыЗТецЃЌСЫНтСЫДЎШХЕФЬиадЃЌзмНсГівдЯТМѕЩйДЎШХЕФЗНЗЈЃК (1)дкЧщПідЪаэЕФЧщПіЯТЃЌОЁСПдіДѓзпЯпжЎМфЕФОрРыЃЌМѕаЁЦНаазпЯпЕФГЄЖШЃЌБивЊЪБВЩгУjogЗНЪНзпЯпЁЃ (2)дкШЗБЃаХКХЪБађЕФЧщПіЯТЃЌОЁПЩФмЕибЁдёЩЯЩ§биКЭЯТНЕбиЫйЖШИќТ§ЕФЦїМўЃЌЪЙЕчГЁКЭДХГЁБфЛЏЕФЫйЖШБфТ§ЃЌДгЖјНЕЕЭДЎШХЁЃ (3)дкЩшМЦзпЯпЪБЃЌгІИУОЁСПЪЙЕМЬхППНќЕиЦНУцЛђЕчдДЦНУцЁЃетбљПЩвдЪЙаХКХТЗОЖгыЕиЦНУцНєУмЕФёюКЯЃЌМѕЩйЖдЯрСкаХКХЯпЕФИЩШХЁЃ (4)дкВМЯпПеМфдЪаэЕФЬѕМўЯТЃЌдкДЎШХНЯбЯжиЕФСНЬѕаХКХЯпжЎМфВхШывЛЬѕЕиЯпЃЌПЩвдМѕаЁСНЬѕаХКХЯпМфЕФёюКЯЃЌНјЖјМѕаЁДЎШХЁЃ 4 Нс гя ДЎШХЪЧаХКХЭъећаджаЕФживЊФкШнЃЌгАЯьЯЕЭГЕФЪБађЁЂНЕЕЭдыЩљШнЯоЃЌЕМжТЯЕЭГЮоЗЈе§ГЃЕФЙЄзїЁЃНщЩмСЫИпЫйЕчТЗжаДЎШХВњЩњЕФЛњРэЃЌВЂЭЈЙ§ЗТецЖдДЎШХНјааЗжЮіЃЌЕУГіДЎШХЕФДѓаЁгыгАЯьДЎШХЯрЙивђЫиЕФЙиЯЕЃЌдкДЫЛљДЁЩЯЬсГіСЫвЛаЉМѕаЁДЎШХЕФЗНЗЈЃЌЖдгкдкИпЫйИпУмЖШЕФЕчТЗЩшМЦжаНтОіДЎШХЮЪЬтгавЛЖЈЕФжИЕМвтвхЁЃ |

ЭјгбЦРТл