ASIC或FPGA :为什么不考虑可移植性?

发布时间:2010-10-7 21:17

发布者:eetech

|

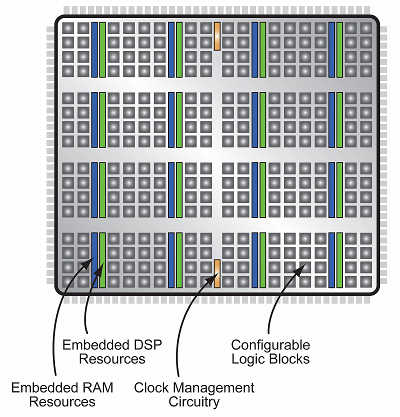

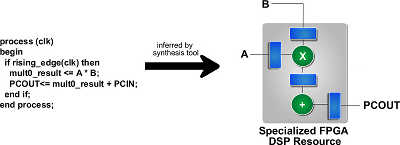

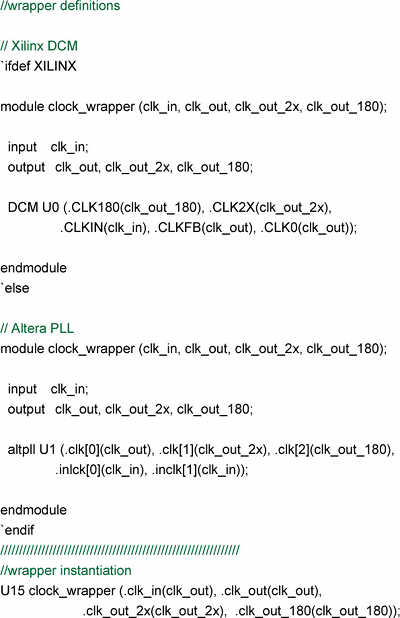

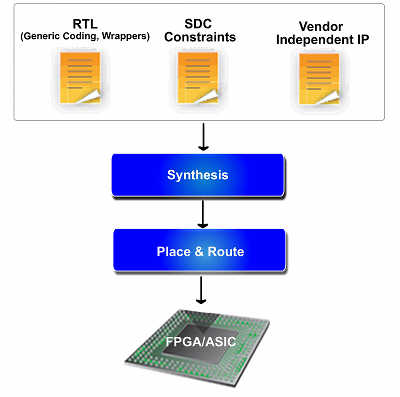

成功的关键在于灵活性,灵活性的关键是利用目标独立性的设计方法,让自己在将来的建设性变更中有选择的余地。 一般而言,某一特定FPGA器件选择不仅为它的逻辑功能,而且还因为FPGA一般能够解决现实中小批量的生产和后期周期设计变更。 但是,在产品需求或市场动态变化时可以迅速重新评价这种选择。有时可能有必要切换到一个完全不同的FPGA系列,例如能够提供规模优势或卓越的性能的FPGA系列。有时ASIC的是一个更好的选择,因为它适合于大批量定制。 成功的关键在于灵活性,灵活性的关键是利用目标独立性的设计方法。如若有一种设计方法类似ASIC或结构化ASIC允许适宜移植,使得从一个FPGA架构迁移到另一个FPGA架构变得更加容易。 利用目标独立性的设计方法,让自己在将来的建设性变更中有选择的余地。 并非所有的制约因素都是平等的 确定时间限制几乎跟RTL级本身的描述设计一样重要,而且代码一样很复杂。没有比被供应商专有的语法限制更令人沮丧的了,特别是存在同行业公认的方法。专有的约束语法可能是供应商的战略,以“锁定”客户,也可以是用于严格的技术原因。在这两种情况下,如果该项目要求时,转移到ASIC的努力变得复杂。 在ASIC世界里,事实上的标准时间是Synopsys公司的设计约束( SDC )格式。领先的FPGA综合工具通过这个语法促进从ASIC设计到FPGA实现的移植(或者用于生产或原型),或相反,从FPGA到ASIC的移植。 转换SDC约束语法不仅仅是在文本文件里行使一个查找/替换,它可以繁琐本身。某一专有语法缺乏明确的翻译往往会带来很多限制。专有语法同样难以往相反的方向翻译。 还值得指出,当一个FPGA供应商使用自己的语言进行时间约束,此语法最终必须联合布局布线。 FPGA厂商有那部分流程,但没有办法解决它。但是有一个先进的合成工具,可以把任何引进或产生SDC文件译成供应商的格式,并将其布局布线。通过这种方式,用户可以在行业标准前面附上合成流程管理的文件格式。 这种方法用在ASIC和FPGA之间的移植非常行之有效,因为FPGA合成流程基本上是借鉴ASIC世界的约束格式。 一般思考,在FPGA的平台,许多设计都是结合独立的RTL技术 (Verilog , SystemVerilog或VHDL )和分区实例化技术来实现的。尽管不建议采用后一种办法,并最好保持在最低限度使用。 设计师有一个选择:要么具体实例某些分区技术,要么用合成工具在通用编码准则的基础上自动推断出该功能。分区技术是指基元成分,如多路复用器,缓冲器,存储器,乘法器,或DSP模块。要获得这些基元取决于FPGA。图1显示传统的FPGA架构,包括块标准逻辑可配置逻辑、芯片存储器和DSP功能的嵌入式区,时钟管理电路。  图1 标准FPGA架构 实例的基元成分允许用户能够控制并实现自己的设计,但前提是需要遵循目标架构的规则。例如,实例化一个赛灵思特定DSP的分区意味着不同的实例来重新编码该部分的HDL文件,并详细了解该架构是否必要转移到一个不同的平台等细节。 推荐使用的另一种办法是,写一般的RTL并让合成工具推断出适当的FPGA实现。如果有必要(或可取)迁移到一个新的目标架构,在RTL一般保持不变,而合成工具会处理新的实现。图2中的代码描述一个简单的乘数累加器通过合成工具推断到目标FPGA器件中的专门DSP模块。  图2 RTL通过合成工具推断到DSP 通用RTL编码这一概念并不是一个新问题。事实上,这种方法普遍受到推崇,因为它使得从一个FPGA系列移植到另一系列得到了简化,例如从一个赛灵思系列到一个Altera 系列。 重要的是,通用RTL编码方法也同样有利于FPGA和ASIC之间的移植。ASIC的合成流程可以解析通用的RTL,这意味着RTL变化需要不是很大时可以遵守通用编码准则。 包装带移植到专门职能 但并非所有功能都可以在通用的RTL得到定义 。数字时钟管理是一个明显的例外。设计中的成倍增加时钟速率或改变时钟阶段的任务最好通过由DLLs或PLLs (锁相环或延迟锁定回路)制成的FPGA芯片。这样做通常是用实例化技术而不是通用RTL 。 专门的I / O单元是只实例化元件的另一个例子。这些IP模块是通过设计高层对其中一个文件做任何修改,并根据包装和编译指示选择适当的代码,以便达到最好的管理。如图3所示,该包装模块可用作其余RTL专门资源的接口。这样,从赛灵思的DCM转换到Altera的PLL需要特定的合成命令水平。  图3包装模块使用环绕时钟管理电路 另一方面,内存在整个设计中最容易,不仅仅因为它在最高层。通过在特定技术内存实例中增加一个通用包装模块,然后将这些特定技术内存实例保存在一个单独的文件中,设计者只需要两个版本的内存档案——各自的技术。在编译的时候,只有与技术指标相匹配的内存文件才被使用,该设计进行的是无缝编译。 需注意的是,通用包装模块需要知道具体的内存大小,而不是传统的设想FPGA大小。例如,要一个设计模块,需要有一个512 × 16个单口RAM 。进一步试想设计师希望实现一个内存为512 × 16 1PS RAM的ASIC和一个18 kb的RAM的FPGA 。RTL模块设计需要调用一个512 × 16单口RAM的内存实例。在ASIC特定内存文件,这是匹配到ASIC内存汇编的具体规模。在FPGA特定内存文件,一般情况接到FPGA特定RAM块。只有包含正确的内存文件,设计的每个技术才能正确编译。 诚然,必须为新的目标作准备。但该方法只是概括,使我们能够为多个目标设计保持HDL源。 这里描述的逻辑功能被认为是“基础”IP ,因为其中许多被用来创造一个设计。使用更大的IP模式,如处理器、接口控制器或总线逻辑是基于不同考虑的不同问题... 选择最易移植的基础成分 FPGA和ASIC的能力不断增加,且设计规模也随着越来越一体化和功能的增多而增长。需求越来越频繁的受到购买力的阻滞。为讨论本设计的可移植性,这些IP模块可分为三类: 专有格式中的FPGA IP由FPGA厂商提供:这一类根本就不可移植,还包括了类似MicroBlaze和Nios处理器。采用专有IP取代专有职能需要做出很大的努力,使得设计技术不断变化,。例如,更换处理器意味着在该处理器写入的所有软件也会随之改变。 RTL格式中的开放市场IP:这种类型可以针对多个技术平台。此类别设计根本不需要修改,但在第二次使用时IP业务许可证可能需要修改。例如,一个RTL块可以在一种新技术中重新合成。 带有行业标准接口的IP,可替换类似内核:这一类包括的IP如PCI Express ,其有行业定义的接口称为PIPE( PCI Express的PHY接口)之间的物理和控制逻辑。如果设计人员的RTL以PIPE为接口,那么就可以移植。例如,如果在FPGA中使用兼容PIPE的FPGA收发器元素,那么相当于兼容PIPE收发器可以获得授权分别用于ASIC设计,反之亦然。其它可移植IP的例子和各自的接口标准包括DDR (DFI)、USB接口( UTMI )、SATA接口( SAPIS )和10Gb的以太网( XGMII ) 。 结论 可移植设计可能是处于热门的FPGA器件进入市场无坚不摧的标准产品的关键转折点。利用SDC约束、推断基元,包装机周围的特殊技术功能模块,以及开放市场的IP ,设计人员可以获得大量的FPGA和ASIC技术。 这样,才能够使他们的产品具有足够的灵活性,以适应成本效益和利润最大化的执行,无论需求如何变化。图4总结了简化结构的概念。今天的工程师们可以通过仔细规划未来的可移植性为家庭经营设计奠定基础。  图4 目标独立方法 |

网友评论