вЛжжЛљгкЪЁЪБПМТЧЕФЩюбЧЮЂУзVLSIЕФЮяРэбщжЄЗНЗЈ

ЗЂВМЪБМфЃК2010-9-30 09:39

ЗЂВМепЃКeetech

|

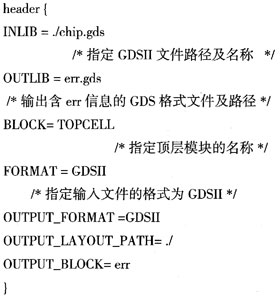

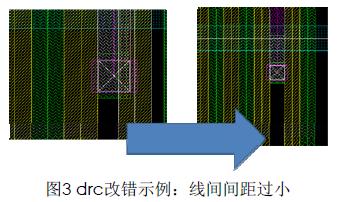

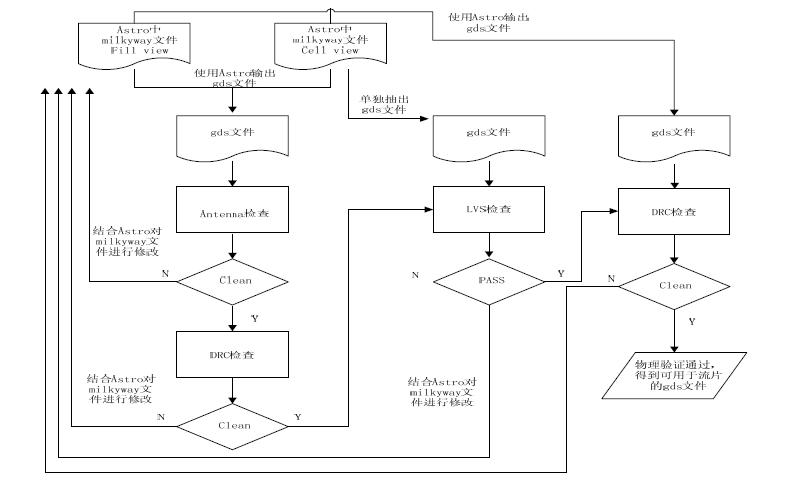

ГЌДѓЙцФЃМЏГЩЕчТЗЩшМЦНјШыЕНЩюбЧЮЂУзЙЄвеКѓЃЌвдЪБађЧ§ЖЏЮЊжїЕФПЊЗЂЗНЗЈЪЙгУИќМгЦеБщЃЌУцСйЕФаТЬєеНвВЫцжЎЖјРДЃКЮЊСЫПЩжЦдьадЖјвЊУцСйдНРДдНЖрЕФН№ЪєВуУмЖШЮЪЬтКЭЬьЯпаЇгІЮЪЬтЃЌЭЌЪБУцЛ§МѕаЁСЫЃЌЕЋгЩгкСЌЯпбгЪБаЇгІгАЯьЃЌИјВМОжВМЯпДјРДСЫРЇФбЃЌвджСгкВЛЕУВЛИљОнВМЯпКѓЪБађЕФНсЙћЛиЙ§ЭЗжиаТЕїећЪБађдМЪјвдБЃжЄКѓУцВМЯпКѓТњзуЪБађвЊЧѓЁЃетЪЙЕУећИіКѓЖЫЕФЪБМфНјЖШбЙСІМгДѓЃЌгШЦфЖдЮяРэбщжЄЖјбдЃЌзїЮЊКѓЖЫЩшМЦШЫдБНЋЩшМЦНЛИјДњЙЄГЇМвЧАЕФзюКѓвЛЕРГЬађЃЌЪБМфБЛбЙЫѕЕФКмНєЁЃвђДЫгаБивЊЬсГівЛЬзГЩЪьЕФЮяРэбщжЄЗНЗЈЃЌРДМгПьЮяРэбщжЄЕФЫйЖШЃЌЮЊМгПьаОЦЌбаЗЂЫйЖШЃЌОЁПьНјШыЪаГЁгЎЕУЪБМфЁЃ 1 ЮяРэбщжЄМАЙЄОпМђЪі ДЋЭГЕФЮяРэбщжЄжївЊАќРЈЩшМЦЙцдђМьВщ(DRC)ЃЌЬьЯпаЇгІМьВщ(ANT)ЃЌАцЭМвЛжТадбщжЄ(LVS)КЭЕчЦјЙцдђМьВщ(ERC)ЫФВПЗжЃЌБОПЮЬтЪЙгУЕФЙЄОпЪЧSynopsysЙЋЫОЕФАцЭМЙЄОпAstroКЭЮяРэбщжЄЙЄОпHerculesЁЃHerculesгЕгаНјааГЌЩюбЧЮЂУз(UDSM)ЙЄвебщжЄЕФФмСІЃЌПЩНјаавкУХМЖЕФЮЂДІРэЦїКЭЧЇЭђУХМЖЕФASICЕФЮяРэбщжЄЁЃЭЈЙ§ИќМгИпаЇЕФбщжЄРДЫѕЖЬЩшМЦжмЦкЃЌВЂЬсЙЉЭМаЮНчУцРДАяжњЩшМЦШЫдБПьЫйЗЂЯжКЭИФе§ЮЅР§ДэЮѓЁЃЫќПЩвдКЭSynopsysЙЋЫОЕФmilkywayЪ§ОнНјааЮоЗьСЌНгЃЌЩшМЦШЫдБЪЙгУmilkywayЪ§ОнНјааВМОжВМЯпКЭАцЭМгХЛЏЁЃMilkywayЪЧAstroЙЄОпЕФАцЭМИёЪНЃЌЫќЕФЩшМЦЕЅдЊГЦЮЊcellЃЌКЌгаЖржжЪгЭМ (View)ЃЌЦфжагыЮяРэбщжЄЙиЯЕУмЧаЕФЪЧCEL ViewКЭFILL ViewЃЌCEL ViewКЌгаЪЕЯжТпМЙІФмЕФАцЭМаХЯЂЃЌFILL ViewКЌгаНјааПЩжЦдьадЩшМЦ(Design for ManufacturingЃЌDFM)ЪБВхШыЕФЬюГфН№Ъє(metal filler)аХЯЂЁЃБОДІЕФDFMЪЧжИЖдВМЯпНсЪјКѓЕФЩшМЦЮЊСЫТњзуЙЄвежЦдьадвЊЧѓЃЌИљОнЬьЯпаЇгІЙцдђЁЂУмЖШЩшМЦЙцдђЕШНјааЕФВхШыЖўМЋЙмЃЌЬэМгЬюГфН№ЪєЃЌЗХШЫfillЕЅдЊЕШВйзїЕФзмГЦЁЃЦфжаЬэМгmetal fillerЪЧЮЊСЫТњзуИВИЧУмЖШвЊЧѓЖјЬэМгШпгрЕФЖрОЇЙшЛђН№ЪєЃЌНсЙћЪЧЩњГЩСЫЖдгІcellЕФFILLViewЁЃFILL ViewдкаоИДDRCДэЮѓМАANTДэЮѓКѓвЊМАЪБНјааЕїећЃЌВЛШЛгжЛсв§ШыаТЕФDRCЮЪЬтЁЃAstroНјааЮяРэбщжЄЪБжЇГжHercules explorerКЭvueСНжжЭМаЮЛЏНчУцЙЄОпЃЌБОПЮЬтЪЙгУЕФЪЧvueНчУцЃЌРДЖдherculesЗЂЯжЕФЮЪЬтНјааЖЈЮЛКЭаоИДЁЃдкНХБОЩшжУЮФМў (runset)ЮФМўжаЩшЖЈOPTIONS {CRE-ATE_VUE_OUTPUT=TRUE}ЩњГЩ.vueЮФМўЃЌдкAstroжаЦєЖЏHerculesШЛКѓНшжњ.vueЮФМўОЭПЩвдНшжњДэЮѓЖЈЮЛНјаааоИФСЫЁЃ дкHerculesЙЄОпНјааЮяРэбщжЄжЎЧАЃЌПЩвдЪЙгУAstroЙЄОпНјааКѓЖЫбщжЄЃЌЯШааМьВщMilkywayЮФМўжаДцдкЕФDRCКЭLVSДэЮѓВЂИќе§ЁЃAstroжЇГжЩюбЧЮЂУзЙЄвеЯТдкЙЄвеЮФМўжаНјааСЫЖЈвхЕФЩшМЦЙцдђМьВщЃЌЪЙгУУќСюgeAdvDRCЛђепgeNewDRCПЩвдЕїгУетвЛЙІФмЃЌЙЄОпЛсЩњГЩДэЮѓЕЅдЊЮЛжУаХЯЂЃЌдкЩЯУцЛсБъГіПЩФмГіЯжЮЪЬтЕФЧјгђЃЌБугкИќе§ЁЃЪЙгУУќСюgeNewLVSПЩвдНјааМђЕЅЕФLVSМьВщ---СЌНгадМьВщЃЌПЩвдЗЂЯжАцЭМжаЕФЖЯТЗЛђПЊТЗЮЪЬтЃЌЭЌбљвВЛсЩњГЩвЛИіДэЮѓЕЅдЊЮЛжУаХЯЂЗНБуИФе§ЁЃ 2 ЮяРэбщжЄзщГЩ DRCЃЌМДЩшМЦЙцдђбщжЄЃЌЫќвЊЧѓЩшМЦЕФАцЭМЮФМўвЊТњзуЖрБпаЮзюаЁУцЛ§ЃЌЭЌВувдМАВЛЭЌВуМфЖрБпаЮФкВПзюаЁМфОрЃЌЭтВПзюаЁМфОрЃЌвдМАЮЊСЫШЗБЃПЩжЦдьадЖјНјааЕФУмЖШМьВщЕШЁЃдкЮяРэбщжЄНзЖЮЃЌЮЊСЫЯћГ§DRCДэЮѓЖјНјааЪжЙЄИФЖЏЪБГЃГЃЛсв§ШыаТЕФДэЮѓЁЃгШЦфЪЧОЙ§DFMКѓЕФЩшМЦЃЌЬюГфН№ЪєЕФв§ШыЛсдіМгзюаЁМфОрЛђзюаЁУцЛ§ЕШРраЭЕФДэЮѓЃЌетаЉвђН№ЪєЬюГфВњЩњЕФДэЮѓПЩдкзюКѓМЏжадкFILL ViewжаИФЭъЁЃ  ANTЪЧЬьЯпаЇгІМьВщЃЌетвВЪЧКЭЕчТЗжЦдьЙ§ГЬгаЙиЕФЮЪЬтЃЌЮЊСЫЗРжЙЬЋЖрЕФЕчзгдкЦЬН№ЪєВуЕФЙ§ГЬжаМЏжаЕНЕМЯпЩЯЛїДЉеЄМЋЃЌБиаыБЃжЄЭЌВуЕФЕМЯпГЄЖШВЛФмЬЋГЄЁЃНтОіЬьЯпаЇгІЮЪЬтгаСНжжЗНЗЈЃЌвЛЪЧдкВњЩњЬьЯпаЇгІЕФзпЯпЩЯЬэМгЗДЯђЖўМЋЙмЃЌетбљПЩвдБЃЛЄеЄМЋЃЛЖўЪЧВЩгУЯђИќИпВуЕФН№ЪєНјааЬјЯпСЌНгЃЌетбљдкМгЙЄЙ§ГЬжаОЭПЩвдБмУтЙ§ЖрЕчзгЕФЛ§ОлЁЃдкПЩжЦдьадЙЄвежЎЧАЃЌгЩгкАцЭМжаУЛгаМгШыЬюГфгУЕФН№ЪєЃЌПЩвдгУЕквЛжжЗНЗЈРДМгШыЖўМЋЙмвдЯћГ§ЬьЯпаЇгІЃЌЕЋдкDFMжЎКѓЕФЮяРэбщжЄВПЗжЃЌвбОКмФбдйевЕНПеЯаЕФПеМфВхШЫЖўМЋЙмЃЌетЪБОЭгІИУЪЙгУЕкЖўжжЗНЗЈРДНтОіЬьЯпаЇгІЮЪЬтЁЃ  ОЭСїГЬЖјбдЃЌDRCМьВщКЭANTМьВщгаЯрЫЦжЎДІЃЌШчЭМ1ЫљЪОЁЃдкЪЙгУAstroНјааСїЮФМўЪфГіЕУЕНCDSIIЮФМўКѓЃЌИљОнЪЕМЪЩшМЦЕФЖЅВуФЃПщУћГЦКЭТЗОЖЃЌЖдДњЙЄГЇМвЬсЙЉЕФЛљгкHerculesЕФDRCЙцдђЩшжУЮФМўНјааИФЖЏЃЌШчЯТР§ЃК  HeaderВПЗжЯТУцЪЧМьВщЪБКђвЛаЉбЁЯюЕФЩшжУЃЌЛЙгаВуЕФЖЈвхвдМАЙцдђЕФУшЪіЁЃЩшжУКУжЎКѓОЭПЩвддЫааHe rculesНјааDRCЛђANTбщжЄСЫЁЃШчЙћЪЙгУСЫе§ШЗЕФrunsetЮФМўЃЌЕУЕНЕФDRCДэЮѓвЛАуЪЧЭМаЮМфОрДэЮѓЁЂПэН№ЪєМфОрДэЮѓЃЌН№ЪєУмЖШДэЮѓЕШЃЌЖјANTДэЮѓвВЛсИјГіОпЬхЗЂЩњЮЪЬтЕФзпЯпУћГЦЃЌетбљдйдкAstroРяЕїгУvueЭМаЮНчУцНјааИФДэМДПЩЁЃ  LVSЪЧАцЭМдРэЭМвЛжТадбщжЄЃЌгУгкБШНЯСНепОЇЬхЙмМЖЕФСЌНгЪЧЗёе§ШЗЃЌТпМЙІФмЪЧЗёвЛжТЃЌЦфЙ§ГЬЗжСНВНЃКЕквЛВНЃЌHerculesЖСШыАцЭМЮФМўЃЌДгАќКЌгаЦїМўМАЦфЯрЛЅМфЕФСЌЭЈадЕФАцЭМЪ§ОнПтжаЬсШЁГіАцЭМЭјБэЃЛЕкЖўВНЃЌHerculesЖСШыАцЭМЭјБэКЭдРэЭМЭјБэЃЌШЛКѓЖдееетСНИіЭјБэЕФСЌНгЧщПівдШЗЖЈЫќУЧЪЧЗёвЛжТЁЃЖдееЪБЃЌHerculesДгЕчТЗЕФЪфШыЪфГіПЊЪМЫбЫїЃЌевЕНвЛИіЦЅХфНкЕуКѓОЭИјИУЦЅХфНкЕуКЭЦїМўИГвдЦЅХфзДЬЌжЕЃЌЕБгіЕНВЛЦЅХфЕФНкЕуЪБЃЌОЭЭЃжЙИУТЗОЖЕФЫбЫїЃЌжБЕНЫљгаЕФТЗОЖЖМЫбЫїЭъБЯЃЌHer-culesНЋНкЕуКЭЦїМўЕФЦЅХфНсЙћаДШыЪфГіЮФМўЃЌИјГіСЌНгМАЦЅХфЧщПіЕФБЈИцЃЌЩшМЦШЫдБПЩвдИљОнБЈИцРДИФе§ВЛЦЅХфЕФдЊМўЃЌLVSбщжЄСїГЬШчЭМ4ЫљЪОЁЃ  НјааLVSбщжЄЕФЩшжУНЯЮЊИДдгЃЌГ§СЫгыDRCРрЫЦЕФЖдfoundryЬсЙЉЕФrunsetЮФМўНјааЩшжУЭтЃЌЛЙвЊЬсШЁverilogЭјБэЃЌНјааЭјБэзЊЛЛ(netTran)ЕУЕНHerculesИёЪНЭјБэКЭЖдЕШЮФМў(Equivalence File)ЁЃЖдЕШЮФМўПЩвдМђЛЏБШНЯЙ§ГЬЃЌБШШчЮФМўжажИЖЈequiv dpram_8xlk=dpram_8xlk{} HerculesдкLVSБШНЯЕФЪБКђОЭжБНгБШНЯгУЛЇжИЖЈЕФетаЉЕЅдЊЕФАцЭМКЭЕчТЗЭМЕФЦЅХфадЃЌЖјВЛБШНЯЦфЫћЕФФЃПщЁЃдЫааHerculesЩњГЩНсЙћКѓЃЌВщПДНсЙћЮФМўВЂНсКЯAstroНјааИФе§ЁЃ 3 ЮяРэбщжЄСїГЬ вЛАуЖјбдLVSгыЕчЦјЙцдђМьВщ(ERC)ЕФЙиЯЕУмЧаЃЌERCжївЊАќРЈБШШчЖЬТЗЁЂПЊТЗЁЂаќИЁЕШЃЌЖдгквЛИіERCМьВщЭЈЙ§ЕФЩшМЦЃЌLVSВХеце§ПЩвдМьВщГідЊМўЕФСЌНгЮЪЬтЁЃвђДЫЃЌERCгІИУдкLVSжЎЧАЭъГЩЃЌашвЊзЂвтЕФЪЧHerculesЕФERCМьВщПЩвдМЏГЩдкDRCКЭLVSМьВщжаЃЌвдРћгкећЬхНјааМьВщКЭИФНјЁЃБОПЮЬтЫљВЩгУSmic18LGЙЄвеЕФЮяРэбщжЄНЋERCМьВщЗжБ№МЏГЩЕНЬьЯпаЇгІМьВщКЭLVSЕФЕчЦјСЌНгМьВщжаЁЃЕЋвЛАуЖјбдЃЌDRCЃЌANTгыLNSдђУЛгаБиШЛЕФЯШКѓЫГађЁЃИљОнЙЄГЬОбщЃЌдкаоИДANTДэЮѓЪБЃЌГЃГЃашвЊИќИФЬюГфН№ЪєаЮзДКЭЮЛжУЃЌЖјетгжЛсДјШыаТЕФDRCЮЪЬтЃЌвђДЫБШНЯРэЯыЕФзіЗЈЪЧЯШаоANTДэЮѓЃЌЕШМьВщЭЈЙ§КѓдйНјааDRCаоИДЧАУцв§ШыЕФЩшМЦЙцдђЮЅР§ЃЌетбљВЛЕЋПЩвдаоИД DRCЃЌЖјЧвПЩвдЮЊКѓУцНјааLNSОЁПЩФмЕФХХГ§ИЩШХЃЌШЛКѓНјааLVSЃЌашвЊзЂвтЕФЪЧЃЌLVSВЛЩцМАFILL ViewЃЌМДКЌгаЬюГфН№ЪєаХЯЂЕФАцЭМВуЃЌЖјНјааLVSЪБдкЬсШЁАцЭМВЮЪ§НзЖЮЃЌШчЙћКЌгаЬюГфН№ЪєаХЯЂЛсЕМжТЬсШЁЕФВЮЪ§ЮФМўЙ§ДѓЃЌвЛжТадБШНЯЪБвВЛсеМгУНЯЖрФкДцЃЌвђДЫПЩвдЪЙгУВЛКЌFILL ViewаХЯЂЕФCDSIIАцЭМЮФМўНјааLVSГѕВНМьВщЃЌОБШНЯВЂаоИФжСМьВщЭЈЙ§ЪБдйЪЙгУКЌЬюГфН№ЪєаХЯЂЕФGDSIIЮФМўЬсШЁВЮЪ§ВЂзїзюКѓЕФLVSЃЌетЪБЕФНсЙћЛсгыЧАУцРрЫЦЃЌШчЙћМьВщЭЈЙ§дђПЩзїзюКѓЕФDRCМьВщЃЌШєНсЙћЯдЪОУЛгаЮЅР§дђПЩНјаазюКѓЕФСїЦЌЁЃЮяРэбщжЄСїГЬШчЭМ5ЫљЪОЁЃ  4 НсТл БОПЮЬтЪЙгУЕФЗўЮёЦїЪЧРЫГБЗўЮёЦїNL380G2ЃЌ3.6GЫЋКЫCPUЃЌXeon8GФкДцЃЌНјаабщжЄЕФЩшМЦЮЊЖўАйЭђУХМЖФГаЭКХЕїжЦаОЦЌЩшМЦЃЌЙЄОпЮЊHer-cules2004.12ЁЃОЩгаЕФСїГЬЪЧАДОбщВЩгУЛђЯШLVSЛђЯШDRCЃЌЖјАДееБОЮФЬсГіЕФСїГЬдкЪЕМЪЕФЩшМЦжавбООЙ§бщжЄЁЃШчЙћЪЙгУКЌга FILL ViewаХЯЂЕФGDSIIЮФМўНјаавЛБщLVSашвЊНјаа7-8 |

ЭјгбЦРТл