ЛљгкFPGAЕФЦЌЩЯЯЕЭГЕФЮоЯпБЃУмЭЈаХжеЖЫ

ЗЂВМЪБМфЃК2009-2-16 16:40

ЗЂВМепЃКБШЖћИЧ

|

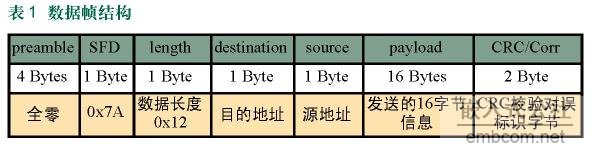

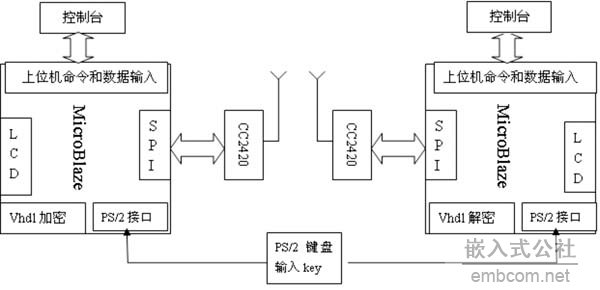

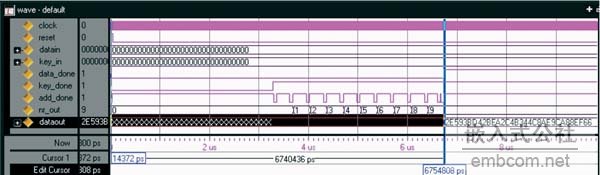

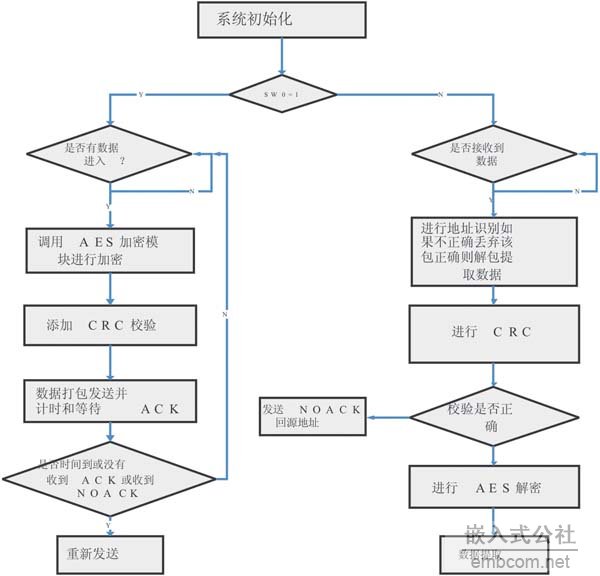

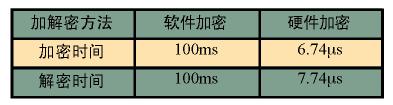

РћгУШэМўЪЕЪЉМгУмЫуЗЈвбОГЩЮЊЪЕЪБАВШЋЭЈаХЯЕЭГЕФживЊЦПОБЁЃБъзМЕФЩЬЦЗЛЏCPUКЭDSPЮоЗЈИњЩЯЪ§ОнМгУмЫуЗЈЕФМЦЫуЫйЖШвЊЧѓЁЃДЫЭтЃЌCPUКЭDSPашвЊЭъГЩЬЋЖрЕФЦфЫћШЮЮёЁЃЛљгкFPGAИпЖШгХЛЏЕФПЩБрГЬЕФгВМўАВШЋадНтОіЗНАИЬсЙЉСЫВЂааДІРэФмСІЃЌВЂЧвПЩвдДяЕНЫљвЊЧѓЕФМгУмДІРэадФмЛљзМ[1].ШЛЖјШчЙћНіЪЙгУFPGAПЩБрГЬVHDLРДЪЕЯжЕФЛАЃЌЯЕЭГОЭВЛЙЛСщЛюЃЌЩ§МЖРЇФбЃЌПіЧвЪЕЯжЦ№РДгаКмДѓЕФФбЖШЃЌБОЯЕЭГвдAESМгУмЫуЗЈЮЊР§ЃЌЪЙгУXilinx SPARTAN 3EЮЊПЊЗЂЦНЬЈЃЌвдxilinxЕФЧЖШыЪНШэКЫmicroblazeЮЊжїПижЦЦїЃЌЕїгУFPGAЕФгВМўVHDLБрГЬЪЕЯжЕФAESМгНтУмКЭПижЦCC2420РДЪЕЯжИпЫйгааЇЕФЪ§ОнЭЈаХЁЃ ЁЁЁЁЯЕЭГЩшМЦЫМЯы ЁЁЁЁБОЩшМЦЪЙгУгВМўУшЪігябдVHDLдкFPGAЪ§зжТпМВуУцЩЯЪЕЯжAESМгНтУмЃЌЮЊСЫЯЕЭГЕФРЉеЙадКЭЙЙНЈСМКУЕФШЫЛњНЛЛЅЃЌЩшМЦЭЈЙ§PS/2МќХЬЪфШыМгУмУмдПЃЌВЂНЋЦфЯдЪОдкLCDЩЯЁЃдкШэКЫMicroBlazeЩЯЃЌЭЈЙ§SPIзмЯпЖСаДFIFOКЭRAMПижЦЩфЦЕаОЦЌCC2420ЃЌЪЙЯЕЭГОпгааХЕРбЁдёЁЂЕижЗЪЖБ№ЁЂздЖЏCRCаЃбщЙІФмЃЌЪЙЯЕЭГИќМгАВШЋЁЂЭЈаХЮѓТыТЪИќЕЭЁЃ ЁЁЁЁЪ§ОнжЁНсЙЙЩшМЦ ЁЁЁЁЮЊСЫИќКУЕФЬсИпБОЯЕЭГЪ§ОнЕФДЋЪфТЪЃЌдкЙйЗНzigbeeЕФЪ§ОнжЁИёЪНЛљДЁЩЯзіСЫаоИФЁЃВЩгУШчБэ5-2ЫљЪОЕФЪ§ОнжЁИёЪНЁЃЪ§ОнжЁЗЂЫЭЪБЃЌCC2420здЖЏдкЪ§ОнАќЕФПЊЪМДІМгЩЯЧАЕМТыКЭжЁЦ№ЪМЗжИєЗћдкЪ§ОнАќФЉЮВМгCRCМьбщЁЃ  ЁЁЁЁБэ1 Ъ§ОнжЁНсЙЙ ЁЁЁЁЪ§ОнПЩППДЋЪф ЁЁЁЁЮЊСЫШЗБЃЪ§ОнВЛГіДэКЭВЛЖЊЪЇЃЌБОЩшМЦВЩгУСЫCRCаЃбщЁЂГЌЪБжиДЋЁЂЗЕЛиACKКЭNOACKЕШДыЪЉРДШЗБЃЪ§ОнЕФВЛГіДэКЭЖЊЪЇЃЌ ЁЁЁЁЯЕЭГФЃПщЙЙГЩ ЁЁЁЁМгУмЖЫЭЈЙ§ДЎПкКЭЭјПкДгЗЂЫЭЖЮНгЪеЪ§ОнЃЌЕБНгЪеЙЛ16зжНк(128bit)ЃЌЛђВЛзуЪБФмздЖЏВЙСуГЩ128bitКѓЫЭИјгВМўAESМгУмФЃПщЁЃдкШэКЫMicroblazeЕФПижЦЯТЭЈЙ§VHDLБрГЬЕФAESМгУмКѓНЋЪ§ОнНјаазщжЁДђАќЃЌЭЈЙ§ШэКЫЖдCC2420ЕФМФДцЦїЕФЖСаДНЋЪ§ОнЭЈЙ§ЮоЯпЗЂЫЭЖЫCC2420ЗЂЫЭГіШЅЃЌЭЌЪБЕШД§ЗЂЫЭЖЮШЗШЯЁЃНгЪеЖЫдкНгЪеЕНЪ§ОнвдКѓ,ДгЪ§ОнАќжаНЋЪ§ОнЬсШЁЃЌНјааПьЫйAESНтУм,НтУмЭъГЩКѓНјааCRCаЃбщЃЌШчЙћаЃбще§ШЗдђЯђдДЕижЗЗЂЫЭACKШЗШЯЁЃНЋе§ШЗЪ§ОнЫЭГіЃЌШчЙћаЃбщЪЇАмЃЌдђЗЕЛиNOACKЁЃЮЊСЫШЗБЃАВШЋЃЌAESМгНтУмЫуЗЈашвЊЕФУмдПkeyгЩМќХЬЪфШыКЭаоИФЃЌЭЌЪБПЩвддкLCDЩЯЯдЪОГіРДЁЃБиаыБЃжЄСНЖЫkeyЯрЭЌВХФмБЃжЄе§ГЃЭЈаХЁЃ  ЁЁЁЁЭМ1 ЯЕЭГзмЬхПижЦЪ§ОнСїЭМ ЁЁЁЁAESМгНтУмФЃПщ ЁЁЁЁ3.1.1 AESМђНщ ЁЁЁЁAESМгНтУмЫуЗЈ(RijndaelЫуЗЈ)ЖдД§МгУмЕФУїЮФЯШНјааЗжЖЮШЛКѓМгУмЃЌУїЮФЕФГЄЖШПЩвдЪЧl28ЮЛЁЂ192ЮЛЛђ256ЮЛЁЃЭЌбљЃЌгУгкМгУмЕФУмдПГЄЖШвВгаl28ЮЛЁЂ192ЮЛЛђ256ЮЛЁЃИљОнУїЮФМАУмдПГЄЖШВЛЭЌЕФзщКЯЃЌМгУмЕФТжДЮга10ТжЁЂ12ТжКЭl4ТжЁЃдкШІКЏЪ§ЕФУПвЛШІЕќДњжаЃЌАќРЈ4ВНБфЛЛЃЌЗжБ№ЪЧзжНкДњЛЛдЫЫуЁЂааБфЛЛЁЂСаЛьКЯвдМАШІУмдПЕФМгЗЈБфЛЛЁЃОЙ§бщжЄЃЌбЁгУl28ЮЛЕФУїЮФКЭУмдПЪЧМИжжзщКЯжаМгНтУмЫйЖШзюПьЕФ[2]ЁЃЫљвддкБОЯЕЭГЩшМЦжаЪЙгУЕФЮЊ128ЮЛУїЮФКЭ128ЮЛУмЮФЕФзщКЯЁЃгЩгкAESЮЊЖдГЦМгНтУмЃЌЫљвддкДЫЮФжаЮвУЧжЛЬжТлAESЕФМгУмЗНЗЈЃЌНтУмОЭЪЧгыAESЖдГЦЕФЗНЪНРДНјааЕФЁЃ ЁЁЁЁ3.1.2 AESМгНтУмФЃПщЩшМЦ ЁЁЁЁдкБОЯЕЭГжаЃЌЪЙгУСЫFPGAЕФгВМўУшЪігябд(VHDL)РДЪЕЯжСЫAESЕФМгНтУмЫуЗЈЃЌAESЗжБ№ЮЊТжУмдПМгЁЂзжНкДњЛЛЁЂаавЦЮЛЁЂСаЛьЯ§ЁЂУмдПРЉеЙЃЌЯТУцЮЊ5ИігУгВМўУшЪігябдЪЕЯжЕФаЁФЃПщЕФЗжБ№НщЩмЁЃгЩгкСаЛьЯ§ФЃПщЁЂаавЦЮЛФЃПщЁЂТжУмдПМггыЮФЯз[4]жаЫуЗЈЯрЭЌдкДЫВЛзіЬжТлЁЃ ЁЁЁЁЂй зжНкДњЛЛФЃПщ ЁЁЁЁДЫФЃПщЮЊAESжаЕФУПвЛИізжНкЬсЙЉСЫвЛИіЗЧЯпадДњЛЛЁЃШЮвЛЗЧСузжНкБЛКЏЪ§ЫљДњЬцЁЃШчЙћxЪЧСузжНкЃЌy=bОЭЪЧSubBytesБфЛЏЕФНсЙћЁЃдкБОЩшМЦжаЃЌЮЊСЫМгПьЫуЗЈЫйЖШЃЌНЋSКадЄЯШаДШыRAMжаЃЌжБНггУЕижЗРДжИЪОЬцДњЕФзжНкЃЌРћгУПеМфРДЛЛЪБМфЃЌДяЕНСЫМгПьгУЫуЕФФПЕФЁЃ ЁЁЁЁЂкУмдПРЉеЙФЃПщ ЁЁЁЁБОЩшМЦВЩгУСЫXilinx IPКЫSingle Block RAMЮЛПэ32ЃЌЩюЖШ64ЃЌдкГЬађЕФПЊЪМЃЌгЩгУЛЇЩшжУЕФГѕЪМУмдПЯЕЭГАДееУмдПРЉеЙЫуЗЈЩњГЩЕФ10ТжРЉеЙУмдПЃЌНЋЩњГЩЕФУмдПАДееЕижЗДЮађДгЕЭЕНИпЗХШыRAMжаЃЌдкУПвЛТжжДааaddroundkeyЪБШЁГіЖдгІТжЪ§ЕФУмдПЃЌгыУїЮФЯрМг(вьЛђ)ЁЃ  ЁЁЁЁЭМ2 AESНтУмФЃПщЗТецВЈаЮ ЁЁЁЁЮоЯпЭЈаХФЃПщ ЁЁЁЁдкБОЯЕЭГжаВЩгУTI ЙЋЫОЕФCC2420РДЪЕЯжЪ§ОнЕФЮоЯпЭЈаХCC2420ЙЄзїгкУтЪкШЈЕФ2.4GHzЦЕЖЮЃЌ33Иі16ЮЛХфжУМФДцЦїЁЂ15ИіУќСюбЁЭЈМФДцЦїЁЂ1Иі128зжНкЕФRX RAMЁЂ1Иі128зжНкЕФTXRAMЁЂ1Иі112зжНкЕФАВШЋаХЯЂДцДЂЦїЁЃTXКЭRXRAMЕФДцШЁПЩЭЈЙ§ЕижЗЛђепгУСНИі8ЮЛЕФМФДцЦїЁЃжїЛњПЩЭЈЙ§SPIзмЯпЩшжУЦфЙЄзїдкNormalФЃЪНЃЌЭЈЙ§SPIзмЯпMOSIЃЌMISOНгПкЖдTXFIFOКЭRX FIFOМАзДЬЌНјаааДКЭЖСЕФВйзїЃЌНЋЪ§ОнаДШыКЭЖСГіRAMРДЪЕЯжгыCC2420ЕФЪ§ОнДЋЪфЃЌЭЈЙ§ДЅЗЂCC2420STXON,SRXONРДЪЕЯжЪ§ОнЕФЮоЯпЗЂЫЭКЭНгЪеЁЃБэЖўЪЧБОЯЕЭГCC2420ЩцМАЕФМФДцЦїМАЦфЙІФмЁЃ  ЁЁЁЁБэ2 ЪЧБОЯЕЭГCC2420ЩцМАЕФМФДцЦїМАЦфЙІФм ЁЁЁЁШэКЫПижЦФЃПщ ЁЁЁЁ3.3.1 ШэКЫMicroBlazeМђНщ ЁЁЁЁMicroBlaze ЪЧвЛПюгЩxilinxЙЋЫОПЊЗЂЕФЧЖШыЪНДІРэЦїШэКЫЃЌЦфВЩгУRISC(Reduced Instruction Set Computer)гХЛЏМмЙЙЁЃЫќЗћКЯIBM CoreConnectБъзМЃЌФмЙЛгыPPC405ЯЕЭГЮоЗьСЌНг[3]ЁЃMicroBlazeЪЧвЛИіЗЧГЃМђЛЏШДОпгаНЯИпадФмЕФШэКЫЃЌдкSpartan3EЯЕСаFPGAжаЫќжЛеМ400ИіSliceЃЌЯрЕБгк10ЭђУХFPGAШнСПЕФ1/3ЁЃЦфЮЊЙўЗ№НсЙЙЃЌ32ЮЛЕижЗзмЯпЃЌЖРСЂЕФжИСюКЭЪ§ОнЛКДцЃЌВЂЧвгаЖРСЂЕФЪ§ОнКЭжИСюзмЯпСЌНгЕНIBMЕФPLBзмЯпЃЌЪЙЕУЫќФмКмШнвзКЭЦфЫќЭтЩшIPКЫвЛЦ№ЭъГЩећЬхЙІФмЁЃжЇГжSPIЁЂI2CЁЂPCIЁЂCANзмЯпЃЌжЇГжжижУЁЂгВМўвьГЃЁЂжаЖЯЁЂгУЛЇвьГЃЁЂднЭЃЕШЛњжЦЃЌПЩХфжУUARTЁЂGPIOЕШНгПкЁЃ ЁЁЁЁ3.3.2 microblazeЕФПижЦСїГЬ  ЁЁЁЁЭМ3 microblazeЕФПижЦСїГЬ ЁЁЁЁ3.3.3 microblazeЕФПижЦСїГЬжїГЬађ ЁЁЁЁmain () { ЁЁЁЁInitial()//ГѕЪМЛЏЯЕЭГ; ЁЁЁЁCmdSend()//ЩЯЮЛЛњУќСюЪфШы; ЁЁЁЁDataRev()//Ъ§ОнНгЪе; ЁЁЁЁAESEny()//Ъ§ОнМгУм; ЁЁЁЁDataPackage()Ъ§ОнДђАќ; ЁЁЁЁCC2420Sen()МгУмЪ§ОнЗЂЫЭ; ЁЁЁЁReturn success; } ЁЁЁЁНсгя ЁЁЁЁБОЯЕЭГНЋШэМўМгНтУм(дк50MЕФЦЕТЪЯТЪЙгУШэМўРДНјааМгНтУм)гыгВМўМгНтУмЪБМфзіСЫЖдБШЃКШчБэ3ЫљЪОЁЃ  ЁЁЁЁБэ3 ШэМўКЭгВМўМгУмЖдБШ  Бэ4 AESМгУмеМгУFPGAзЪдДЭГМЦБэ ЁЁЁЁИУЗНАИГфЗжгааЇЕФРћгУСЫSpartan3EЕФзЪдДЃЌгШЦфЮЊПЩБрГЬТпМКЭRAMЕФРћгУЁЃЦфжаAESМгНтУмжаЕФГЫЗЈдЫЫуОљгЩLUTВщевБэРДЪЕЯжЃЌгУПеМфЛЛШЁЪБМфЃЌЛёЕУСЫКмИпЕФЫуЗЈЫйЖШЁЃдкAESЫуЗЈВтЪдЪБЮвУЧЗЂЯж80%ЕФAESМгНтУмЪБМфЖМгУгкУмдПРЉеЙЫуЗЈжаЃЌШчЙћФмдйНјвЛВНАбЫуЗЈгХЛЏЃЌБШШчзіГЩСїЫЎЯпЕФЫуЗЈФЃЪНЕФЛАЃЌМгНтУмЪБМфгжФмМѕЩйНќ20%ЃЌМДгЩЯждкЕФ6.74usМѕЩйЕНТдДѓгк5.39usЃЌаЇТЪгжПЩвддіМгКмЖрЁЃ |

ЭјгбЦРТл