ИпМЖЖЏЬЌадФмФЃЪ§зЊЛЛЦї

ЗЂВМЪБМфЃК2010-9-25 11:28

ЗЂВМепЃКeetech

ЙиМќДЪЃК

ЖЏЬЌадФм , ФЃЪ§зЊЛЛЦї

|

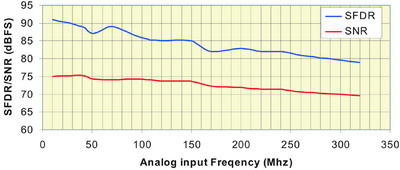

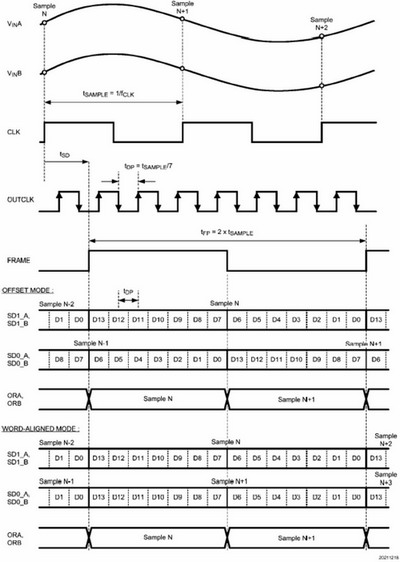

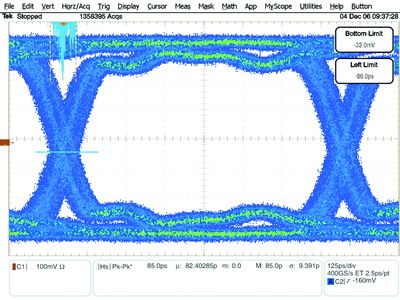

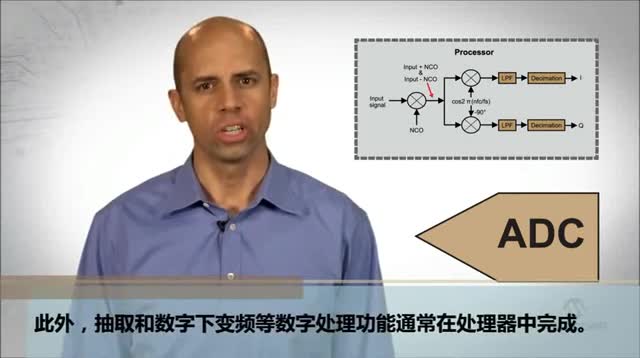

ADC12C/DSxxxгыADC14C/DSxxx ADC12C/DSxxxКЭADC14C/DSxxxЯЕСаФЃЪ§зЊЛЛЦїФкжУИпадФмЕФВЩбљМАБЃГжЗХДѓЦїКЭИпОЋЖШДјЯЖЕчбЙВЮПМЕчТЗЃЌЪфШыДјПэИпДя1GHzЃЌвђДЫПЩвджЇГжжаЦЕВЩбљЙЄзїЁЃДЫЭтЃЌетЯЕСааОЦЌЪфШыЗНУцгаЕЅМАЫЋЭЈЕРЃЌЖјЪфГіЗНУцгаВЂааCMOSМАДЎааLVDSПЩЙЉбЁдёЃЌИќШнвзНЋFPGAЛђASICгыФЃФт/Ъ§зжзЊЛЛЦїСЌНгвЛЦ№ЁЃетЯЕСааОЦЌЕФИїаЭКХВњЦЗЖМв§НХМцШнЃЌШЗБЃЯЕЭГПЩвдЧсвзгЩ12ЮЛЩ§МЖжС14ЮЛЃЌВПЗжаОЦЌИќПЩдкЩуЪЯ-40жС+85ЁцЕФЙуРЋЙЄвЕЮТЖШЗЖЮЇФкЙЄзїЁЃЕЅЭЈЕРЕФаЭКХВЩгУ32в§НХЕФLLPЗтзАЃЌГпДч5mmЁС5mmЃЌЖјЫЋЭЈЕРЕФаЭКХдђВЩгУ60в§НХЕФLLPЗтзАЃЌГпДч9mmЁС9mmЁЃ етЯЕСаФЃЪ§зЊЛЛЦїШєвд1GHzвдЩЯЕФТњЙІТЪДјПэЙЄзїЃЌдђОпгагХСМЕФЖЏЬЌадФмМАЯпадЖШЃЌЙІКФНЯЕЭЁЃетЯЕСааОЦЌШєвдИпДя300MHzЕФЪфШыЦЕТЪЙЄзїЃЌЦфЮодгЩЂаХКХЖЏЬЌЗЖЮЇ(SFDR)ПЩИпДя80dBЁЃШєВЩгУ3.0VЕФЙЉЕчЕчбЙЃЌЦфЙІКФИќЕЭжС320mWЁЃМДЪЙЪфШыЦЕТЪГЌЙ§300MHzЃЌаХдыБШШдШЛИпДя70dBвдЩЯЃЌШУЯЕЭГЩшМЦЙЄГЬЪІПЩвдГфЗжРћгУетИіЕЭдыЩљЕФгХЕуЃЌИФЩЦвЦЖЏЕчЛАЛљеОЕФНгЪеФмСІЁЃгЩгкетЯЕСааОЦЌОпгаИпДјПэМАИпВЩбљТЪЕФгХЕуЃЌвђДЫПЩвджЇГжИпжаЦЕВЩбљЁЃЛЛбджЎЃЌЯЕЭГЮоашМгЩшЯТБфЦЕМЖЃЌЮЊЯЕЭГНкЪЁПЩЙлЕФГЩБОЃЌЖјЧвЕЭЙІКФЕФЬиЕувВСюЯЕЭГИќЮШЖЈПЩППЁЃзюКѓвЊЧПЕїЕФвЛЕуЪЧЃЌетЯЕСааОЦЌЕФДјПэКмИпЃЌвђДЫЧ§ЖЏЦїЗХДѓЦїВЛЛсЪмЬЋЖрЕФЯожЦЃЌШУЙЄГЬЪІПЩвдОЋМђаХКХТЗОЖЕФТЫВЈЯЕЭГЁЃ ШєФЃФтЪфШыЦЕТЪНЯЕЭЃЌдђвд80MSPSЕФВЩбљТЪЙЄзїЃЌЦфаХдыБШПЩДя75dBFSЃЌ SFDRПЩДя90dBЃЌгааЇЮЛЪ§(ENOB)12ЮЛЁЃШєВЩбљТЪЮЊ105MSPSЃЌаХдыБШПЩДя74.5dBFSЃЌSFDRПЩДя90dBЃЌENOBПЩДя11.9ЮЛЁЃжСгкжБСїЕчЗНУцЕФБэЯжЃЌетЯЕСаФЃЪ§зЊЛЛЦїЕФЪфШыЦЋвЦЮѓВюЁР1mVЃЌдівцЮѓВюЁР0.5%FSЃЌЮЂЗжЗЧЯпад(DNL)ЮѓВюЁР0.5LSBЃЌЖјЛ§ЗжЗЧЯпад(INL)ЮѓВюЁР1.5LSBЁЃгЩгкетЯЕСааОЦЌВЩгУЯШНјЕчТЗЩшМЦЃЌвђДЫЙІКФПЩНЕжСзюЕЭЃЌЪЕМЪЙІКФдђШЁОігкЙЄзїЦЕТЪЁЃгЩгкЪБжгЪфГів§НХЕФЩЯЩ§БпдЕЮЛгкЪфГіаХКХблЭМЕФжабыЮЛжУЃЌвђДЫЯЕЭГЩшМЦЙЄГЬЪІПЩвдРћгУЪБжгЪфГів§НХВЖзНВЂааЕФCMOSЪфГіЪ§ОнЁЃ ИпЫйДЋЪфЕФНтОіЗНАИ ADC14C105ЫЋЭЈЕРФЃЪ§зЊЛЛЦїПЩНЋСНЬѕЭЈЕРЕФВЛЭЌВЮЪ§ЛЅЯрЖдзМЃЌдкЖдзМЙ§ГЬжаЃЌаОЦЌЯШНЋЫљШЁЕУЕФCMOSЪБжгЪфШыДЋЫЭЕНаОЦЌЕФКЫаФЃЌШЛКѓгЩвЛЬѕЛКГхЭЈЕРдйНЋЪБжгЪфШыДЋЫЭЕНЫЋЭЈЕРЕФЪБжгЪфШыЖЫЃЌећИіЙ§ГЬжЛаш4ИіCMOSеЄМЋЁЃДЫЭтЃЌаОЦЌФкВПЧјЖЮЗжИєМАЙЉЕчТЗОЖМЋЮЊЦЅХфЃЌЪЙЭЈЕРМфЕФПзОЖЖЖЖЏЪЇХфВЛГЌЙ§30fsЃЌЖјЭЈЕРМфЕФПзОЖбгГйЪЇХфдђВЛГЌЙ§50psЁЃДЫЭтЃЌетПюЫЋЭЈЕРФЃЪ§зЊЛЛЦїЕФЭЈЕРМфдівцЮѓВюЪЇХфВЛГЌЙ§ЁР0.2%FSЃЌЦЋвЦЪЇХфВЛГЌЙ§ЁР1mVЃЌЖјЭЈЕРМфЕФДЎвєИЩШХдђДяЕН-95dBвдЩЯЁЃ  ЭМ1 ADC14C105вд105MSPSВЩбљТЪЙЄзїЪБЃЌаХдыБШМАЮодгЩЂаХКХЖЏЬЌЗЖЮЇЕФЦЕТЪБфЛЏ LVDSЪЧИіЕчДХИЩШХМЋЕЭЕФНгПкНтОіЗНАИЃЌзюЪЪгУгкИпЫйЕФЪ§ОнзЊЛЛЦїЃЌвбГЩЮЊИпЫйЪ§ОнДЋЪфЕФБъзМНгПкЁЃДЎааLVDSЪфГіФЃЪ§зЊЛЛЦїЩшгаЕЅЯпМАЫЋЯпСНжжВЛЭЌЕФЪ§ОнДЋЪфФЃЪНЃЌетжжЩшМЦЕФФПЕФЪЧвЊНЕЕЭLVDSЪ§ОнДЋЪфТЪвЛАыЁЃЕЅЯпФЃЪНЪЪгУгк25MSPSжС65MSPSЕФЗЖЮЇЃЌетИіЗЖЮЇФкЕФВЩбљТЪЯрЕБгк350MbpsжС910MbpsЕФЪ§ОнДЋЪфТЪЁЃЫЋЯпФЃЪНЕФЪ§ОнДЋЪфТЪИеКУЪЧЩЯЪіДЋЪфТЪЕФвЛАыЃЌвђЮЊLVDSЪфГів§НХЕФЪ§ФПдіМгСЫвЛБЖЃЌвђДЫЃЌLVDSФЃЪ§зЊЛЛЦїШєВЩгУЫЋЯпФЃЪНЙЄзїЃЌзЊЛЛТЪБуПЩЬсИпЕН50MSPSжС105MSPSЕФЗЖЮЇФкЁЃ LVDSНгПкЩшгаЦЋвЦФЃЪНКЭзжЖдзМФЃЪНСНжжВЛЭЌЕФЪ§ОнВЖзНЗНЪНЃЌвдБуНтДЎЦїИќвзВЖзНЪ§ОнЃЌгУЛЇдђПЩАДееИіБ№гІгУЕФашвЊЃЌбЁгУЪЪКЯЕФЪ§ОнВЖзНЗНЪНЁЃе§ШчЭМ2ЕФЪ§ОнЫљЯдЪОЃЌSD0/SD1СНЬѕЭЈЕРВЩгУзжЖдзМЕФФЃЪНзїЮЊдЄЩшФЃЪНЁЃШєВЩгУЦЋвЦФЃЪНЃЌSD0ЭЈЕРЕФЪ§ОнБШSD1ЭЈЕРЕФЪ§ОнбгГйАыИізжЁЃЛЛбджЎЃЌМгЩшЫЋЯпФЃЪНетвЛбЁЯюПЩвдОЋМђИпЫйЪ§ОнДЋЪфЯЕЭГЕФЩшМЦСїГЬЃЌЪЙЙЄГЬЪІЕФЩшМЦЙЄзїБфЕУИќЮЊШнвзЁЃ  ЭМ2 ЫЋЯпФЃЪНЕФЖЈЪБЪБађЭМ ЮЊСЫШЗБЃLVDSНгПкЕФЕїЪдЙІФмЃЌаОЦЌПЩвджЇГжВЛЭЌЕФВтЪдФЃЪНЃЌАќРЈдЄЩшВтЪдФЃЪНКЭгУЛЇздбЁВтЪдФЃЪНЁЃДЫЭтЃЌетПюЫЋЭЈЕРаОЦЌЕФаэЖрЙІФмЖМПЩМгвдЩшЖЈЃЌР§ШчЃЌПЩвдНЋИіБ№ПижЦв§НХСЌНгЕчдДЛђЕиЯпЃЌШЛКѓНјааЩшЖЈЃЌвВПЩРћгУДЎааЭтЮЇЩшБИНгПк(SPI)ЩшЖЈгаЙиЙІФмЁЃ ЭМ3ЯдЪОвЛЗљЕфаЭЕФблЭМЃЌЭМжаЧхГўЯдЪОДЎааLVDSНгПкШчКЮДЋЫЭЪ§ОнЁЃЭМжаЕФаХКХвд80MSPSЛђ1.12GbpsЕФЫйЖШДЋЫЭЃЌаХКХЖЖЖЏЃЌР§ШчЫцЛњЖЖЖЏЁЂШЗЖЈадЖЖЖЏвдМАВЛЭЌЪ§ОнЕФВЛЭЌЖЖЖЏЃЌЖМЧхГўЯдЪОГіРДЁЃвдЩЯЖЖЖЏЫљВњЩњЕФШЮКЮгАЯьЖМБиаыМЦЫудкФкЃЌвдБуШЁЕУЪ§ОнВЖзНДАПкЁЃетПюФЃЪ§зЊЛЛЦїЮЊЪ§ОнВЖзНЬсЙЉ90%ЕФДАПкШнЯоЁЃ  ЭМ3 ADC14DS105 аОЦЌвд1.12GbpsЫйЖШЙЄзїЪБЕФблЭМ IDCW=80MS/sЁС14bit=1.12Gbps=1bit/892.9 ps ADCW=100ЁС(1 - Tj/IDCW)=100ЁС(1-85ps/892.9ps)=90.5% ЙЋЪНжаЕФIDCWЪЧРэЯыЪ§ОнВЖзНДАПкЃЌЖјADCWЪЧецЪЕЪ§ОнВЖзНДАПкЁЃ |

ЭјгбЦРТл