Іо·ЦРЕєЕ

·ўІјК±јдЈє2010-9-21 11:19

·ўІјХЯЈєeetech

№ШјьґКЈє

Іо·ЦРЕєЕ

|

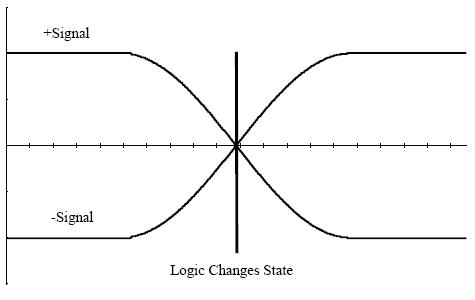

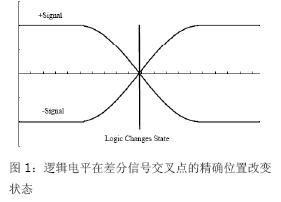

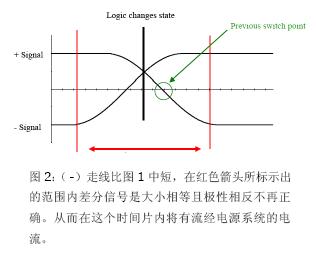

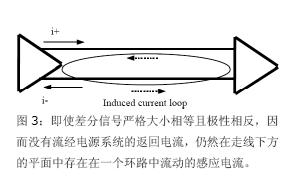

±ај±КјЗЈє±ѕОДµДФЧчХЯОЄDouglas BrooksЈ¬УЙЛјїЖCAD№¤іМК¦ЗЗИс·ТлЎЈОДХВё±±кМвОЄЈєІо·ЦµДІоЎЈ±ѕОДµµµДЦшЧчИ«№йКфФЧчХЯDouglas BrooksІ©Кїј°UltraCAD Design Inc.ЛщУРЎЈ ТлХЯЙщГчЈє·Тл±ѕОДµµґїКфРЛИ¤°®єГЈ¬Г»УРИОєОЙМТµДїµДЎЈ±ѕОДµµµДЦшЧчИ«№йКфФЧчХЯDouglas BrooksІ©Кїј°UltraCAD Design Inc.ЛщУРЎЈЧЄФШј°К№УГ±ѕОДµµЛщІъЙъµД·ЁВЙ·зПХУЙК№УГХЯЧФРРіРµЈЈ¬ЧчХЯІ»іРµЈИОєО·ЁВЙФрИОЎЈ ОТГЗЦРµДґуІї·Ц¶јДЬЦ±№ЫµШАнЅвРЕєЕКЗИзєОСШµјПЯ»тЧЯПЯґ«ІҐµДЈ¬јґ±гОТГЗТІРн¶ФХвЦЦБ¬ЅУ·ЅКЅµДГыіЖІўІ»КмП¤ЎЄЎЄµҐ¶ЛДЈКЅЎЈКхУпЎ°µҐ¶ЛЎ±ДЈКЅЅ«ХвЦЦ·ЅКЅН¬ЦБЙЩЖдЛьБЅЦЦРЕєЕґ«ІҐДЈКЅЗш·ЦїЄАґЈєІоДЈєН№ІДЈЎЈєуГжБЅЦЦіЈіЈїґЖрАґёьјУёґФУЎЈ ІоДЈ ІоДЈРЕєЕСШТ»¶ФЧЯПЯґ«ІҐЎЈЖдЦРТ»ёщЧЯПЯґ«ЛНОТГЗНЁіЈЛщАнЅвµДРЕєЕЈ¬БнТ»ёщґ«ЛНТ»ёцСПёсґуРЎПаµИЗТј«РФПа·ґЈЁЦБЙЩАнВЫЙПИзґЛЈ©µДРЕєЕЎЈІо·ЦУ뵥¶ЛДЈКЅІўІ»ПсЛьГЗХ§їґЙПИҐДЗСщУРєЬґуµДІ»Н¬ЎЈјЗЧЎЈ¬ЛщУРРЕєЕ¶јУР»ШВ·ЎЈТ»°гµШЈ¬µҐ¶ЛРЕєЕґУТ»ёцБгµзО»Ј¬»тµШЈ¬µзВ··µ»ШЎЈІо·ЦРЕєЕµДГїТ»·ЦЦ§¶јЅ«ґУµШµзВ··µ»ШЈ¬іэ·ЗТтОЄГїёцРЕєЕ¶јґуРЎПаµИЗТј«РФПа·ґТФЦБУЪ·µ»ШµзБчНкИ«µЦПыБЛЈЁЛьГЗЦРГ»УРИОєОТ»Ії·ЦіцПЦФЪБгµзО»»тµШµзВ·ЙПЈ©ЎЈ ѕЎ№ЬОТІ»ґтЛгФЪЧЁАёЦРѕНХвёцОКМв»ЁМ«¶аК±јдЈ¬№ІДЈКЗЦёН¬К±ФЪТ»ёцЈЁІо·ЦЈ©РЕєЕµДПЯ¶Ф»тХЯФЪµҐ¶ЛЧЯПЯєНµШЙПіцПЦµДРЕєЕЎЈ¶ФОТГЗАґЛµХвІўІ»ИЭТЧЦ±№ЫµШИҐАнЅвЈ¬ТтОЄОТГЗєЬДСПлПуФхСщІЕДЬІъЙъХвСщµДРЕєЕЎЈПа·ґНЁіЈОТГЗІ»»бІъЙъ№ІДЈРЕєЕЎЈНЁіЈХвР©¶јКЗУЙµзВ·µДјДЙъ»·ѕі»тХЯґУБЪЅьµДНвІїФґсоєПЅшµзВ·ІъЙъµДЎЈ№ІДЈРЕєЕЧЬКЗєЬЎ°ФгёвЎ±Ј¬Рн¶аЙијЖ№жФтѕНКЗУГАґ·АЦ№ЛьГЗµД·ўЙъЎЈ Іо·ЦЧЯПЯ ѕЎ№ЬїґЖрАґХвСщµДЛіРтІ»КЗєЬєГЈ¬ОТТЄФЪРрКцК№УГІо·ЦЧЯПЯµДУЕµгЦ®З°КЧПИАґЅІКцІо·ЦРЕєЕµДІјПЯ№жФтЎЈХвСщµ±ОТМЦВЫЈЁПВГжЈ©ХвР©УЕµгК±Ј¬ѕНїЙТФЅвКНХвР©Па№ШµД№жФтКЗИзєОАґЦ§іЦХвР©УЕµгµДЎЈ ґуІї·ЦК±єтЈЁТІУРАэНвЈ©Іо·ЦРЕєЕТІКЗёЯЛЩРЕєЕЎЈХвСщЈ¬ёЯЛЩЙијЖ№жФтНЁіЈТІКЗККУГµДЈ¬УИЖдКЗ№ШУЪЙијЖЧЯПЯК№Ц®їґЖрАґПсКЗґ«КдПЯµДЗйїц ЎЈХвТвО¶ЧЕОТГЗ±ШРлЧРПёµШЅшРРЙијЖєНІјПЯЈ¬ИзґЛЈ¬ЧЯПЯµДМШХчЧиї№ФЪСШПЯІЕДЬ±ЈіЦІ»±дЎЈ ФЪІо·Ц¶ФІјПЯК±Ј¬ОТГЗЖЪНыГїёщЧЯПЯ¶јУлЖдЕд¶ФЧЯПЯНкИ«Т»ЦВЎЈТІѕНКЗЛµЈ¬ФЪЧоґуµДїЙКµПЦ·¶О§ДЪЈ¬Іо·Ц¶ФЦРГїёщЧЯПЯУ¦ёГѕЯУРТ»ЦВµДЧиї№УлТ»ЦВµДі¤¶ИЎЈІо·ЦЧЯПЯНЁіЈТФПЯ¶ФµД·ЅКЅЅшРРІјПЯЈ¬ПЯ¶ФµДјдѕаСШПЯґ¦ґ¦±ЈіЦІ»±дЎЈНЁіЈµШЈ¬ОТГЗѕЎїЙДЬЅ«Іо·Ц¶ФїїЅьІјПЯЎЈ Іо·ЦРЕєЕµДУЕµг Ў°µҐ¶ЛЎ±РЕєЕНЁіЈІОїјµЅДіР©Ў°ІОїјЎ±µзО»ЎЈХвУРїЙДЬКЗХэµД»тХЯКЗµШµзС№Ј¬Т»ёцЖчјюµДГЕПЮµзС№Ј¬»тХЯБнНвДіґ¦µДРЕєЕЎЈБнТ»·ЅГжЈ¬Іо·ЦРЕєЕЅцІОїјµЅУлЖдЕд¶ФРЕєЕЎЈТІѕНКЗЛµЈ¬Из№ыТ»ёщЧЯПЯЈЁХэРЕєЕЈ©ЙПµДµзС№±ИБнНвТ»ёщЧЯПЯЈЁёєРЕєЕЈ©ёЯЈ¬ОТГЗѕНµГµЅБЛТ»ёцВЯјЧґМ¬Ј¬Из№ыКЗµНЈ¬ОТГЗѕНµГµЅБнНвТ»ёцВЯјЧґМ¬ЈЁјыНј1Ј©ЎЈХвСщУРјёёцєГґ¦Јє  Нј 1µ±Іо·ЦРЕєЕЗъПЯЅ»ІжК±ВЯјЧґМ¬ФЪёГµг·ўЙъёД±д К±РтїЙТФёьѕ«И·µШ¶ЁТеЈ¬ТтОЄїШЦЖТ»¶ФРЕєЕµДЅ»µг±ИїШЦЖТ»ёц№ШУЪЖдЛыІОїјµзС№µДѕш¶ФµзС№ИЭТЧЎЈХвТІКЗЧЯПЯТЄѕ«И·µИі¤µДФТтЦ®Т»ЎЈИОєОФЪФґ¶ЛЛщЅшРРµДК±РтїШЦЖ¶јїЙТФИГІЅЈ¬Из№ыРЕєЕФЪІ»Н¬µДК±јдµЅґпБнТ»¶ЛЎЈЅшТ»ІЅАґЅІЈ¬Из№ыПЯ¶ФµДФ¶¶ЛРЕєЕГ»УРѕ«И·ПаµИЗТј«РФПа·ґЈ¬№ІДЈРЕєЕѕНїЙДЬІъЙъІўЅ«µјЦВРЕєЕК±РтУлEMIОКМвЎЈ ТтОЄіэБЛЧФЙнЈ¬Іо·ЦРЕєЕГ»УРІОїјИОєОЖдЛьРЕєЕЈ¬ІўЗТРЕєЕЅ»ІжµДН¬ІЅїЙТФёьУРБ¦µШїШЦЖЈ¬Іо·ЦµзВ·НЁіЈїЙТФФЛРРФЪ±ИАаЛЖµДµҐ¶ЛµзВ·ёьёЯµДЖµВКЙПЎЈ ТтОЄІо·ЦµзВ·¶ФБЅёщЧЯПЯЈЁБЅХЯµДРЕєЕґуРЎПаµИј«РФПа·ґЈ©ЙПРЕєЕµДІоЧчіцПмУ¦Ј¬µГµЅµДѕ»РЕєЕБЅ±¶УЪЈЁїЙ±ИµД»·ѕіФлЙщЈ©ИОТ»µҐ¶ЛРЕєЕЎЈТтґЛФЪЖдЛьМхјюµИН¬µДЗйїцПВЈ¬Іо·ЦРЕєЕУРЧЕёьґуµДРЕФл±Иј°РФДЬЎЈ Іо·ЦµзВ·¶ФПЯ¶ФРЕєЕЦ®јдµДµзО»ІоГфёРЎЈµ«КЗЈЁПа¶ФµШЈ©¶ФПЯЙПУлЖдЛьІОїјµзС№Па±ИЈЁМШ±рКЗµШЈ©µДѕш¶ФµзО»І»ГфёРЎЈТтґЛЈ¬Па¶Ф¶шСФЈ¬Іо·ЦµзВ·¶ФЦоИзµШµЇЎўЖдЛьґжФЪУЪµзФґєН/»тµШЖЅГжµДФлЙщРЕєЕТФј°їЙДЬіцПЦФЪГїТ»ёщЧЯПЯЦРПаµИµД№ІДЈРЕєЕХвСщµДОКМвІ»ГфёРЎЈ Іо·ЦРЕєЕ¶ФEMIєНґ®ИЕВФОўГвТЯЎЈИз№ыПЯ¶ФЧЯµГєЬЅьЈ¬ХвСщИОєОНвІїсоєПФлЙщЅ«ПаµИµШсоєПЅшПЯ¶ФЎЈХвСщТ»АґсоєПФлЙщѕН±діЙЎ°№ІДЈЎ±ФлЙщЈ¬¶шµзВ·¶ФґЛКЗЈЁАнВЫЙПЈ©ГвТЯµДЎЈИз№ыµјПЯКЗЎ°ІшИЖЎ±ЈЁ±ИИзЛ«ЅКПЯЈ©µДЈ¬ДЗГґ¶ФФлЙщµДГвТЯРФѕНёьєГЎЈТтОЄОТГЗІ»ДЬ·Ѕ±гµШЅ«УЎЦЖ°еЙПµДІо·ЦЧЯПЯІшИЖЖрАґЈ¬°СЛьГЗѕЎїЙДЬµШїїЅьЧЯПЯѕНКЗЧоєГµД°м·ЁБЛЎЈ Ѕф°¤ЧЕІјПЯµДІо·Ц¶Ф±ЛґЛЅфГЬсоєПЎЈХвЦЦ»ҐсојхЙЩБЛEMI·шЙдЈ¬МШ±рКЗУ뵥¶ЛЧЯПЯПа±ИЎЈДгїЙТФ°СХвёцИПОЄКЗГїёщЧЯПЯµД·шЙд±ЛґЛґуРЎПаµИЗТј«РФПа·ґЈ¬ХвСщ±ЛґЛµДКдіцѕНП໥µЦПыБЛЈ¬ѕНПсФЪЛ«ЅКПЯЦРТ»СщЈЎІо·ЦЧЯПЯ±ЛґЛФЅїїЅьЈ¬соєПФЅЗїЈ¬EMI·шЙдµДїЙДЬРФѕНФЅРЎЎЈ И±ПЭ Іо·ЦµзВ·µДЦчТЄИ±ПЭКЗЧЯПЯµДФцјУЎЈТтґЛЈ¬Из№ыДгµДУ¦УГЦРХвР©УЕµгГ»УРТ»ёцКЗМШ±рЦШТЄµДЈ¬ДЗГґѕНІ»ЦµµГОЄІо·ЦРЕєЕТФј°ёЅґшµДІјПЯїјВЗФцјУГж»эЎЈµ«КЗИз№ыХвР©УЕµгФЪДгµДµзВ·ЦРІъЙъБЛПФЦшµДРФДЬІоТмЈ¬ДЗГґФцјУµДІјПЯГж»эѕНКЗОТГЗё¶іцµДґъјЫЎЈ ЦШТЄЅбВЫ Іо·ЦПЯ±ЛґЛсоєПЎЈХвЦЦсоєПУ°ПмБЛЧЯПЯµД¶ФНвЧиї№Ј¬ТтґЛ¶ЛЅУ·Ѕ·Ё ЈЁ№ШУЪХвёцОКМвµДМЦВЫТФј°ИзєОјЖЛгІо·ЦЧиї№ЗлІОјыЅЕЧў2Ј©ЛщУГµДІо·ЦЧиї№µДјЖЛгКЗА§ДСµДЎЈФЪХвАп№ъјТ°лµјМеУРТ»Р©ІОїјЈ¬Polar InstrumentsМṩБЛТ»ёц¶АБўµДјЖЛгЖчЈЁКЗКХ·СµДЈ©їЙТФјЖЛгРн¶аІ»Н¬Ѕб№№ Іо·ЦЧЯПЯµДІо·ЦЧиї№ЎЈёЯ¶ЛЙијЖ№¤ѕЯ°ьТІДЬјЖЛгІо·ЦЧиї№ЎЈ µ«КЗЧўТвКЗсоєПЦ±ЅУУ°ПмБЛІо·ЦЧиї№µДјЖЛгЎЈІо·ЦЧЯПЯЦ®јдµДсоєП±ШРлФЪХыёцПЯі¤ДЪ±ЈіЦТ»ЦВ»тХЯЧиї№КЗБ¬РшµДЎЈХвѕНКЗЙијЖ№жФтЦРЎ°№М¶ЁјдѕаЎ±µДФТтЎЈ ±ај±КјЗЈє±ѕОДµДФЧчХЯОЄDouglas BrooksЈ¬УЙЛјїЖCAD№¤іМК¦ЗЗИс·ТлЎЈОДХВё±±кМвОЄЈєЙъґж·ЁФтЎЈ±ѕОДµµµДЦшЧчИ«№йКфФЧчХЯDouglas BrooksІ©Кїј°UltraCAD Design Inc.ЛщУРЎЈ ТлХЯЙщГчЈє·Тл±ѕОДµµґїКфРЛИ¤°®єГЈ¬Г»УРИОєОЙМТµДїµДЎЈ±ѕОДµµµДЦшЧчИ«№йКфФЧчХЯDouglas BrooksІ©Кїј°UltraCAD Design Inc.ЛщУРЎЈЧЄФШј°К№УГ±ѕОДµµЛщІъЙъµД·ЁВЙ·зПХУЙК№УГХЯЧФРРіРµЈЈ¬ЧчХЯІ»іРµЈИОєО·ЁВЙФрИОЎЈ ОТГЗНЁіЈИПОЄРЕєЕТФИэЦЦДЈКЅСШµзВ·ґ«ІҐЈєµҐ¶ЛЎўІоДЈ»т№ІДЈЎЈ µҐДЈКЗОТГЗЧоКмП¤µДЎЈЛь°ьАЁЅйУЪЗэ¶ЇЖчУлЅУКХЖчЦ®јдµДµҐёщµјПЯ»тЧЯПЯЎЈРЕєЕСШЧЯПЯґ«ІҐІўґУµШ·µ»Ш1ЎЈ ІоДЈ°ьАЁЅйУЪЗэ¶ЇЖчУлЅУКХЖчµДТ»¶ФЧЯПЯЈЁ»тµјПЯЈ©ЎЈОТГЗТ»°гИПОЄЖдЦРТ»ёщЧЯПЯґ«ЛНХэРЕєЕ¶шБнТ»ёщґ«ЛНёєРЕєЕЈ¬ІўЗТґуРЎПаµИј«РФПа·ґЈ¬Г»УРНЁ№эµШµД·µ»ШРЕєЕЈ»РЕєЕСШТ»ёщЧЯПЯЗ°ЅшІўґУБнНвТ»ёщ·µ»ШЎЈ №ІДЈРЕєЕНЁіЈёьДСУЪАнЅвЎЈјИїЙТФ°ьАЁµҐ¶ЛЧЯПЯТІїЙТФ°ьАЁБЅёцЈЁїЙДЬёь¶аЈ©Іо·ЦЧЯПЯЎЈН¬СщµДРЕєЕСШЧЯПЯТФј°·µ»ШВ·ѕ¶ЈЁµШЈ©»тХЯСШІо·Ц¶ФЦРµДБЅёщЧЯПЯБч¶ЇЎЈґуІї·ЦИЛНщНщ¶Ф№ІДЈРЕєЕІ»КмП¤Ј¬ТтОЄОТГЗЧФјєґУАґІ»»б№КТвІъЙъЛьГЗЎЈЛьГЗНЁіЈКЗУЙґУЖдЛьЈЁБЪЅь»тНвІїЈ©ФґсоєПЅшµзВ·µДФлЙщТэЖрµДЎЈТ»°гАґЅІЈ¬Ѕб№ыЧоєГЗйїцКЗЦРРФµДЈ¬Чо»µЗйїцКЗѕЯУРЖЖ»µРФµДЎЈ№ІДЈРЕєЕДЬ№»ІъЙъёЙИЕµзВ·ХэіЈФЛРРµДФлЙщЈ¬ІўЗТКЗіЈјыµДEMI ОКМвµДАґФґЎЈ УЕµг Іо·ЦРЕєЕПа±ИµҐ¶ЛРЕєЕУРТ»ёцПФЦшµДИ±µгЈєРиТЄБЅёщЧЯПЯ¶шІ»КЗТ»ёщЈ¬»тХЯБЅ±¶µДµзВ·°еГж»эЎЈµ«КЗІо·ЦРЕєЕУРјёёцУЕµгЈєИз№ыГ»УРНЁ№эµШµД·µ»ШРЕєЕЈ¬µШ»ШВ·µДБ¬РшРФПа¶ФѕН±дµГІ»ЦШТЄБЛЎЈТтґЛЈ¬јЩИзОТГЗУРТ»ёцДЈДвРЕєЕНЁ№эІо·Ц¶ФБ¬ЅУµЅКэЧЦЖчјюЈ¬ѕНОЮРиµЈРДїзФЅµзФґ±ЯЅзЈ¬ЖЅГжІ»Б¬РшµИµИОКМвЎЈІо·ЦЖчјюµДµзФґ·ЦёоТІёьИЭТЧґ¦Ан2ЎЈІо·ЦµзВ·ФЪµНС№РЕєЕµДУ¦УГЦРКЗ·ЗіЈУРТжµДЎЈИз№ыРЕєЕµзЖЅ·ЗіЈµНЈ¬»тХЯИз№ыРЕФл±ИКЗёцОКМвЈ¬ДЗГґІо·ЦРЕєЕїЙТФУРР§µШ±¶ФцРЕєЕµзЖЅЈЁ+v-(-v)=2vЈ©ЎЈІо·ЦРЕєЕєНІо·Ц·ЕґуЖчНЁіЈУГУЪРЕєЕµзЖЅ·ЗіЈµНµДПµНіµДКдИлј¶ЎЈ Іо·ЦЅУКХЖчНщНщ¶ФКдИлРЕєЕµзЖЅµДІоГфёРЈ¬µ«КЗіЈіЈ±»ЙијЖОЄ¶ФКдИлµД№ІДЈЖ«ТЖІ»ГфёРЎЈТтґЛФЪЗїФлЙщ»·ѕіЦРІо·ЦРЕєЕНщНщ±ИµҐ¶ЛРЕєЕУРЧЕёьєГµДРФДЬЎЈ Па±ИµҐ¶ЛРЕєЕЈЁТФТ»ёцІ»М«ѕ«И·µДКЬµзВ·°еЖдЛыО»ЦГµДФлЙщµДёЙИЕµДРЕєЕОЄІОїјЈ©Іо·ЦРЕєЕЈЁ±ЛґЛ»ҐОЄІОїјЈ©µД·ЧЄК±РтїЙТФёьѕ«И·µШЙи¶ЁЎЈІо·Ц¶ФµДЅ»Іжµг¶ЁТеµГ·ЗіЈѕ«И·ЈЁНј1Ј©ЎЈµҐ¶ЛРЕєЕО»УЪВЯј1 єНВЯј0 Ц®јдµДЅ»ІжµгКЬЦЖУЪЈЁѕЩАэЈ©ФлЙщЎўФлЙщГЕПЮТФј°ГЕПЮјмІвОКМвµИµИЎЈ  ЦШТЄјЩЙи Іо·ЦРЕєЕµДТ»ёцЦШТЄ·ЅГжіЈіЈ±»№¤іМК¦»тХЯЙијЖИЛФ±єцВФЈ¬ЙхЦБУРК±±»ОуЅвЎЈОТГЗґУБЅМх№гОЄИЛЦЄµД№жФтїЄКјЈєЈЁaЈ©µзБчФЪТ»ёц±ХєПµД»·В·ДЪБч¶ЇТФј°ЈЁbЈ©µзБчФЪ»·В·ДЪґ¦ґ¦ПаµИЎЈ їјВЗІо·Ц¶ФµДЎ°ХэЎ±ЧЯПЯЎЈµзБчСШЧЯПЯБч¶ЇІўЗТ±ШРлФЪТ»ёц»·В·ДЪБч¶ЇЈ¬НЁіЈґУµШ·µ»ШЎЈБнНвТ»ёщЧЯПЯЦРµДёєРЕєЕТІ±ШРлФЪТ»ёц»·В·ДЪБч¶ЇЈ¬НЁіЈТІґУµШ·µ»ШЎЈХвєЬИЭТЧГч°ЧИз№ыОТГЗФЭК±ПлПуТ»ёцІо·Ц¶ФЦРµДТ»ёщЧЯПЯЙПµДµзБч±ЈіЦІ»±дЎЈБнТ»ёщЧЯПЯЦРµДРЕєЕ±ШРлґУДіёцµШ·Ѕ·µ»ШІўЗТєЬЗеію·µ»ШВ·ѕ¶У¦ёГКЗµҐ¶ЛРЕєЕµД·µ»ШВ·ѕ¶ЈЁµШЈ©ЎЈОТГЗЛµІо·Ц¶ФГ»УРНЁ№эµШµД·µ»ШРЕєЕІ»КЗТтОЄІ»ДЬЈ¬¶шКЗТтОЄ·µ»ШРЕєЕµДИ·ґжФЪІўЗТґуРЎПаµИЗТј«РФПа·ґЛщТФП໥µЦПъБЛЈЁєНОЄБгЈ©ЎЈХвТ»µг·ЗіЈЦШТЄЎЈИз№ыґУТ»ёцРЕєЕЈЁ+iЈ©·µ»ШµДРЕєЕСПёсµИУЪЈ¬ЗТ·ыєЕПа·ґЈ¬БнТ»ёцРЕєЕЈЁ-iЈ©Ј¬ДЗГґЛьГЗµДєНЈЁ+i-iЈ©ОЄБгЈ¬Г»УРµзБчґУИОєОµШ·ЅБч№эЈЁМШ±рКЗµШЈ©ЎЈПЦФЪјЩ¶ЁРЕєЕІў·ЗСПёсПаµИЗТј«РФПа·ґЎЈЙиТ»ёцОЄ+i1 БнТ»ёцОЄ-i2ЎЈХвАпi1 єНi2 µДЦµЅьЛЖµ«КЗІ»µИЎЈ·µ»ШµзБчµДєНОЄ(i1-i2)ЎЈТтОЄІ»КЗБгЈ¬ХвёцФцјУµДµзБч±ШРлґУДіёцµШ·Ѕ·µ»ШЈ¬НЖІвУ¦ёГКЗµШЎЈ ДгЛµКІГґЈїДЗГґИГОТГЗјЩ¶Ё·ўЛНµзВ··ўЛНТ»¶ФІо·ЦРЕєЕЈ¬СПёсПаµИЗТј«РФПа·ґЎЈФЩјЩ¶ЁЛыГЗФЪВ·ѕ¶µДЦХµгИФИ»ИзґЛЎЈµ«КЗИз№ыВ·ѕ¶і¤¶ИІ»µИ»бИзєОДШЈїИз№ыЈЁІо·Ц¶ФЦРµДЈ©Т»МхВ·ѕ¶±ИБнНвТ»Мхі¤Ј¬ДЗГґРЕєЕФЪґ«КдµЅЅУКХЖчµДЅЧ¶ОѕНІ»ФЩКЗСПёсПаµИЗТј«РФПа·ґБЛЈЁНј2Ј©ЎЈИз№ыРЕєЕФЪЛьГЗґУТ»ёцЧґМ¬µЅБнТ»ёцЧґМ¬µДЧЄ±д№эіМЦРІ»ФЩКЗСПёсПаµИЗТПа·ґЈ¬Г»УРµзБчБчѕµШѕНІ»ФЩКЗХэИ·µДБЛЎЈИз№ыУРБчѕµШµДµзБчґжФЪЈ¬ДЗГґµзФґНкХыРФѕНТ»¶ЁіЙОЄТ»ёцОКМвЈ¬ІўЗТїЙДЬEMIТІ»біЙОЄТ»ёцОКМвЎЈ  ЙијЖ№жФт1 ОТГЗґ¦АнІо·ЦРЕєЕµДµЪТ»ёц№жФтКЗЈєЧЯПЯ±ШРлµИі¤ЎЈУРИЛј¤БТµШ·ґ¶ФХвМх№жФтЎЈНЁіЈЛыГЗµДХщВЫµД»щґЎ°ьАЁБЛРЕєЕК±РтЎЈЛыГЗПкѕЎµШЦёіцРн¶аІо·ЦµзВ·їЙТФИЭИМІо·ЦРЕєЕБЅёцІї·ЦПаµ±µДК±РтЖ«Іо¶шИФИ»ДЬ№»їЙїїµШЅшРР·ЧЄЎЈёщѕЭК№УГµДІ»Н¬µДВЯјГЕПµБРЈ¬їЙТФИЭИМ500 mil µДЧЯПЯі¤¶ИЖ«ІоЎЈІўЗТХвР©ИЛГЗДЬ№»Ѕ«ХвР©ЗйїцУГЖчјю№ж·¶єНРЕєЕК±РтНј·ЗіЈПкѕЎµШГи»жіцАґЎЈОКМвКЗЈ¬ЛыГЗГ»УРЧҐЧЎТЄµгЈЎІо·ЦЧЯПЯ±ШРлµИі¤µДФТтУлРЕєЕК±РтјёєхГ»УРИОєО№ШПµЎЈУлЦ®Па№ШµДЅцЅцКЗјЩ¶ЁІо·ЦРЕєЕКЗґуРЎПаµИЗТј«РФПа·ґµДТФј°Из№ыХвёцјЩЙиІ»іЙБўЅ«»б·ўЙъКІГґЎЈЅ«»б·ўЙъµДКЗЈєІ»КЬїШµДµШµзБчїЄКјБч¶ЇЈ¬ЧоєГЗйїцКЗБјРФµДЈ¬Чо»µЗйїцЅ«µјЦВСПЦШµД№ІДЈEMIОКМвЎЈ ТтґЛЈ¬Из№ыДгТААµХвСщµДјЩ¶ЁЈ¬јґЈєІо·ЦРЕєЕКЗґуРЎПаµИЗТј«РФПа·ґЈ¬ІўЗТТтґЛГ»УРНЁ№эµШµДµзБчЈ¬ДЗГґХвёцјЩ¶ЁµДТ»ёц±ШТЄНЖВЫѕНКЗІо·ЦРЕєЕ¶ФµДі¤¶И±ШРлПаµИЎЈІо·ЦРЕєЕУл»·В·Гж»эЈєИз№ыОТГЗµДІо·ЦµзВ·ґ¦АнµДРЕєЕУРЧЕЅПВэµДЙПЙэК±јдЈ¬ёЯЛЩЙијЖ№жФтІ»КЗОКМвЎЈµ«КЗЈ¬јЩЙиОТГЗХэФЪґ¦АнµДРЕєЕУРЧЕУРЅПїмµДЙПЙэК±јдЈ¬КІГґСщµД¶оНвµДОКМвїЄКјФЪІо·ЦПЯЙП·ўЙъДШЈїїјВЗТ»ёцЙијЖЈ¬Т»¶ФІо·ЦПЯґУЗэ¶ЇЖчµЅЅУКХЖчЈ¬їзФЅТ»ёцЖЅГжЎЈН¬К±јЩЙиЧЯПЯі¤¶ИНкИ«ПаµИЈ¬РЕєЕСПёсґуРЎПаµИЗТј«РФПа·ґЎЈТтґЛЈ¬Г»УРНЁ№эµШµД·µ»ШµзБчЎЈµ«КЗЈ¬ѕЎ№ЬИзґЛЈ¬ЖЅГжІгЙПґжФЪТ»ёцёРУ¦µзБчЈЎ ИОєОёЯЛЩРЕєЕ¶јДЬ№»ЈЁІўЗТТ»¶Ё»бЈ©ФЪПаБЪµзВ·ЈЁ»тХЯЖЅГжЈ©ІъЙъТ»ёцсоєПРЕєЕЎЈХвЦЦ»ъЦЖУлґ®ИЕµД»ъЦЖНкИ«ПаН¬ЎЈХвКЗУЙµзґЕсоєПЈ¬»ҐёРсоєПУ뻥ИЭсоєПµДЧЫєПР§№ыЈ¬ТэЖрµДЎЈТтґЛЈ¬ИзН¬µҐ¶ЛРЕєЕµД·µ»ШµзБчЗгПтУЪФЪЦ±ЅУО»УЪЧЯПЯПВ·ЅµДЖЅГжЙПґ«ІҐЈ¬Іо·ЦПЯТІ»бФЪЖдПВ·ЅµДЖЅГжЙПІъЙъТ»ёцёРУ¦µзБчЎЈ µ«ХвІ»КЗ·µ»ШµзБчЎЈЛщУРµД·µ»ШµзБчТСѕµЦПыБЛЎЈТтґЛЈ¬ХвґїґвКЗЖЅГжЙПµДсоєПФлЙщЎЈОКМвКЗЈ¬Из№ыµзБч±ШРлФЪТ»ёц»·В·ЦРБч¶ЇЈ¬КЈПВАґµДµзБчµЅДДАпИҐБЛДШЈїјЗЧЎЈ¬ОТГЗУРБЅёщЧЯПЯЈ¬ЖдРЕєЕґуРЎПаµИј«РФПа·ґЎЈЖдЦРТ»ёщЧЯПЯФЪЖЅГжТ»ёц·ЅПтЙПсоєПБЛТ»ёцРЕєЕЈ¬БнТ»ёщФЪЖЅГжБнТ»ёц·ЅПтЙПсоєПБЛТ»ёцРЕєЕЎЈЖЅГжЙПХвБЅёцсоєПµзБчґуРЎПаµИЈЁјЩЙиЖдЛь·ЅГжЙијЖµГєЬєГЈ©ЎЈТтґЛµзБчНкИ«ФЪІо·ЦЧЯПЯПВ·ЅµДТ»ёц»·В·ЦРБч¶ЇЈЁНј3Ј©ЎЈЛьГЗїґЙПИҐѕНПсКЗОРБчЎЈсоєПµзБчФЪЖдЦРБч¶ЇµД»·В·УЙЈЁaЈ©Іо·ЦПЯЧФЙнєНЈЁbЈ©ЧЯПЯФЪГїёц¶ЛµгЦ®јдµДјдёфАґ¶ЁТеЎЈ  ЙијЖ№жФт2 ПЦФЪEMI Ул»·В·Гж»эТСКЗ№гОЄИЛЦЄБЛ3ЎЈТтґЛИз№ыОТГЗПлїШЦЖEMIЈ¬ѕНРиТЄЅ«»·В·Гж»эЧоРЎ»ЇЎЈІўЗТЧцµЅХвТ»µгµД·Ѕ·ЁТэіцБЛОТГЗµДµЪ¶юМхЙијЖ№жФтЈєЅ«Іо·ЦПЯ±ЛґЛїїЅьІјПЯЎЈУРИЛ·ґ¶ФХвМх№жФтЈ¬КВКµЙПХвМх№жФтФЪЙПЙэК±јдЅПВэІўЗТEMI І»КЗОКМвК±ІўІ»КЗ±ШРлµДЎЈµ«КЗФЪёЯЛЩ»·ѕіЦРЈ¬Іо·ЦПЯ±ЛґЛїїµГФЅЅьІјПЯЈ¬ЧЯПЯПВ·ЅЛщёРУ¦µДµзБчµД»·В·ѕНФЅРЎЈ¬EMI ТІїЙТФµГµЅёьєГµДїШЦЖЎЈ ЦµµГТ»МбµДКЗТ»Р©№¤іМК¦ТЄЗуЙијЖИЛФ±ИҐµфІо·ЦПЯПВ·ЅµДЖЅГжЎЈФТтЦ®Т»КЗјхРЎ»тПыіэЧЯПЯПВ·ЅµДёРУ¦µзБч»·В·ЎЈБнНвТ»ёцФТтКЗ·АЦ№ЖЅГжЙПТСУРµДФлЙщсоєПµЅЈЁНЖІвИзґЛЈ©ЧЯПЯЙПµДµНС№РЕєЕ4ЎЈ »№УРТ»ёцЅ«Іо·ЦПЯ±ЛґЛїїЅьІјПЯµДАнУЙЎЈІо·ЦЅУКХЖчЙијЖОЄ¶ФКдИлРЕєЕµДІоГфёР¶ш¶ФКдИлµД№ІДЈЖ«ТЖІ»ГфёРЎЈТІѕНКЗЛµјґК№ЈЁ+Ј©КдИлПа¶ФЈЁ-Ј©КдИлЅцУРЗбОўµДЖ«ТЖЈ¬ЅУКХЖчТІ»бјмІвµЅЎЈµ«КЗИз№ыЈЁ+Ј©єНЈЁ-Ј©КдИлТ»ЖрЖ«ТЖЈЁФЪН¬СщµД·ЅПтЈ©Ј¬Па¶Ф¶шСФЅУКХЖч¶ФХвЦЦЖ«ТЖІ»ГфёРЎЈТтґЛИз№ыИОєОНвІїФлЙщЈЁ±ИИзEMI »тґ®ИЕЈ©µИН¬µШсоєПµЅІо·ЦПЯЦРЈ¬ЅУКХЖчЅ«¶ФґЛЦЦЈЁ№ІДЈсоєПЈ©ФлЙщІ»ГфёРЎЈІо·ЦПЯІјµГФЅ±ЛґЛїїЅьЈ¬ИОєОЕјєПФлЙщФЪГїёщЧЯПЯЙПѕНФЅПаЅьЎЈТтґЛµзВ·µДФлЙщТЦЦЖѕНФЅєГЎЈ №жФт2НЖВЫ ФЩґОјЩ¶ЁёЯЛЩ»·ѕіЦРЈ¬Из№ыІо·ЦПЯ±ЛґЛЅф°¤ЧЕІјПЯЈЁОЄБЛК№ЖдПВ·ЅµД»·В·Гж»эЧоРЎ»ЇЈ©ДЗГґЧЯПЯЅ«±ЛґЛсоєПЎЈИз№ыЧЯПЯЧг№»і¤ТФЦБУЪ¶ЛЅУіЙОЄТ»ёцОКМвЈ¬ХвЦЦсоєПѕН»бУ°ПмµЅИ·ЗРµД¶ЛЅУЧиї№5µДјЖЛгЎЈФТтКЗЈєїјВЗТ»ёцІо·ЦПЯ¶ФЈ¬ПЯ1 єНПЯ2ЎЈјЩК№ЛьГЗ·Ц±рРЇґшРЕєЕV1 єНV2ЎЈТтОЄЛьГЗКЗІо·ЦПЯЈ¬V2=V1*V1 ФЪПЯ1 ТэЖрТ»ёцµзБчI1 ¶шV2ФЪПЯ2 ТэЖрТ»ёцµзБчI2ЎЈµзБч±ШИ»КЗґУЕ·Д·¶ЁВЙµјіцЈ¬I=V/Z0Ј¬ХвАпZ0 КЗЧЯПЯµДМШХчЧиї№ЎЈПЦФЪПЯ1ЈЁѕЩАэЈ©РЇґшµДµзБчКВКµЙПУЙi1 єНk*i2 ЧйіЙЈ¬ХвАпk КЗПЯ1 УлПЯ2 јдµДсоєП±ИАэЎЈХв±нГчХвЦЦсоєПµДЧоЦХР§№ыКЗПЯ1 ЙПµДТ»ёцГчПФµДЧиї№Ј¬ХвёцЧиї№µИУЪZ=Z0-Z12ХвАпZ12 УЙПЯ1 УлПЯ2 јдµД»Ґсо6ТэЖрЎЈИз№ыПЯ1 єНПЯ2 ·ЦµГєЬїЄЈ¬ЛьГЗЦ®јдµДсоєПѕНєЬРЎЈ¬И·ЗРµД¶ЛЅУЧиї№ѕНЦ»КЗZ0Ј¬µҐ¶ЛЧЯПЯµДМШХчЧиї№ЎЈµ«КЗИз№ыЧЯПЯїїµДёьЅьЈ¬ЛьГЗЦ®јдµДсоєПѕН»бФцјУЈ¬ХвСщЧЯПЯµДЧиї№УлХвЦЦсоєПіЙ±ИАэµШјхРЎЎЈХвѕНКЗЛµИ·ЗРµДЧЯПЯ¶ЛЅУЈЁОЄБЛ·АЦ№·ґЙдЈ©ОЄZ0-Z12Ј¬»тХЯДіёцРЎУЪZ0 µДЦµЎЈХв¶ФІо·Ц¶ФµДБЅёщЧЯПЯ¶јККУГЎЈТтОЄГ»УРБчѕµШµДµзБчЈЁґуёЕХвКЗёцјЩЙиЈ©ДЗГґ¶ЛЅУµзЧи±»Б¬ЅУФЪПЯ1 єНПЯ2 Ц®јдЈ¬ЗТИ·ЗРµД¶ЛЅУЧиї№ЛгµГКЗ2(Z0-Z12)ЎЈХвёцЦµѕіЈ±»ЅРЧцЎ°Іо·ЦЧиї№Ў±7ЎЈ ЙијЖ№жФт3 Іо·ЦЧиї№Тт»Ґсо¶ш±дЈ¬¶ш»ҐсоТтПЯѕа¶ш±дЎЈТтґЛФЪИОєОЗйїцПВЈ¬ЧЯПЯЧиї№Ј¬ТІѕНКЗ»ҐсоЈ¬ФЪИ«ПЯОЄіЈКэКЗєЬЦШТЄµДЎЈХвѕНµГµЅБЛОТГЗµДµЪИэёц№жФтЈєЈЁІо·Ц¶ФµДЈ©ПЯѕа±ШРлФЪИ«ПЯОЄіЈКэЎЈ ЧўТв¶ФІо·ЦЧиї№µДУ°ПмЦ»КЗ№жФт2 µДНЖВЫЎЈІо·ЦЧиї№ёщ±ѕІ»КЗУлЙъѕгАґµДЎЈОТГЗТЄ°СІо·ЦПЯ±ЛґЛїїЅьІјПЯУлEMI єНФлЙщГвТЯУР№ШЎЈЛь¶ФЎ°і¤Ў±ПЯИ·ЗР¶ЛЅУТФј°ПЯѕаТ»ЦВРФµДУ°ПмµДКВКµЦ»І»№эКЗОЄБЛEMI їШЦЖ¶шЅ«ЧЯПЯ±ЛґЛїїЅьІјПЯµДТ»ёцНЖВЫ8ЎЈ ЅбВЫ Іо·ЦРЕєЕУРјёёцУЕµгЈ¬ЛьГЗЦРµДИэёцКЗЈЁaЈ©УлµзФґПµНіУРР§ёфАлЈ¬ЈЁbЈ©¶ФФлЙщГвТЯЈ¬єНЈЁcЈ©ФцЗїРЕФл±ИЎЈУлµзФґПµНіЈЁМШ±рКЗПµНіµШЈ©ёфАлТААµУЪІо·ЦПЯЙПµДРЕєЕХжХэµШґуРЎПаµИЗТј«РФПа·ґЎЈХвёцјЩ¶ЁТІРнІ»іЙБўЈ¬Из№ыІо·Ц¶ФЦРµҐёцПЯі¤І»НкИ«ЖҐЕдЎЈ¶ФФлЙщµДГвТЯѕіЈТААµУЪЧЯПЯµДЅфсоєПЎЈХвЅ«ТАґОУ°ПмµЅОЄ·АЦ№·ґЙд¶ш¶ФЧЯПЯЅшРРХэИ·µД¶ЛЅУµДЦµЈ¬ТФј°Из№ыЧЯПЯ±ШРлЅфсоєПЈ¬НЁіЈТІКЗРиТЄµДЈ¬ЛьГЗµДјдѕа±ШРлИ«ПЯОЄіЈКэЎЈ |

НшУСЖАВЫ